# PAM4 System Simulation using AMI models

Fangyi RAO

Asian IBIS Summit Taipei, Taiwan November 13, 2015

Presented by Ming-Chih LIN

- Overview of PAM4

- Challenges in PAM-4 Link Designs

- Solutions for Simulating PAM-4 Links with IBIS-AMI Models

# Enabling the next step in link data rate

- 56 Gb/s lane data rate will be the principle enabler for 400GbE

- Two contenders for implementing 56Gb/s lane data rate:

- 56G NRZ

- + No new science linear evolution from 25/28G lanes

- Difficult to manage channel loss & channel reflections

- 28 Gbaud PAM-4

- + Channel loss problems worked out with 28 Gb/s NRZ

- 30% chip real estate, 35+% more power

- Lose 9.6 dB usable SNR

- Lots of new challenges little experience to draw from

- Both signaling technologies will be utilized to enable 400GbE

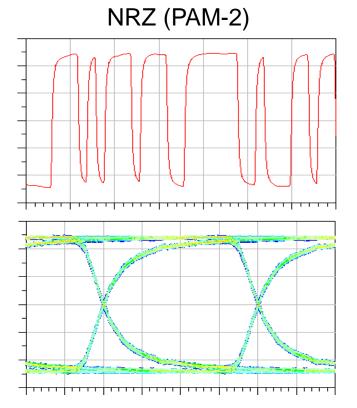

### NRZ (Non-Return-to-Zero) vs. PAM (Pulse Amplitude Modulation)

- 2 amplitude levels

- 1 bit of information in every symbol

- 56 Gbaud for 56 Gb/s

- 4 amplitude levels

- 2 bits of information in every symbol

- ✓ 2x throughput for the same Baud rate

- ✓ 28 Gbaud for 56 Gb/s, half of the loss in dB

- Lower SNR, more susceptible to jitter & noise

- More complex TX/RX design, higher cost

# Moving from NRZ to PAM-4

Revolutionary – not Evolutionary

- Jump from 10G NRZ to 25G introduced many new concepts....

- · Still a linear transition (more or less)

- Multi-Level signaling changes all the rules in place for 50+ years!

- Saturating to linear output stages

- · More complex (and precise) level threshold detection for inputs

- Finite rise time creates inherent ISI

- How to implement clock recovery?

- How will DFE need to change?

- ....

- ....

- Overview of PAM4

- Challenges in PAM-4 Link Designs

- Solutions for Simulating PAM-4 Links with IBIS-AMI Models

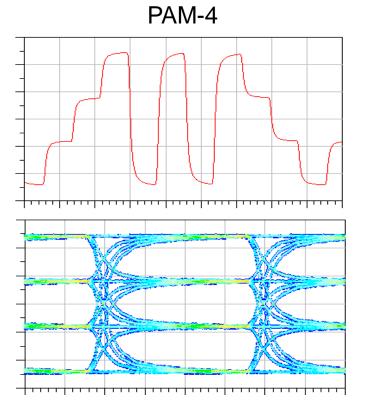

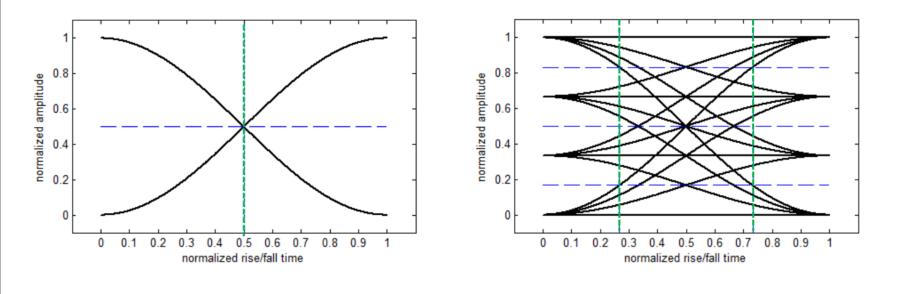

### Implementing PAM-4 links = "New Science"

Inherent ISI requires receivers to be less susceptible to pattern dependent jitter

----- decision threshold Amount of switching jitter

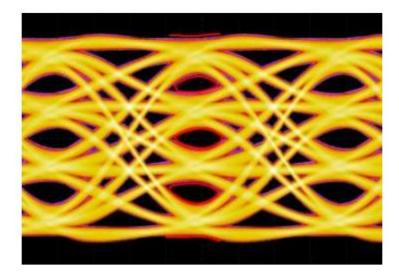

# Implementing PAM-4 links = "New Science" (2)

- Some of the other challenges learned so far include...

- Eye time skew from linear drive of VCSELs

- Upper eyes arrive sooner than lower transitions

- · Each eye needs to be sampled with independent delay

# Challenges shifting from NRZ to PAM

PAM-4 is one of the enablers of 56 G lane rate supporting 400G links

Multi-level signaling changes all the rules that have in place for 50+ years!

Saturating to linear output stages

More complex (and precise) level threshold detection for inputs

Finite rise time creates inherent ISI

How to implement clock recovery?

How will DFE need to change?

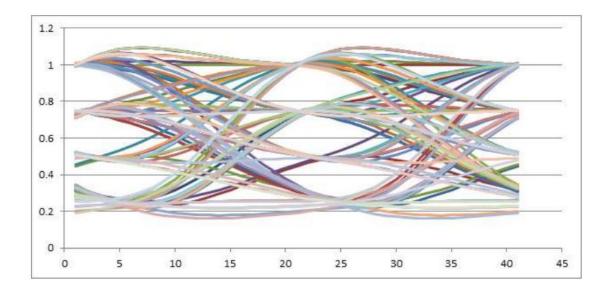

# Other impairments that challenge PAM-4 receivers

- · Non-linearity Amplitude compression in lower eyes

- Non uniform effective SNR across individual eyes

- Receivers sensitive to additional artifacts beyond "traditional" jitter types in NRZ

- Still learning what impairments cause problems

- New measurements <u>WILL</u> be defined for Tx Outputs

- New stress types <u>WILL</u> be defined for Rx Input testing

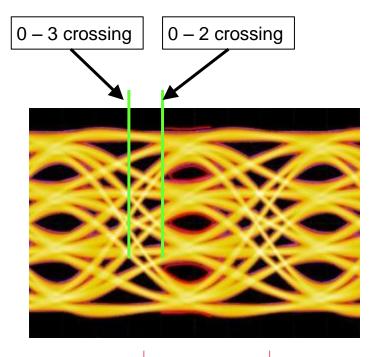

# Challenges in PAM-4 SerDes Design

- Nonlinearity between levels due to saturation

- CDR

- Upper and lower eye slicer reference level tuning

- Timing skews between three slicers for optimal sampling

- Analog based architecture vs ADC based architecture

# **Challenges in PAM-4 Link Simulation**

- How to capture PAM-4 SerDes behaviors

- How to measure PAM-4 eyes (three stacking eyes vs single eye in NRZ)

- Overview of PAM4

- Challenges in PAM-4 Link Designs

- Solutions for Simulating PAM-4 Links with IBIS-AMI Models

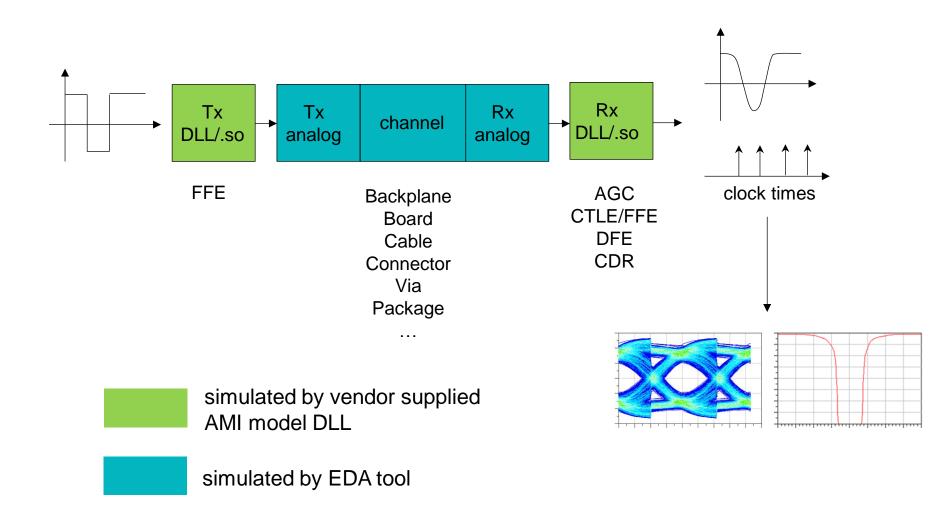

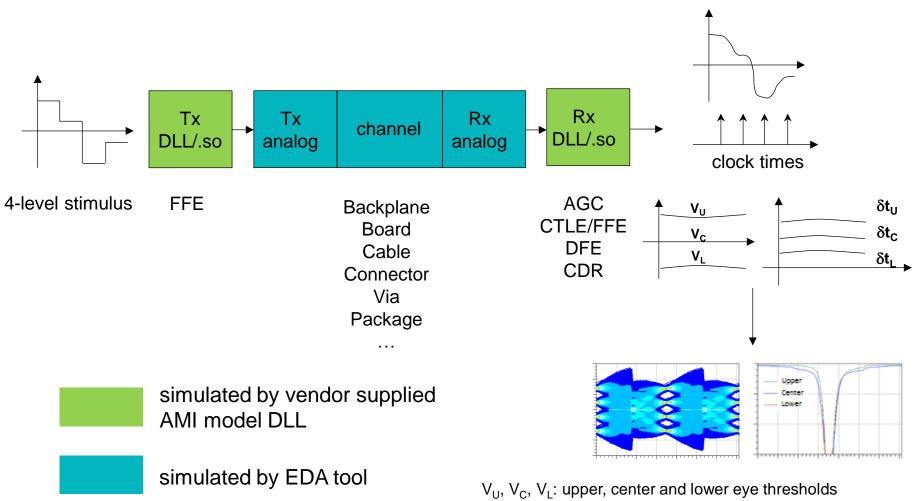

### AMI Simulation Flow for NRZ

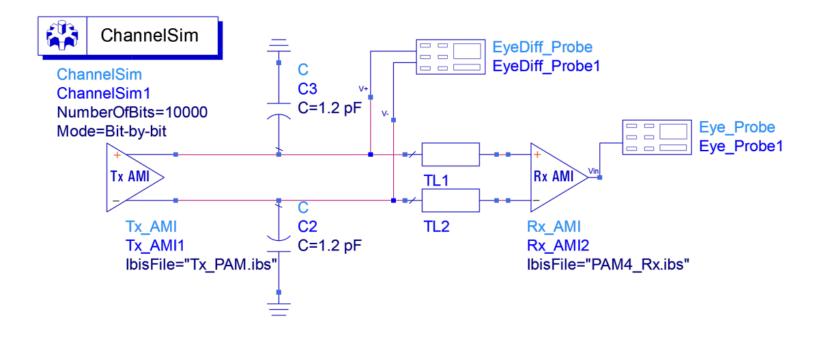

### **IBIS-AMI Based PAM-4 Link Simulation**

- AMI successfully brings SerDes vendors' models and EDA tools together

- Interoperability: AMI defines a common interface between SerDes model and channel simulator

- IP protection: SerDes behavior is concealed in model DLL/shared object

- Superior simulation speed

- AMI has been widely adopted by IC, system and EDA companies

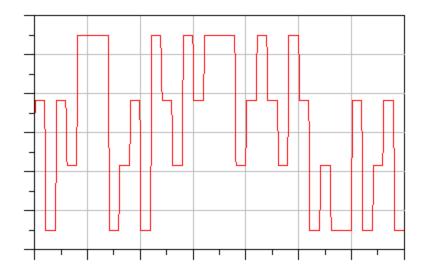

# AMI Modeling for PAM4 Signaling: Tx

- For NRZ, input stimulus to Tx DLL has two levels (0.5 and -0.5V), representing 1 and 0 bits

- For PAM4, input to Tx DLL has four levels (0.5, 0.5/3, -0.5/3 and -0.5V), representing symbols 0, 1, 2 and 3

- Tx DLL/.so interface is unchanged for PAM4

### **Tx AMI Reserved Parameters**

#### Modulation

- String. Allowed values are "NRZ" and "PAM4"

- Optional. Default is "NRZ"

#### PAM4\_Mapping

- String of four non-repeated integers 0, 1, 2 and 3 (e.g. "0123")

- Bit pairs 00, 01, 10 and 11 map to symbol levels specified by 1<sup>st</sup>, 2<sup>nd</sup>, 3<sup>rd</sup> and 4<sup>th</sup> integers, respectively

- Optional. Default is "0132" (Gray coding)

# AMI Modeling for PAM4 Signaling: Rx

- PAM4 Rx symbol decision relies on three slicers

- Slicer thresholds can be adjusted adaptively and can vary with time

- Sampling time skew can be applied independently to each slicer for optimal result and can vary with time

- Rx model should provide transient slicer threshold and timing skew information

### **Rx AMI Reserved Parameters**

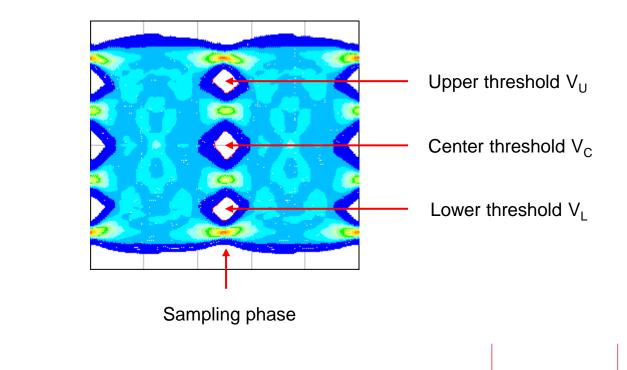

#### PAM4\_UpperThreshold, PAM4\_CenterThreshold, PAM4\_LowerThreshold

- Float. Upper, center and lower slicer thresholds

- Optional. If not provided by models, EDA tools have to guess their values for SER calculations

#### PAM4\_UpperEyeOffset, PAM4\_CenterEyeOffset, PAM4\_LowerEyeOffset

- Float. Upper, center and lower slicer sample time offsets relative to clock times

- Optional. Default is 0

Rx model can update values of these parameters in AMI\_Init and AMI\_GetWave and return them through the AMI\_parameters\_out string argument

### AMI Simulation Flow for PAM4

$\delta t_{U}$ ,  $\delta t_{C}$ ,  $\delta t_{L}$ : upper, center and lower eye sample time offsets

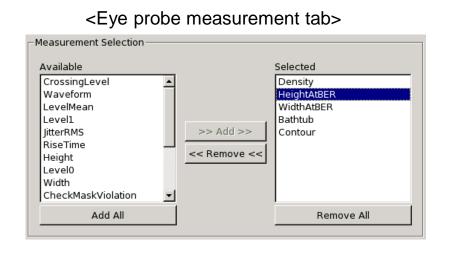

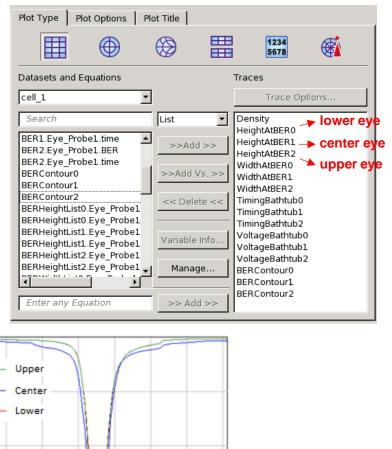

# Symbol Error Rate (SER) Measurement

- Measure bathtubs and SER contours individually for each of the three stacking eyes

- Horizontal eye center is placed at clock time + offset to capture CDR behavior and skew

- Vertical eye center is placed at threshold  $V_U / V_C / V_L$  to capture slicer level fluctuation

|            | Logic high<br>traces | Logic low<br>traces |

|------------|----------------------|---------------------|

| Upper eye  | $v_3(t) - V_U(t)$    | $v_2(t) - V_U(t)$   |

| Center eye | $v_2(t) - V_C(t)$    | $v_1(t) - V_C(t)$   |

| Lower eye  | $v_1(t) - V_L(t)$    | $v_0(t) - V_L(t)$   |

( $v_0$ ,  $v_1$ ,  $v_2$  and  $v_3$  are waveforms of expected 0, 1, 2 and 3 symbols, respectively)

# SER Measurements in Eye Probe

A set of bathtub, contour, HeightAtBER and WidthAtBER are calculated individually for each of the three eyes if selected

<SER>

35

time.psec

<Dataset>

33

34

0.15

0.10-

0.05-

0.00

-0.05

-0.10

-0.15

0.00

10.00

20.00

30,00

40.00

time, psec

50.00

60.00

70.00

38

37

36

### PAM4 System Simulation using AMI models

### PAM4 System Simulation using AMI models

Tx Output Rx Output 0.6 0.6 ADS ADS 0.4 0.4 EyeDiff\_Probe1.Density Eye\_Probe1.Density 0.2 0.2 0.0 0.0 -0.2 -0.2 -0.4 -0.4 -0.6 -0.6 0 20 40 60 80 100 120 140 160 Ó 20 40 60 80 100 120 140 160 time, psec time, psec 0.500 0.500 ADS ADS 0.375 0.375 EyeDiff\_Probe1.Waveform Eye Probe1.Waveform 0.250-0.250 0.125-0.125 0.000 0.000 -0.125 -0.125--0.250 -0.250 -0.375 -0.375 -0.500 -0.500 1.002 1.002 1.004 1.008 1.000 1.004 1.006 1.008 1.010 1.000 1.006 1.010 time, usec time, usec

KEYSIGHT TECHNOLOGIES

# Thank you