#### WELCOME FROM MIKE LABONTE, IBIS OPEN FORUM

#### Ladies and Gentlemen,

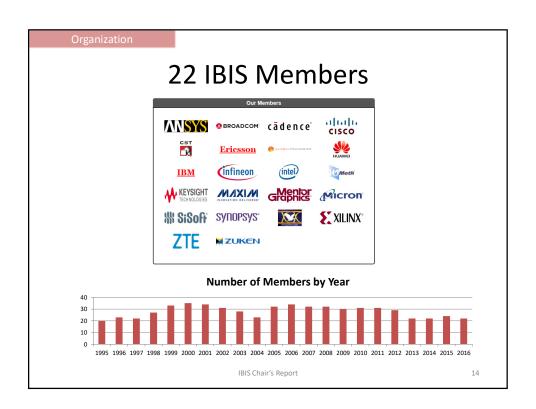

As chair of the IBIS Open Forum it is my pleasure to welcome you to the 2016 Asian IBIS Summit in Shanghai, and to thank you for your presentations and participation. We are grateful to our sponsors Huawei Technologies, Cadence Design Systems, IO Methodology, SPISim, Synopsys, Teledyne LeCroy, Xpeedic Technology, and ZTE Corporation for making this event possible.

Since 1993 IBIS has provided the digital electronics industry with specifications to make signal, timing, and power integrity analyses much easier and faster. The challenges keep changing and the IBIS community keeps responding with new enhancements to the IBIS family of specifications, which the IC vendors, EDA tool companies, and system designers adopt readily.

Support for IBIS in Asia has been strong, and we are pleased to see the formation of an IBIS China Regional Forum. The IBIS Open Forum looks forward to continued innovation and contributions from technology companies around the world. Thank you!

Mike LaBonte

Signal Integrity Software (SiSoft)

Chair, IBIS Open Forum

Medral R List

#### WELCOME FROM MIKE LABONTE, IBIS OPEN FORUM

女士们,先生们,

作为 IBIS 开放论坛的主席我很高兴地欢迎大家来到 2015 年亚洲 IBIS 上海峰会,并感谢您的演讲和参与。我们特别要感谢我们的赞助商华为技术,Cadence Design Systems,IO Methodology Inc,SPISim,Synopsys,Teledyne LeCroy,Xpeedic Technology 和中兴通讯,是他们使本次活动成为可能。

从 1993 年至今,IBIS 为高速数字电路设计的信号,时序和功率完整性分析方面提供了更加容易和快捷电子模型行业规范。为适应不断变化的挑战,在 IC 供应商, EDA 工具公司和系统设计师的共同努力下, IBIS 正在继续不断加入新的功能和完善已有的 IBIS 系列规范。

在亚洲,IBIS 受到了更广泛的支持。 在这里我也要向大家宣布 IBIS 中国分会的正式成立,对此,IBIS 开放论坛期待着有更多的技术公司的参与和更多的技术创新和贡献。

谢谢!

Mike LaBonte (迈克 拉邦地)

Mahal R Latino

SiSoft 公司

主席, IBIS 开放论坛

#### WELCOME FROM LIU SHUYAO, HUAWEI TECHNOLOGIES

Ladies and Gentlemen,

On behalf of Huawei Technologies, welcome to the 12th annual Asian IBIS Summit (China). I would like to express my appreciation to IBIS Open Forum and all the sponsors for coorganizing this event.

Since 2005, IBIS Asian Summit in China has been the top-level international conference in high speed digital design society in China. I am looking forward to work with IBIS members in China, and to expand our participations in the region.

Huawei has actively involved in all IBIS society's events. We hope to resolve high speed link issues with IBIS Open Forum, EDA vendors and IC vendors. Your comments and suggestions will be deeply appreciated!

Welcome all of you to Shanghai! Hope you will enjoy all the technical discussions and sharing throughout the meeting, and have a nice journey!

Thank you! Shuyao Liu Huawei Technologies

各位专家,各位来宾:

我代表华为公司,欢迎大家来参加第 12 届亚洲 IBIS 技术研讨会,衷心地感谢 IBIS 协会组织本次会议。

自从 2005 年以来,IBIS 技术研讨会已经成为了中国高速设计领域的一次盛会。我很高兴有机会与 IBIS 协会一起促进和扩大在该领域的分享。

华为积极参与各项 IBIS 活动,希望与 IBIS 协会、EDA 软件、芯片公司一道来共同解决许 多高速链路设计上的挑战,欢迎大家会上讨论和建议。

欢迎 IBIS 专家来到上海,希望你们能够喜欢所有的技术讨论和会议分享,度过美好一天。

谢谢大家 华为公司 柳树要

#### **AGENDA AND ORDER OF THE PRESENTATIONS**

#### (The actual agenda might be modified)

|       | IBIS SUMMIT MEETING AGENDA                                                                                                                           |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15  | SIGN IN - Vendor Tables Open at 8:30                                                                                                                 |

| 8:45  | <pre>WELCOME - Liu, Shuyao   (Huawei Technologies, China) - LaBonte, Mike (Chair, IBIS Open Forum)   (Signal Integrity Software (SiSoft), USA)</pre> |

| 9:00  | IBIS Chair's Report                                                                                                                                  |

| 9:25  | IBIS Model Simulation with RLC_dut                                                                                                                   |

| 9:55  | Case Study: Modeling IBIS for Open_drain True Differential 22 Pair Buffer Wang*, Lance; Liang**, Yan (*IO Methodology; **Maxim Integrated, USA)      |

| 10:20 | BREAK (Refreshments and Vendor Tables)                                                                                                               |

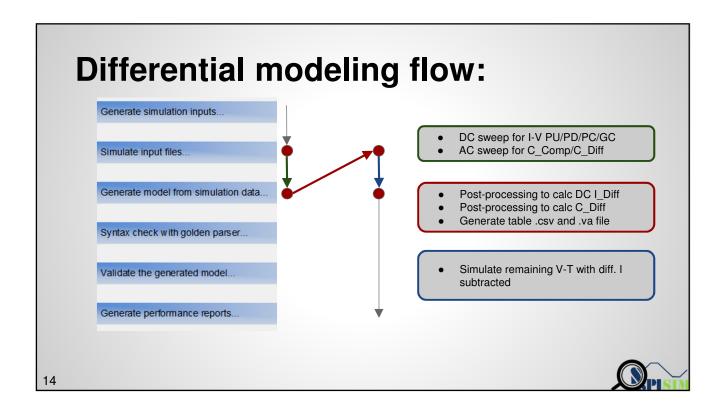

| 10:40 | Differential Modeling Flow with Series Model in Verilog-A 30 Huang*, Wei-hsing; Gupta**, Sanjeev (*SPISim, USA; **Sigintegrity Solutions, India)     |

| 11:10 | IBIS-AMI Model Generation with Quality                                                                                                               |

| 12:00 | FREE BUFFET LUNCH (Hosted by Sponsors) - Vendor Tables                                                                                               |

#### AGENDA AND ORDER OF THE PRESENTATIONS (Continued)

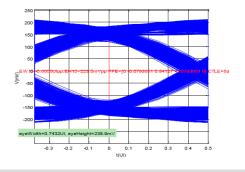

| 13:30 | Suggestion on Issuing VSR/CAUI-4 Based on IBIS-AMI Model 59 Xu, Zhengrong (Huawei Technologies, China)                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:50 | Necessity for Integrating FEC Functionality for PAM4 in 64 IBIS-AMI Model  Dong*, Xiaoqing; Huang**, Nick (*Huawei Technologies; **Shenzhen Zhongzeling Elecronics, China) |

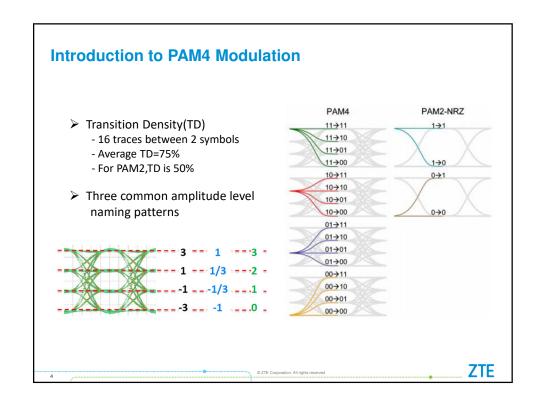

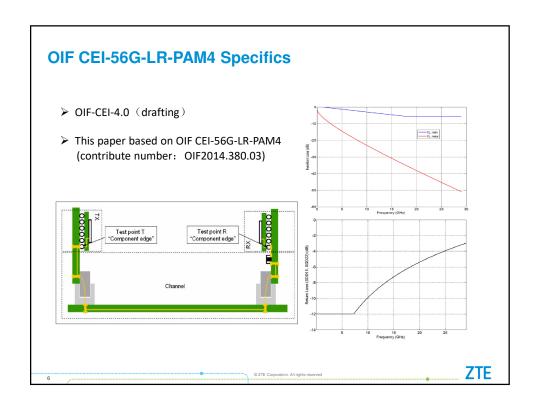

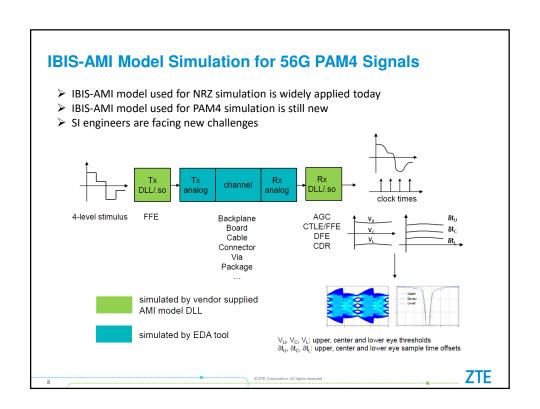

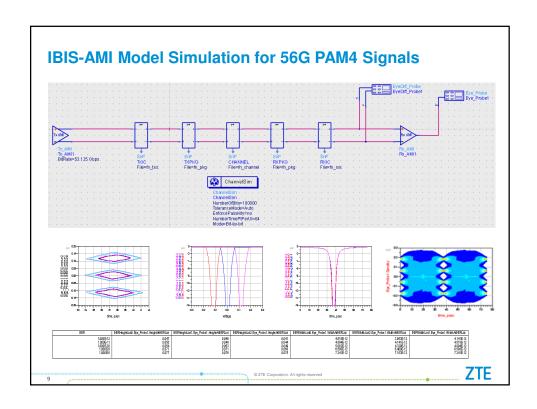

| 14:10 | The Impact of Channel Performance to 56G PAM4 Simulation 70 Yin, Changgan; Zhu, Shunlin (ZTE Corporation, China)                                                           |

| 15:00 | BREAK (Refreshments and Vendor Tables)                                                                                                                                     |

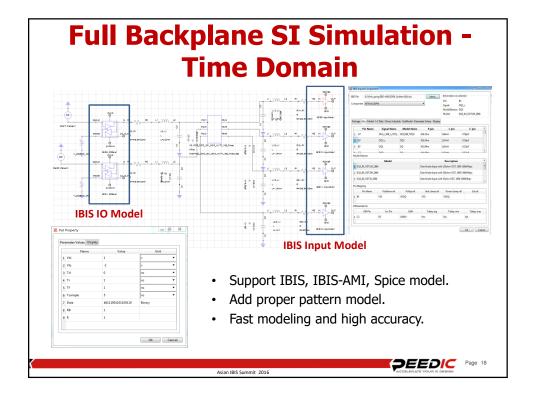

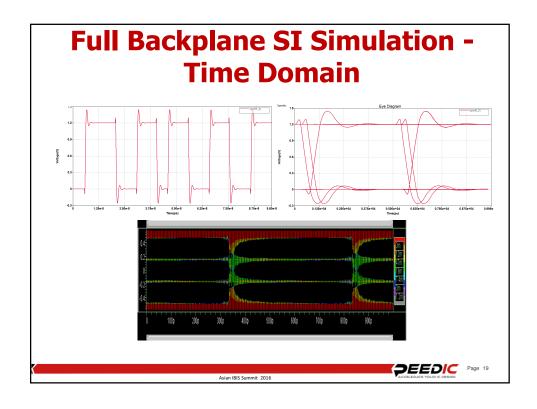

| 15:20 | Achieving Full System Signal Integrity for High Speed 90 Backplane Simulation Dai, Wenliang (Xpeedic Technology, China)                                                    |

| 15:50 | On-Die Decoupling Model Improvements for IBIS Power Aware 101 Models  Wolff#, Randy; Viscardi##, Aniello (Micron Technology; #USA, ##Italy)                                |

| 16:15 | <pre>IBISCHK6 V6.1.3 and Executable Model File Checking</pre>                                                                                                              |

| 15:40 | Touchstone Conversion Wrapper                                                                                                                                              |

| 17:05 | DISCUSSION                                                                                                                                                                 |

| 17:20 | CONCLUDING ITEMS                                                                                                                                                           |

| 17:30 | END OF IBIS SUMMIT MEETING                                                                                                                                                 |

## IBIS Chair's Report

http://www.ibis.org/

Mike LaBonte Signal Integrity Software Chair, IBIS Open Forum

> Asian IBIS Summit Shanghai, China November 11, 2016

IBIS Chair's Report

1

#### **Specification Development**

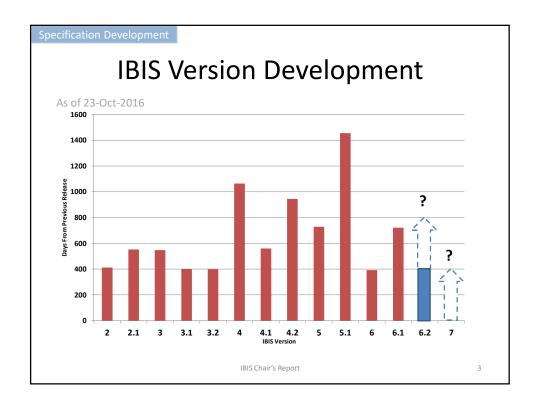

#### **IBIS Milestones**

#### I/O Buffer Information Specification

- 1993-1994 IBIS 1.0-2.1:

- Behavioral buffer model (fast simulation)

- Component pin map (easy EDA import)

- 1997-1999 IBIS 3.0-3.2:

- Package models

- Electrical Board Description (EBD)

- Dynamic buffers

- 2002-2006 IBIS 4.0-4.2:

- Receiver models

- AMS languages

- 2007-2012 IBIS 5.0-5.1:

- IBIS-AMI SerDes models

- Power aware

- 2013-2015 IBIS 6.0-6.1:

- PAM4 multi-level signaling

- Power delivery package models

#### Other Work

- 1995: ANSI/EIA-656

- IBIS 2.1

- 1999: ANSI/EIA-656-A

- IBIS 3.2

- 2001: IEC 62014-1

- IBIS 3.2

- 2003: ICM 1.0

- Interconnect Model Specification

- 2006: ANSI/EIA-656-B

- IBIS 4.2

- 2009: Touchstone® 2.0\*

- 2011: IBIS-ISS 1.0

- Interconnect SPICE Subcircuit specification

\*Touchstone\* is a registered trademark of Agilent Technologies, Inc.

IBIS Chair's Report

## Work In Progress

- Advanced Technology Modeling Task Group

- IBIS 6.2 dedicated to reference node clarifications

- Back-channel support (BIRD147.3)

- C\_comp model enhancements

- Redriver flow enhancements

- Interconnect Task Group

- External Package/on-die models using IBIS-ISS and Touchstone®

- IBIS Quality Task Group

- IBISCHK enhancements and documentation

IBIS Chair's Report

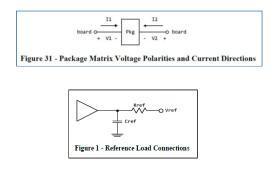

## In Progress: IBIS 6.2

- Purpose: Clarify reference terminal conventions in IBIS

- BIRDs submitted, discussed in ATM Task Group

- Editorial Task Group will resume after BIRDs passed

IBIS Chair's Report

5

#### Specification Developmen

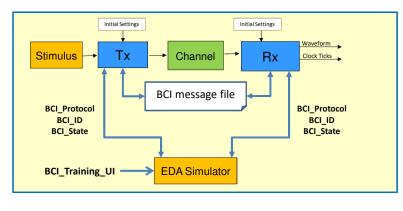

## In Progress: Backchannel support

- · Purpose: Backchannel to model time domain link training

- BIRD 147.3 recommended by ATM Task Group for acceptance

IBIS Chair's Report

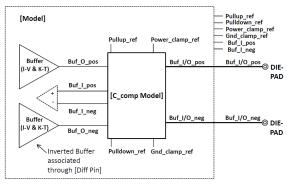

#### In Progress: C\_comp Model Enhancements

- Purpose: Accurate C\_comp model supporting frequency and voltage dependence, using IBIS-ISS and Touchstone®

- · In ATM Task group, BIRD not yet submitted

IBIS Chair's Report

7

#### Specification Development

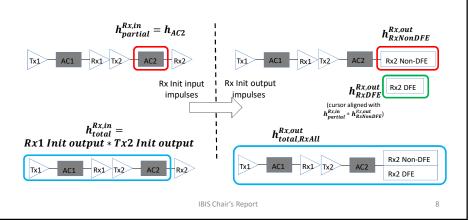

#### In Progress: Redriver Flow Enhancements

- Purpose: Provide full redriver channel impulse to Rx Init for optimization, eliminate the need for deconvolution

- In ATM Task group, BIRD not yet submitted

## In Progress: Interconnect BIRD

- Purpose: External Package/on-die models using IBIS-ISS

- In Interconnect Task Group, BIRD (draft 42) not yet submitted

IBIS Chair's Report

9

#### **Specification Development**

## In Progress: Approved BIRDs

• All are targeted for IBIS 6.2

| BIRD | Title                                                      |

|------|------------------------------------------------------------|

| 179  | New IBIS-AMI Reserved Parameter Special_Param_Names        |

| 180  | Require Unique Pin Names in [Pin]                          |

| 182  | POWER and GND [Pin] signal_name as [Pin Mapping] bus_label |

| 183  | [Model Data] Matrix Subparameter Terminology Correction    |

IBIS Chair's Report

## In Progress: Open BIRDs

- Some are targeted for IBIS 6.2

- Some are superseded by new BIRDs and will be rejected

| 125.1 | Make IBIS-ISS Available for IBIS Package Modeling                                  |

|-------|------------------------------------------------------------------------------------|

| 145.3 | Cascading IBIS I/O buffers with [External Circuit]s using the [Model Call] keyword |

| 157   | Parameterize [Driver Schedule]                                                     |

| 158.3 | AMI Touchstonefile (R) Analog Buffer Models                                        |

| 161.1 | Supporting Incomplete and Buffer-only [Component] Descriptions                     |

| 163   | Instantiating and Connecting [External Circuit] Package Models with [Circuit Call] |

| 164   | Allowing Package Models to be defined in [External Circuit]                        |

| 165   | Parameter Passing Improvements for [External Circuit]s                             |

| 166   | Resolving problems with Redriver Init Flow                                         |

| 181   | I-V Table Clarifications                                                           |

| 184.1 | Model_name and Signal_name Restriction for POWER and GND Pins                      |

| 185.1 | Section 3 Reserved Word Guideline Update                                           |

IBIS Chair's Report

#### Organization

#### **IBIS Officers 2016-2017**

Chair: Mike LaBonte, Signal Integrity Software

Vice-Chair: Lance Wang, IO Methodology Inc.

Secretary: Randy Wolff, Micron Technology

Treasurer: Bob Ross, Teraspeed Labs

Librarian: Anders Ekholm, Ericsson

Webmaster: Mike LaBonte, Signal Integrity Software

Postmaster: Curtis Clark, ANSYS

IBIS Chair's Report

15

#### Organization

### **IBIS Meetings**

- Teleconferences every week

- Quality Task Group (Tuesdays)

- Advanced Technology Modeling Task Group (Tuesdays)

- Interconnect Task Group (Wednesdays)

- Editorial Task Group (some Fridays, now suspended)

- IBIS Open Forum teleconference every 3 weeks

- IBIS Summit meetings: DesignCon, SPI, Shanghai, Taipei, Tokyo, EPEPS (2015)

IBIS Chair's Report

## IBIS Model Simulation with R/L/C\_dut

Xuefeng Chen

Asian IBIS Summit Meeting

Shanghai, China

November 11, 2016

#### **Outline**

- Introduction of IBIS R/L/C\_dut subparameters

- IBIS algorithm enhancement for R/L/C\_dut

- Accuracy test of complete IBIS model with R/L/C\_dut

- Summary

© 2016 Synopsys, Inc. 2

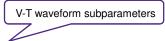

#### Introduction of IBIS R/L/C\_dut subparameters

IBIS 3.2:

The R\_dut, C\_dut, and L\_dut subparameters are analogous to the package parameters R\_pkg, C\_pkg, and L\_pkg and are used if the waveform includes the effects of pin inductance/capacitance

#### Example:

© 2016 Synopsys, Inc. 3

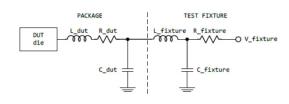

## IBIS Algorithm Without R/L/C\_dut

Two steps to get scaling coefficients of PU, PD (Ku,Kd)

- 1. Get Idie(t) by V-T waveforms, C\_comp and R/L/C\_fixture : apply  $i=C^*dv(t)/dt$  and  $v=L^*di(t)/dt$

- 2. Use the well known 2EQ/2UK algorithm:

```

\begin{split} 0 &= Ku(t) * lu(Vwfm1(t)) + lpc(Vwfm1(t)) - Kd(t) * ld(Vwfm1(t)) - lgc(Vwfm1(t)) - ldie(Vwfm1(t)) \\ 0 &= Ku(t) * lu(Vwfm2(t)) + lpc(Vwfm2(t)) - Kd(t) * ld(Vwfm2(t)) - lgc(Vwfm2(t)) - ldie(Vwfm2(t)) \\ \end{split}

```

For details, please refer

"IBIS Algorithm Including Reactive Loads", Xuefeng Chen, Asian IBIS Summit (China), September 11, 2007.

© 2016 Synopsys, Inc. 4

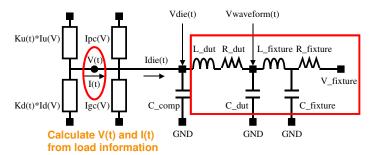

#### IBIS algorithm enhancement for R/L/C\_dut

The step 1 of Vdie(t) & Idie(t) calculation extends to:

- a) get I(L\_fixture) by Vwaveform(t) and L/R/C/V\_fixture.

- b) get I(C\_dut) by Vwaveform(t) and C\_dut.

- c) get I(L\_dut) by above I(L\_fixture) and I(C\_dut).

- d) get Vdie(t) by I(L\_dut), L\_dut, R\_dut and Vwaveform(t).

- e) get I(C\_comp) by Vdie(t) and C\_comp

- f) get Idie(t) by I(C\_comp) and I(L\_dut).

© 2016 Synopsys, Inc. 5

#### A Complete IBIS Model with R/L/C\_dut I/O Model\_type 0.92pF C\_comp [Voltage Range] 5.000V [Pulldown] 3 V 3 V [GND Clamp] 1000 mV 1000 mV [Pullup] 0 V Os 1 ns 2 ns 3 ns 4 ns 5 ns 6 ns 7 ns rising waveform (VCC) falling waveform (VCC) [POWER Clamp] [Rising Waveform] V\_fixture = 5 $R_{\text{fixture}} = 50$ 1.5 V L fixture = 2n 1000 mV C fixture = 3p R dut=5 L\_dut=2n C\_dut=3p 1 ns 2 ns 3 ns 4 ns 5 ns 6 ns 7 ns falling waveform (GND) rising waveform (GND) SYNOPSYS" © 2016 Synopsys, Inc. 6

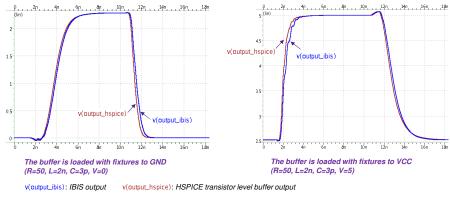

### **Accuracy Test of the Complete IBIS Model with** R/L/C\_dut

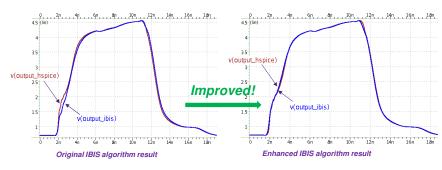

The output result by original IBIS algorithm (ignore R/L/C\_dut) when the buffer is loaded with R/L/C/V fixtures:

SYNOPSYS © 2016 Synopsys, Inc. 7

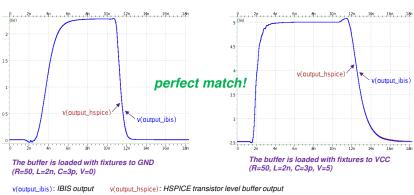

### **Accuracy Test of the Complete IBIS Model with** R/L/C\_dut (Cont.)

The output result by enhanced IBIS algorithm (consider R/L/C dut in V-T solving) when the buffer is loaded with R/L/C/V\_fixtures:

© 2016 Synopsys, Inc. 8

SYNOPSYS.

## Accuracy Test of the Complete IBIS Model with R/L/C\_dut (Cont.)

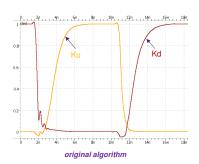

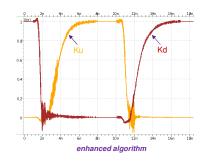

Ku, Kd comparison between original IBIS algorithm and enhanced IBIS algorithm:

Due to R/L/C\_dut, the Ku, Kd results look more noisy. But it contributes for much better accuracy of output waveform!

© 2016 Synopsys, Inc. 9

SYNOPSYS

## Accuracy Test of the Complete IBIS Model with R/L/C\_dut (Cont.)

The output result comparison between original and enhanced IBIS algorithms when the buffer is loaded with W element and IBIS terminators:

$\textit{v}(\texttt{output\_ibis}) : \textit{IBIS output} \qquad \textit{v}(\texttt{output\_hspice}) : \textit{HSPICE transistor level buffer output}$

© 2016 Synopsys, Inc. 10

#### **Summary**

- Enhanced IBIS algorithm is provided to support the R/L/C\_dut subparameters in V-T tables.

- The algorithm can get perfect match to transistor level buffer under the loading conditions of V-T extraction, and shows obvious accuracy improvement when the buffer is loaded with W element and IBIS terminator.

- The Ku & Kd results of V-T solving is very sensitive to R/L/C\_dut. So IBIS model extractors need be cautious to use such subparameters.

- In fact, based on the algorithm, R/L/C\_dut provides a solution to describe a little more complicated "C comp" circuit due to below common situations:

- ✓ located between V-T extraction point and die pad

- ✓ involved in V-T solving to get Vdie(t) & Idie(t)

- ✓ the values are constant for different V-T tables.

- ✓ need to be added in circuit during buffer simulation

© 2016 Synopsys, Inc. 11

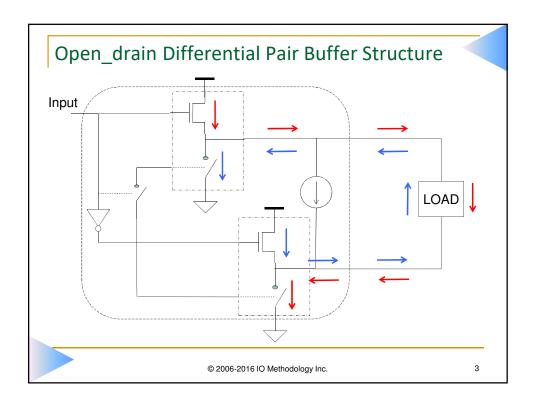

# Case Study: Modeling IBIS for Open\_drain True Differential Pair Buffer

Lance Wang, IO Methodology Inc. Yan Liang, Maxim Integrated

Asian IBIS Summit – Shanghai, China November 11th, 2016

#### Outline

- Open\_drain Differential Pair Buffer Structure

- Review IBIS Modeling Method

- Differential Pair Modeling Method

- Output Type Buffer

- Open\_drain Type Buffer

- Practical Method for Open\_drain Differential Pair Buffer

- Conclusions

© 2006-2016 IO Methodology Inc.

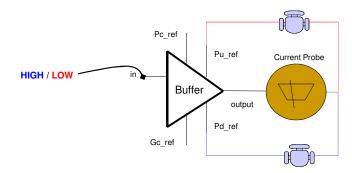

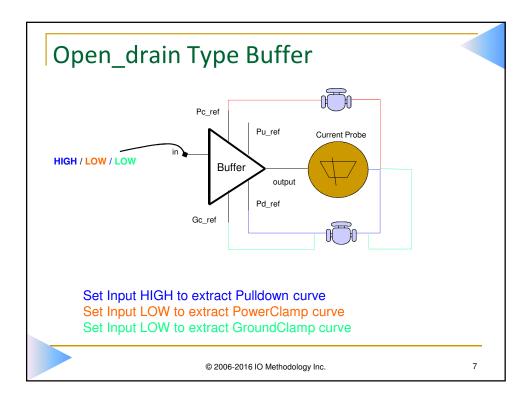

## Review IBIS Modeling Method

- Differential Pair Modeling Method

- Output Type Buffer

- Open\_drain Type Buffer

© 2006-2016 IO Methodology Inc.

## Differential Pair Modeling Method

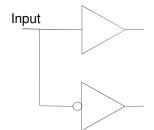

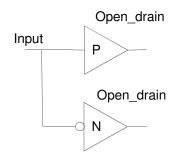

- IBIS uses two singleend models to be a differential pair

- IBIS uses [Diff Pin] to define two pins to be a differential pair pins

- Uses two opposite inputs as required

© 2006-2016 IO Methodology Inc.

5

## Output Type Buffer (non-inverting)

Set Input LOW to extract Pullup curve Set Input HIGH to extract Pulldown curve

© 2006-2016 IO Methodology Inc.

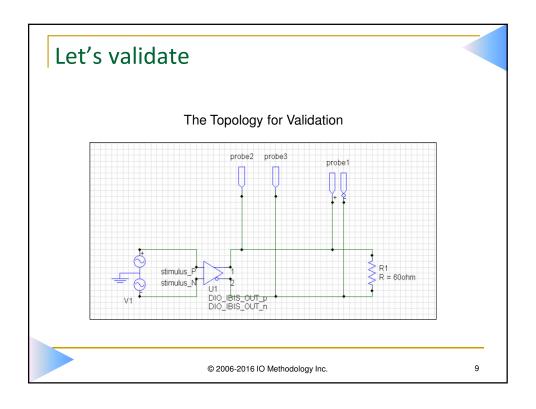

## Practical Method for Open\_drain Differential Pair Buffer

As the normal method, we will use two

Open\_drain type IBIS models for Positive and Negative pins.

© 2006-2016 IO Methodology Inc.

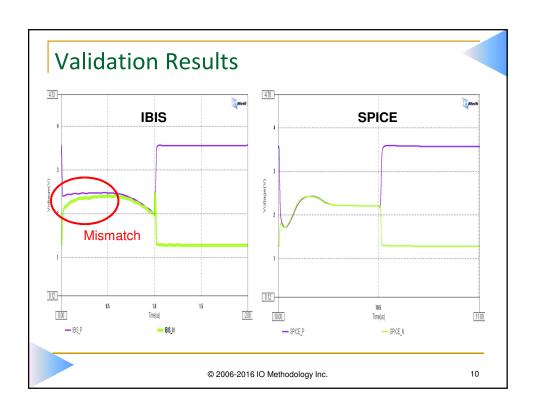

#### Root cause for mismatch and solution

- We missed some currents in the IBIS models

- There is some current between P and N pins

- IBIS Open\_drain type model without Pullup curve. Assuming Pullup current is Zero

- Solution

- We can use Output type model to capture all curve data

- However, we need to use Open\_drain type setting to capture the data

© 2006-2016 IO Methodology Inc.

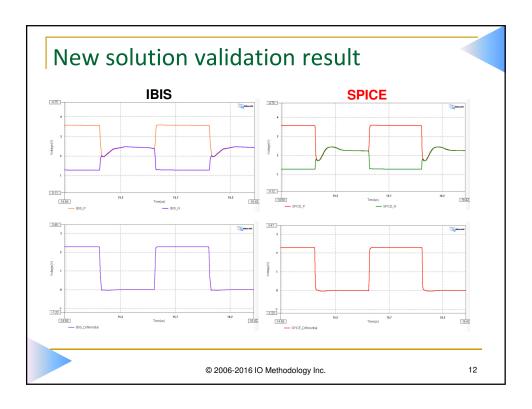

#### Conclusion

- Open\_drain differential pair is a special case for IBIS modeling

- IBIS Open\_drain model is without the Pullup data

- We need to use Output/IO type IBIS model to capture the Pullup data for this kind of differential pair buffer

- However we need to IBIS Open\_drain modeling setting for extractions

- IBIS C\_comp needs to improve to be matched better

© 2006-2016 IO Methodology Inc.

13

#### C\_comp

- Currently, IBIS Spec only allows 4 values at the most

- We might need to have more C\_comp values according DC levels and frequency changes

- Study is in process ...

© 2006-2016 IO Methodology Inc.

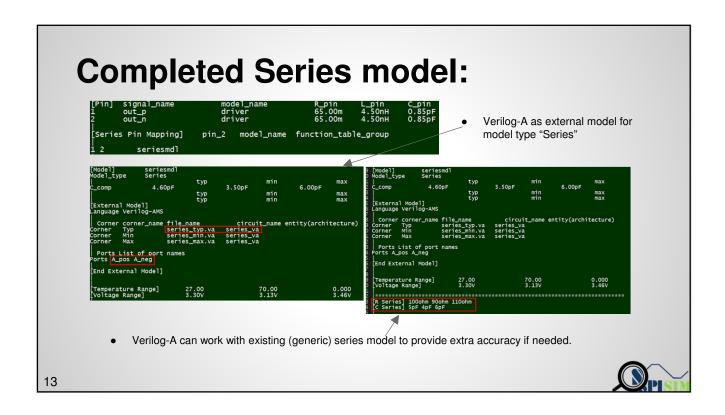

# Differential Modeling Flow with Series Model in Verilog-A

Asian IBIS Summit Shanghai, China November 11, 2016

Wei-hsing Huang, SPISim

Wei-hsing.Huang@spisim.com

Sanjeev Gupta, SigIntegrity-Solutions

sanjeev@sigintegrity-solutions.com

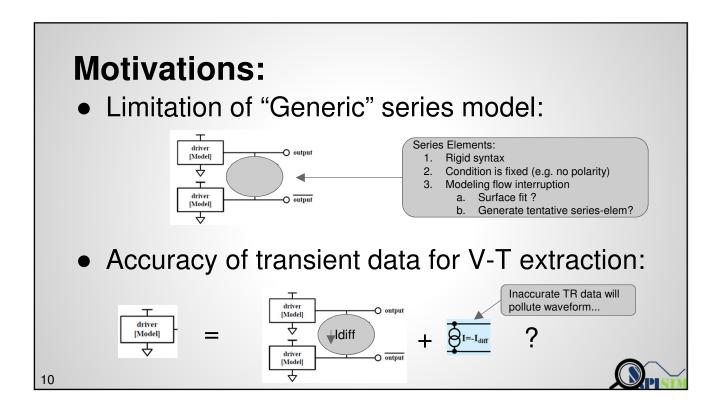

## Agenda:

- Background & Motivation

- Verilog-A based modeling

- Differential current

- External model

- Flow & Validation

- Summary

- Q&A

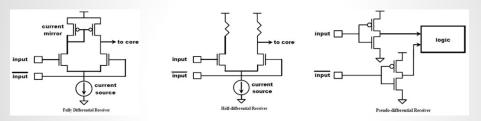

## Background: (1, IBIS CookBook V4)

Differential buffer: True/Half/Pseudo differential.

• [Diff Pin]: describe differential behavior between two pins.

```

[Diff Pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

I

2      3      NA      NA      Ons      5ns

6      5      NA      NA      Ons      5ns

```

**O**PSIM

3

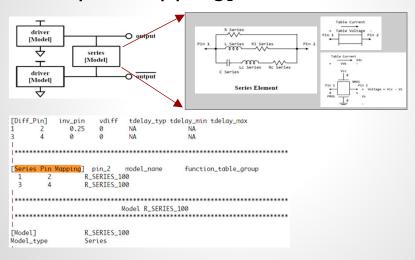

## Method 1 for Half/True differential:

• [Series pin mapping]/Series Model:(2)(3)

### Method 2 for Half/True differential:

• [External Model]: Spice/VHDL-AMS/Verilog-AMS/IBIS-ISS(4)

```

VHDLAMS-DRV

Model_type

Polarity

Output

Non-Inverting

C_comp

4.60pF

3.50pF

6.00pF

Vmeas = 1.15V

Cref = 1pF

Rref = 50ohms

Vref = 0V

Input_diff

These model types specify that the model defines a true differential model available directly through the

Output_diff

I/O_diff

[External Model] keyword documented in Section 6.3.

3-state_diff

Language VHDL-AMS

I Corner corner_name file_name

circuit_name entity(architecture)

ideal_driver.vhd

driver_ideal(linear)

driver_ideal(linear)

Corner

ideal_driver.vhd

Corner

Corner

ideal_driver.vhd

driver_ideal(linear)

I Ports List of port names (in same order as in VHDL-AMS)

Ports D_drive A_puref A_pdref A_signal

[End External Model]

```

Method 1 & 2 can be used together!

5

**OPISIM**

**Background:** Data extraction: I-V curves Common-mode current Differential current Step through holding V<sub>n</sub> same range as V C\_comp & C\_diff I-V driver Figure 4.13 – I-V Table Extraction Fixture for a Differential Buffer [Model] series [Model] Rise R=R fixture O output [Model] R=R\_fixture V=V fixture V-T Figure 4.18 - V-T Table Extraction Fixture for a Differential Buffer 6

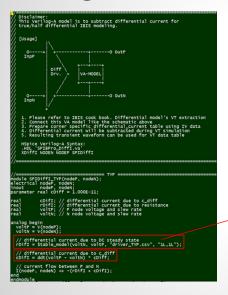

A Verilog-A device can be used in differential V-T extraction.

- · Behavioral device is very versatile

- Support operator like ddt, if .. else

- Supports 1/2D look-up table (5), (6)

```

#VoutN VoutP TD1ff_Typ

-1.50E+00 -1.50E+00 0.00E+00

-1.50E+00 -1.46E+00 -7.83E+00

-1.50E+00 -1.41E+00 -7.83E+00

-1.50E+00 -1.37E+00 -2.41E+01

-1.50E+00 -1.37E+00 -3.25E+01

-1.50E+00 -1.38E+00 -4.13E+01

-1.50E+00 -1.28E+00 -5.03E+01

-1.50E+00 -1.19E+00 -5.95E+01

-1.50E+00 -1.19E+00 -6.91E+01

-1.50E+00 -1.10E+00 -7.89E+01

-1.50E+00 -1.05E+00 -7.89E+01

-1.50E+00 -1.01E+00 -9.94E+01

-1.50E+00 -1.01E+00 -9.94E+01

-1.50E+00 -1.01E+00 -9.94E+01

```

**O**PSIM

## Verilog-A for V-T extraction:

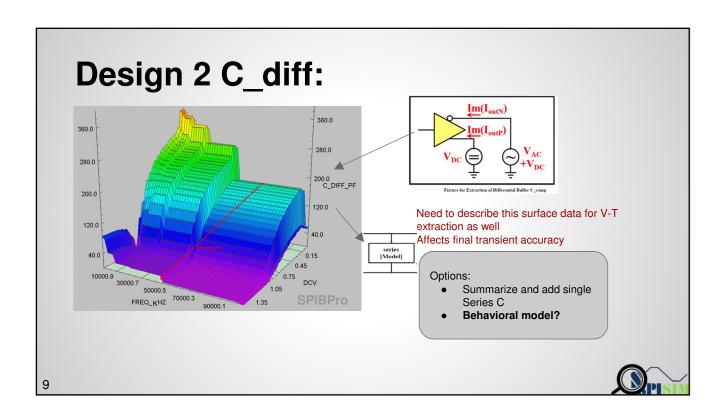

Simulator only supports 1D table? 2D bi-linear look-up can still be done Voltage & freq. Dependent C\_Diff (or use cross() to find freq. dynamically)

parameter real freq = 1.089; // current wering frequency

parameter real freq = 2.089; // cufff at frequency

parameter real freq = 2.089; // cufff at frequency

parameter real freq = 2.089; // cufff at frequency

parameter real freq = 2.089; // cufff at frequency

parameter real freq = 2.089; // cufff at frequency

parameter real confir. // prode motion and sile wrate

real cuff, // prode voltage and sile wrate

real cuff, cufff; // differential capacitance

analogo begin

voltp = V(noder);

voltn = V(noder);

// differential current due to DC steady state

poifi = stable\_model(voltn - voltp, 'driver\_Typ.csv', 'll.,ll');

// differential current due to C\_diff

cufff = Stable\_model(voltn - voltp, 'driver\_Typ.csv', 'll.,ll'); // at freq = 2.004

cufff = Cufff = 2.004 freq - freq = 2.004

cufff = Cufff = 2.004 freq - freq = 2.004

cufff = Cufff = 2.004 freq - freq = 2.004

cuff = Cufff = 2.004 freq - freq = 2.004

cuff = 2.004 freq

12

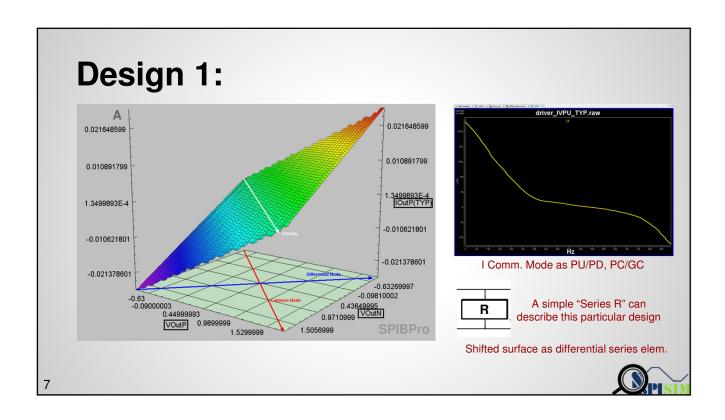

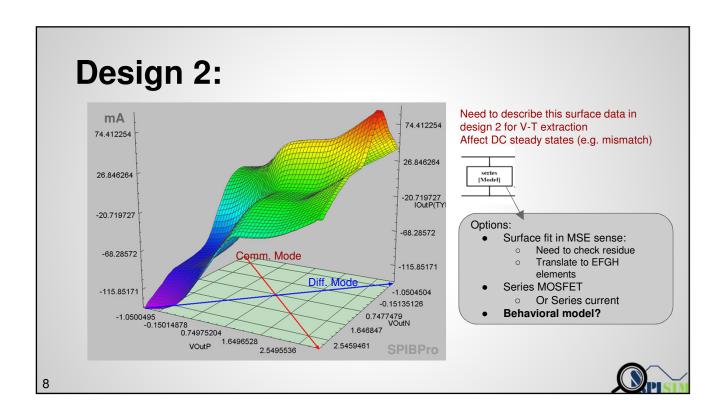

# **Modeling flow validation:**

- Use an existing single-ended driver for P and N

- Insert approximate non-linear behavioral R/L/C elements between P and N outputs

- Flow should recreate same PU/PD/PC/GC as driver

- I-V surface plot should reveal inserted resistance

- C Diff/C Comp surface should reveal inserted cap

- Correlations of V-T table depends on I Diff accuracies.

15

## **Summary:**

- Verilog-A for differential V-T extraction

- Versatile, supports many operators

- E.g. ddt(Vx), \$table\_model for 1D/2D lookup

- Streamlines modeling flow

- Extract transient differential current

- Improve V-T extraction accuracies

- Use Verilog-A to remove rigid series syntax

- External model for "Series":

- o [External model] supports "Series" type model

- o Can work with generic series model

## References:

1. IBIS Cookbook V4

https://ibis.org/cookbook/cookbook-v4.pdf

2. IBIS summit Jan/Mar 2001 by Hazem Hegazy (Mentor)

https://ibis.org/summits/jan01/hegazy.zip https://ibis.org/summits/mar01/hegazy.zip

3. IBIS summit 2002 ~ 2004 by Arpad Muranyi (Intel)

https://ibis.org/summits/oct02/muranyi.pdf

https://ibis.org/summits/oct03/muranyi.pdf

https://ibis.org/summits/feb04a/muranyi2.pdf

4. IBIS summit 2014 ~ 2015 by Shivani Shama et. al. (Cadence)

https://ibis.org/summits/nov14b/sharma.pdf

https://ibis.org/summits/nov15b/liang.pdf

5. Verilog A Language Reference Manual (LRM, Vendor Specific) http://accellera.org/images/downloads/standards/v-ams/VAMS-LRM-2-3-1.pdf

6. HSpice User's Manual

**OPISIO**

17

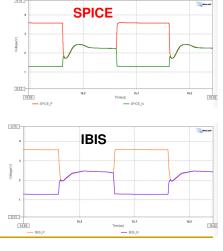

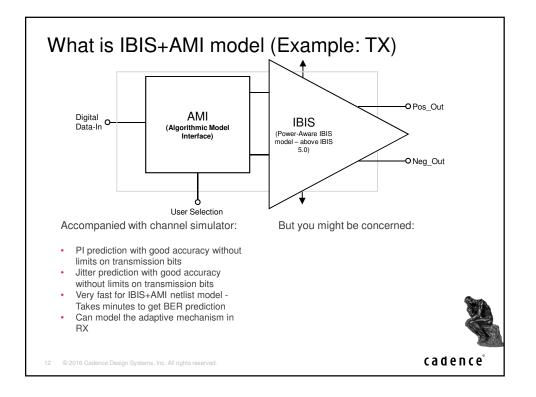

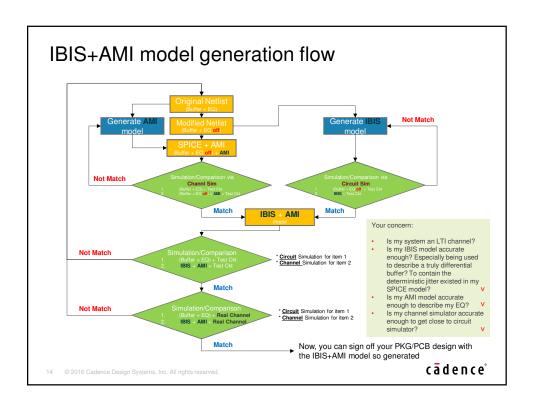

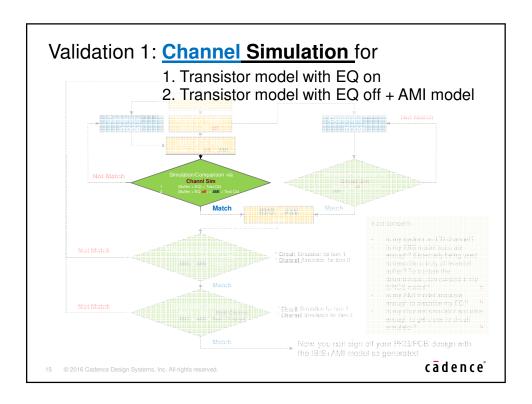

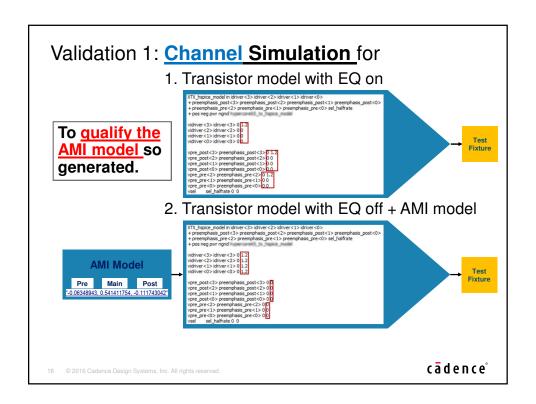

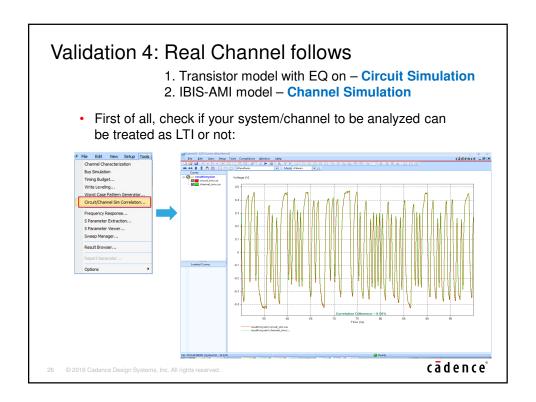

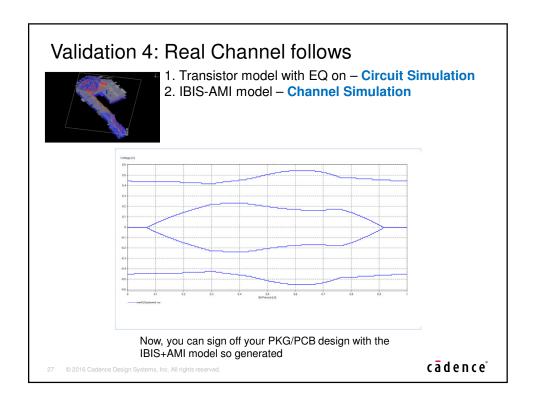

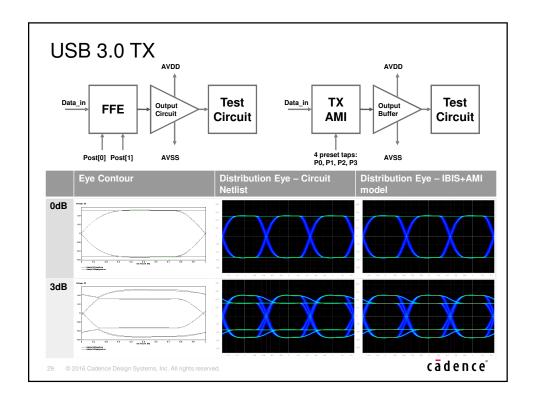

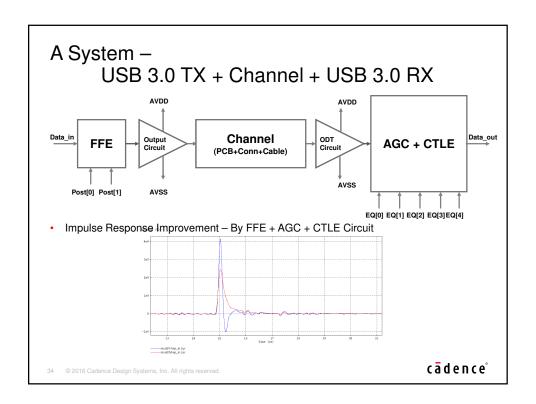

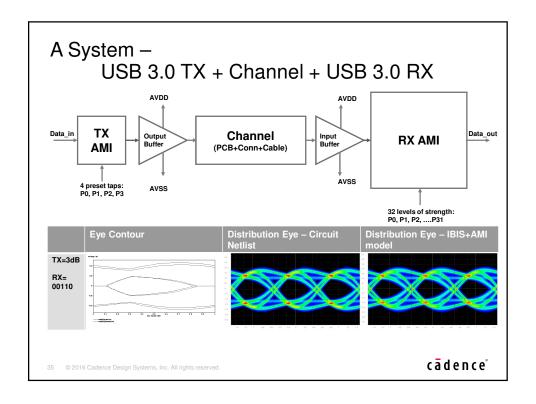

# Validation 1: Channel Simulation for 1. Transistor model with EQ on 2. Transistor model with EQ off + AMI model To qualify the AMI model so generated. Why Channel Simulation?: 1. AMI model can only be used in Channel Simulation 2. Put transistor models under Channel Simulation will narrow down the possible cause for any difference happened here to the AMI model so generated.

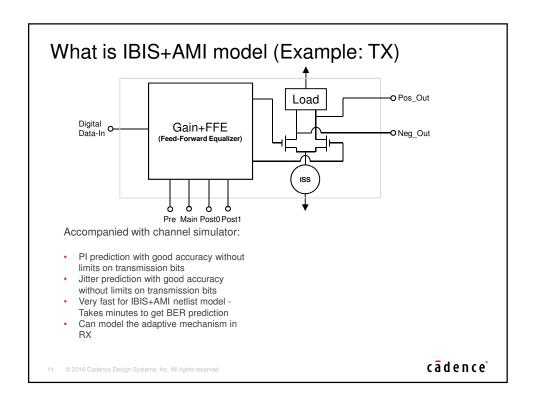

### Conclusion

- An accurate IBIS+AMI model could be an alternative approach to validate your "system" design versus a transistor netlist model

- An accurate IBIS-AMI model consists of two parts an <u>accurate IBIS model</u> and <u>an accurate AMI model</u> <u>validation</u> is the key

- An accurate IBIS should be generated by a tool which can well describe a <u>truly</u> <u>differential pair</u> in all V/I, V/T and I/T curves.

- An accurate AMI model should be generated by a tool with a rich library such that the generation tool can use all available means in the library to describe all your possible designs.

- A simulation environment which supports transistor netlist models is fundamental for IBIS+AMI model generation/validation.

37 © 2016 Cadence Design Systems, Inc. All rights reserved.

cādence

© 2016 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and Spectre are registered trademarks and Sigrity, SystemSI, and T2B are trademarks of Cadence Design Systems, Inc. in the United States and other countries.. All rights reserved. All other trademarks are the property of their respective owners.

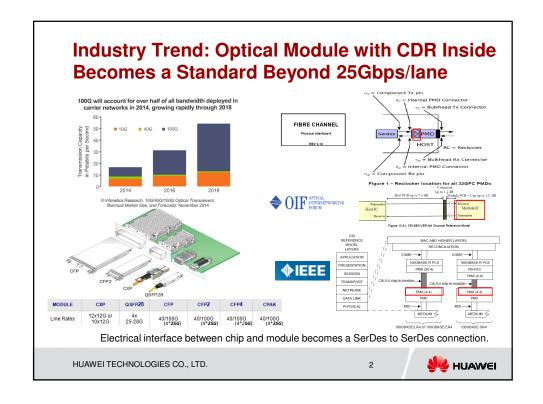

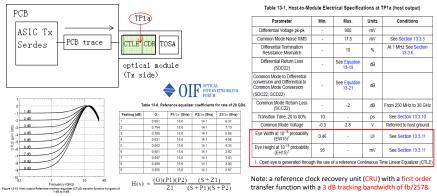

# Electrical Interface Compliance Test Defined in OIF CEI-28G-VSR / IEEE 802.3bm CAUI-4

- TP1a is the test point after CTLE inside CDR device. The real eye diagram at TP1a can't be measured

- A standard "Reference CTLE" and "Golden PLL" model is defined for compliance test instead

HUAWEI TECHNOLOGIES CO., LTD.

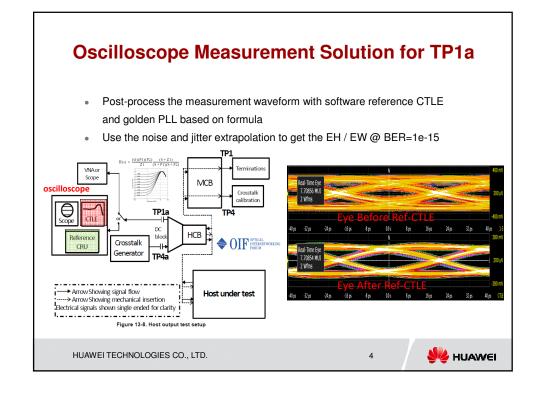

# Simulation Solution for TP1a (1): Acquire Certain Module's CDR IBIS-AMI Model Advantage: Display real performance of certain optical module's CDR Supported by commercial EDA tools Disadvantage: Not all vendors can provide their CDR's IBIS-AMI model Not the VSR/CAUI-4 defined compliance analysis method EW@BER=1e-15>=0.46UI EH@BER=1e-15>=95mV EY@RER=1e-15>=0.46UI EH@BER=1e-15>=95mV EY@RER=1e-15>=0.46UI EH@BER=1e-15>=95mV EY@RER=1e-15>=0.46UI EH@BER=1e-15>=0.46UI E

- Similar to measurement, current simulation has to be done with self-programmed data post-processing script

- Without reference CTLE IBIS-AMI model, VSR/CAUI-4 electrical interface simulation can't be achieved in EDA tools

HUAWEI TECHNOLOGIES CO., LTD.

**W** HUAWEI

# **Suggest IBIS Organization Issue the IBIS-AMI Model of Standard Reference CTLE for Customers**

- Suggest IBIS Organization issue the standard VSR/CAUI-4 compliant IBIS-AMI model including reference CTLE and golden PLL

- As reference CTLE is a definite formula and fully meets LTI system, it's not difficult to generate such a standard model

HUAWEI TECHNOLOGIES CO., LTD.

7

### **Further Discussion**

- The issue of the VSR/CAUI-4 based IBIS-AMI model may provide a way for optical CDR vendor to do the correlation between their setting and MSA EQ setting

- Although MSA defined the unified I2C EQ setting, different optical module vendor uses different CDR and different CTLE, which may have different mapping relationship between MSA EQ and CDR's CTLE.

- Without a unified correlation method, how to keep the reliability that passing the reference CTLE test of TP1a can pass the error test

TABLE 6-34 INPUT EQUALIZATION (PAGE 03H BYTES 234-235)

SFF Committee

SFF-8636

Specification for

Management Interface for Cabled Environments

| Value | Transmitter Inp | ut Equalization |

|-------|-----------------|-----------------|

| F     | Nominal         | Units           |

| 11xxb | Reserved        |                 |

| 1011b | Reserved        |                 |

| 1010b | 10              | dB              |

| 1001b | 9               | dB              |

| 1000b | 8               | dB              |

| 0111b | 7               | dB              |

| 0110b | 6               | dB              |

| 0101b | 5               | dB              |

| 0100b | 4               | dB              |

| 0011b | 3               | dB              |

| 0010b | 2               | dB              |

| 0001b | 1               | dB              |

| 0000b | 0               | No EQ           |

- · CTLE non-linearity feature should be considered in future

- > Currently formula-based model without considering the non-linearity

HUAWEI TECHNOLOGIES CO., LTD.

Asian IBIS Summit Shanghai, China November 11, 2016

# Necessity for integrating FEC functionality for PAM4 in AMI simulations

Xiaoqing Dong (dongxiaoqing82@huawei.com), Huawei Technologies Chunxing Huang (nickhuang168@163.com), Shenzhen Zhongzeling Electronics

HUAWEI TECHNOLOGIES CO., LTD.

### **Agenda**

- · Review of AMI simulation methodology

- FEC simulation introduction for PAM4 link

- Summary and suggestion

HUAWEI TECHNOLOGIES CO., LTD.

**W** HUAWEI

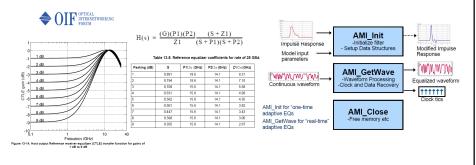

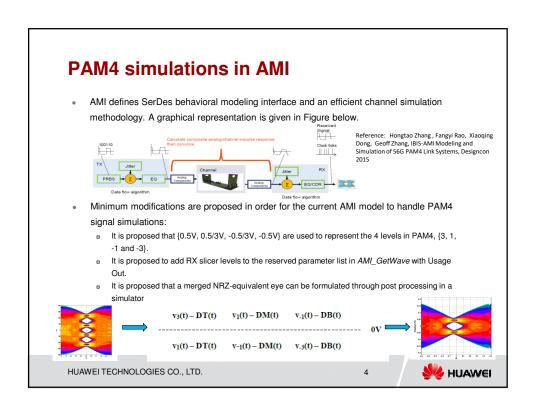

### **General AMI simulation methodology** Figure cited from IBIS Impulse Response Processing summit proposal archive With TX, RX EQ With TX EQ Recovered Clock With TX, RX EQ Input Waveform (Non-LTI) (Non-LTI) TX FFE, RX linear equalization is processed in AMI Init function; RX CDR, DFE are mostly modeled in AMI\_GetWave function; Converged equalization parameters can be output using AMI\_parameters\_out; BER targets are set by users to monitor link qualities. HUAWEI TECHNOLOGIES CO., LTD. 👺 HUAWEI 3

### The industry existing/emerging PAM4 standards

> 28G generation: IEEE-802.3bj-KR4

1.4.53b 100GBASE-KR4: IEEE 802.3 Physical Layer specification for 100 Gb/s using 100GBASE-R encoding, Clause 91 RS-FEC, and 2-level pulse amplitude modulation over four lanes of an electrical backplane, with a total insertion loss up to 35 dB at 12.9 GHz. (See IEEE Std 802.3, Clause 93.)

The receive path of the RS-FEC sublayer may have the option to perform error detection without correction to reduce the data delay (see 91.53.3). When the receive path of the RS-FEC sublayer performs error correction, the link is required to operate with a BER of  $10^{-5}$  or better. When the BER EEC sublayer is configured to bypass error correction, the link is required to operate with a BER of  $10^{-5}$  or better. When the DER of  $10^{-5}$  or better. In this

FEC is mandatory in major PAM4 standards to assure basic link BER target!

> 56G generation: OIF-CEI-56G

A raw BER better than or equal to 1E-4 s required per lane. A compliant receiver, when receiving from a compliant transmitter over a compliant channel, shall deliver the specified raw BER to the subsequent FEC decoder, including burst errors. The burst error length delivered to the PAM4 decoder having more than 65 PAM4 symbol errors shall have a probability of less than 1E-20. (see, 18.A Appendix -, 18.B Appendix -)

Emerging commercial simulators support BER simulations up to no better than 1e-5 or 1e-4 for PAM4, according to industry standards. This works for NRZ, but considering FEC has become crucial to enable basic link performance for PAM4, and error propagation of different SerDes makes different error distribution features in an actual link, it is suggested that FEC functionalities be integrated in AMI for PAM4.

HUAWEI TECHNOLOGIES CO., LTD.

5

### PAM4 vs. NRZ: error propagation mechanism

- Given span-symbol error has very low occurrence probability, symbol error is assumed to

occur across adjacent levels in PAM4. This approach simplifies the calculation of erroneous

voltages, and makes an uniform calculation procedure of PAM4 and NRZ.

- For PAM4, errors only occur between (1,1/3), (1/3,-1/3) and (-1/3,-1). The scaling factor for erroneous voltage offset is 2/3 x DFE coefficients.

- $\bullet$   $\,$  1+Z  $^{\!-1}$  coding scheme can't solve the error propagation issue introduced from DFE.

Binary bits to PAM4 mapping

P)0 P=0 P=0

HUAWEI TECHNOLOGIES CO., LTD.

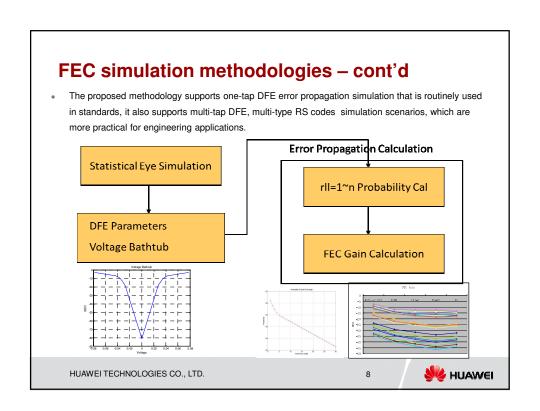

# FEC simulation methodologies • There are multiple approaches to enable FEC simulation in industry. The one we implemented, is based on burst error probability calculation, where burst error length is set to be long enough to assure calculation accuracy, given converged DFE coefficients and error propagation probabilities. $BER = \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}} \sum_{n=1}^{N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1}$ $= \sum_{i=1}^{N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1} p(rII = i, E) \cdot W(E) \cdot p_i \cdot (1-p_i)^{n-N_{BL}-1} p(rII = i, E) \cdot$

### System simulation case study: PAM4 vs. NRZ Simulation condition: One-tap DFE model adopted; One symbol error causes error propagation spanning two-bit length. RS(544,514) defined in KP4 standard does not gain much compared to RS(528,514) in KR4 standard. RS(554,514,20)\_PAM4\_Pb=0.5 RS(544,514,15)\_NRZ\_Pb=0.5 RS(554,514,20) PAM4 Pb=0.3 RS(544,514,15)\_NRZ\_Pb=0.3 RS(544,514,15)\_NRZ\_Pb=0.1 RS\_FEC after BER HUAWEI TECHNOLOGIES CO., LTD. W HUAWEI 9

### System simulation case study: RS solutions

PAM4 link information:

- 29.877dB, ICN=2mV,

- DFE=[0.5;0.0105591419033788;-0.0838646291817282;-0.0411341054292222;-0.0330967146894018;-0.0126712251463267;-0.00584431523805114;-0.00244702521890698;0.00384402448806175;-0.0240163300157797;-0.00748279553106418;0.0522180947613083]];

Performance comparison for different PAM4 RS solutions:

| RS Type       | RS(544, 514) | RS(528, 514) | RS(544, 504) |

|---------------|--------------|--------------|--------------|

| BER           | 6.0e-6       | 6.0e-6       | 1.3350e-39   |

| SER after FEC | 1.7073e-29   | 3.7614e-14   | 1.3350e-39   |

| BER after FEC | 5.0247e-31   | 5.7090e-16   | 5.1558e-41   |

HUAWEI TECHNOLOGIES CO., LTD.

**W** HUAWEI

### **Summary**

- Conventional AMI simulation does not take into account FEC functionalities.

- Industry standards on PAM4 requires FEC to achieve basic BER targets (1e-12/15 for example), given same/similar channel insertion loss as NRZ systems.

- FEC gain can be modeled using error propagation theories.

- Burst error length should be long enough to assure calculation accuracy( ≥200 bits for RS(544,514) solution )

- FEC simulation algorithm should support multi-tap DFE, multi-type RS codes simulation scenarios.

- Concept has been proved for feasibility of PAM4 simulation to integrate FEC functionalities through two case studies.

- From system application's perspective, it is recommended that IBIS-AMI to consider integrating FEC simulation functionality for PAM4.

HUAWEI TECHNOLOGIES CO., LTD.

11

## Thank you

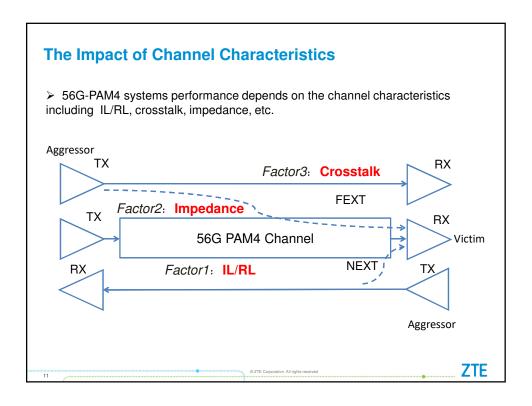

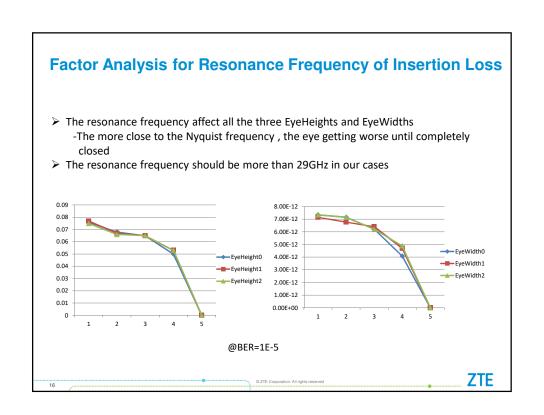

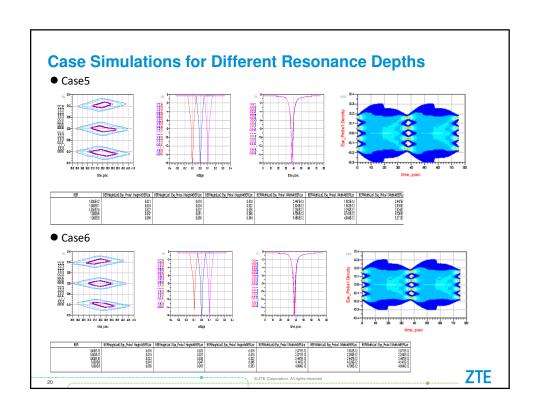

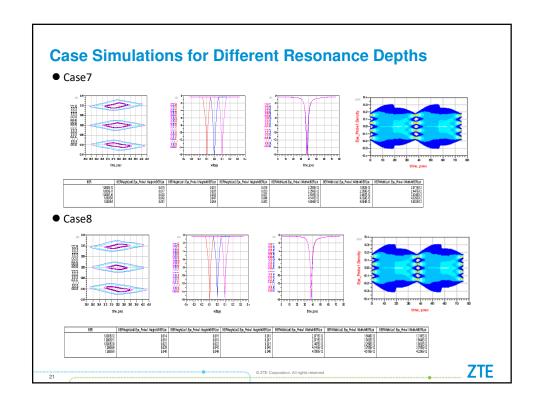

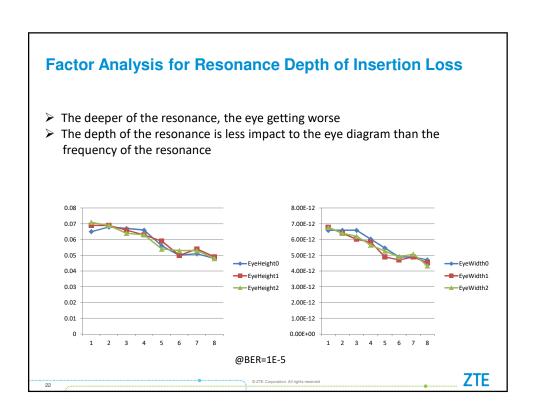

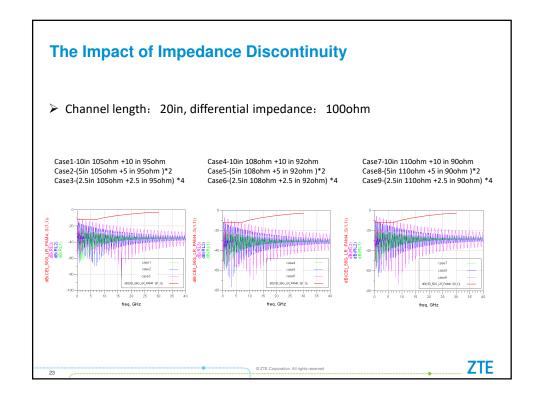

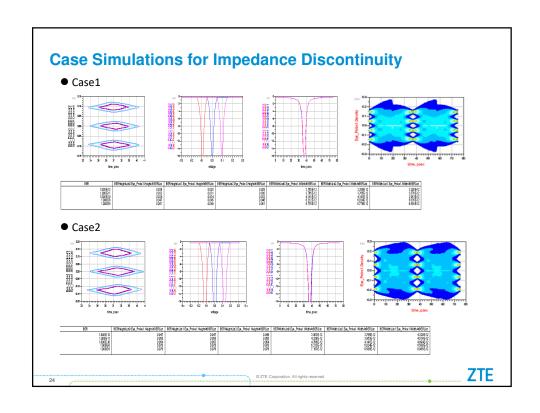

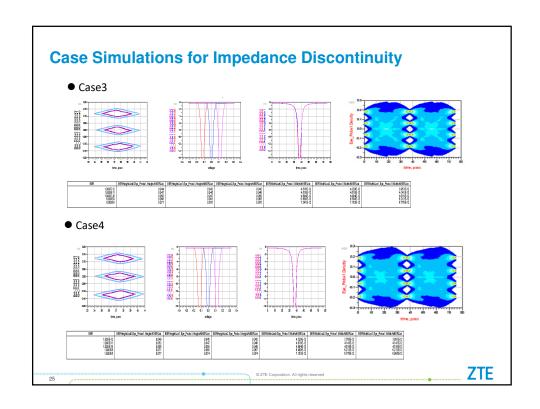

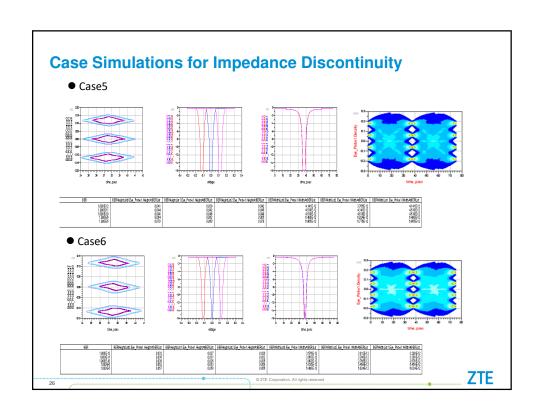

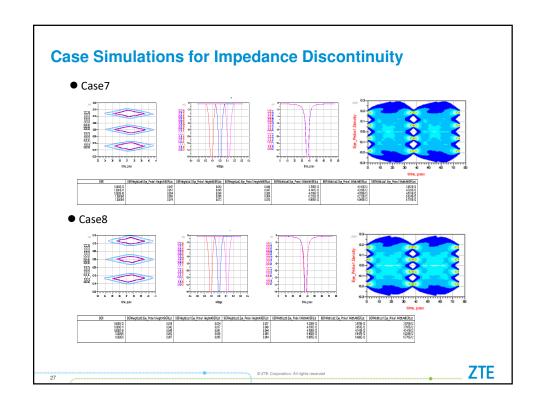

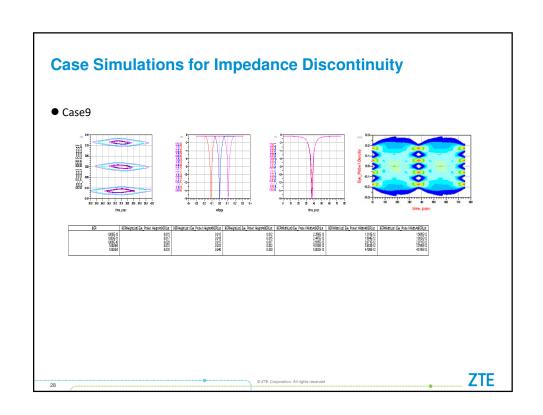

#### **Factor Analysis for Impedance Discontinuity** > The diagrams including 3 valleys and the depth is greater in turn - The impedance fluctuations of the signal channel affect the EyeHeight more than the EyeWidth - Common impedance tolerance +/-10% is not acceptable in the 56G PAM4 systems - The impedance tolerance is recommend to be less than or equal to +/-8% - Reduce the discontinuity points as possible as you can 8.00E-12 0.08 7.00E-12 0.07 6.00E-12 0.06 5.00E-12 0.05 -EyeWidth0 4.00E-12 0.04 EyeHeight1 valleys EyeWidth1 3.00E-12 EyeWidth2 0.02 2.00E-12 0.01 1.00E-12 0.00E+00 1 2 3 4 5 6 7 8 9 @BER=1E-5 **ZTE**

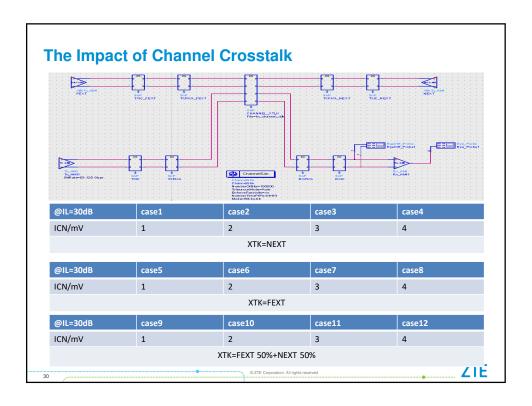

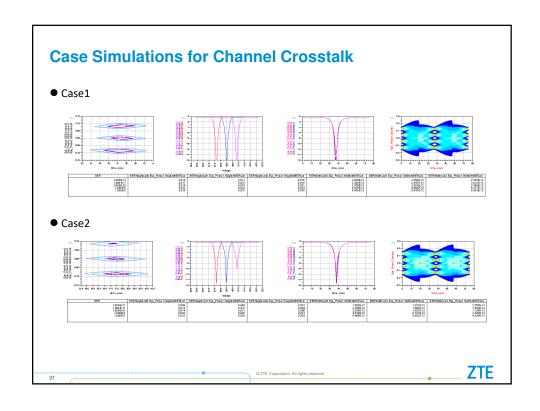

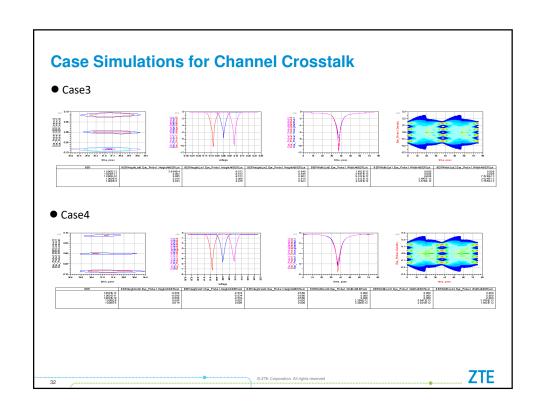

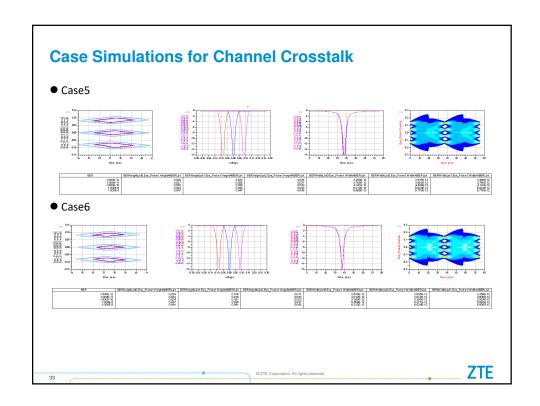

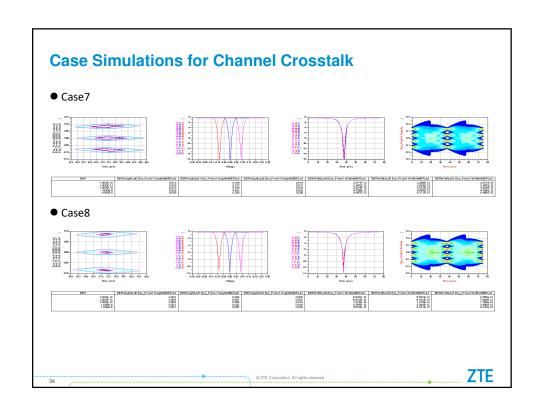

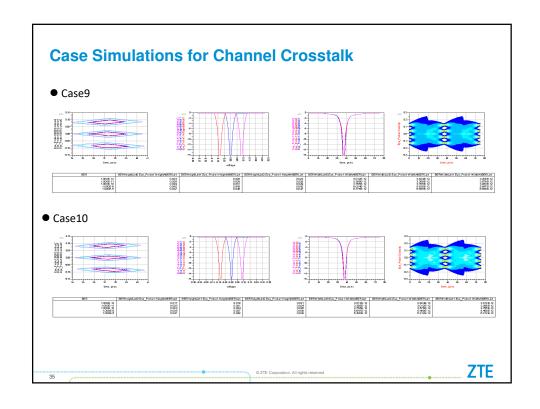

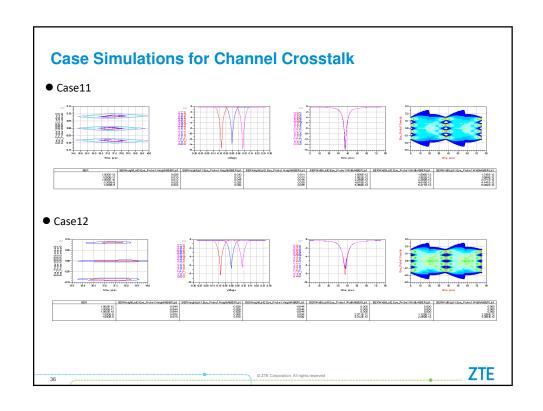

#### **Factor Analysis for Channel Crosstalk** > NEXT is more influential to the 56G-PAM4 systems than FEXT ➤ ICN limited: - To be less than 4mV for all crosstalk is NEXT - To be 4mV is OK for all crosstalk is FEXT - To be less than 4mV for half of crosstalk is FEXT and the other half of crosstalk is NEXT 8.00E-12 7.00E-12 0.05 6.00E-12 0.04 5.00E-12 4.00E-12 0.03 EyeHeight1 EyeWidth1 3.00E-12 0.02 2.00E-12 0.01 1.00E-12 0.00E+00 9 10 11 12 @BER=1E-5 **ZTE**

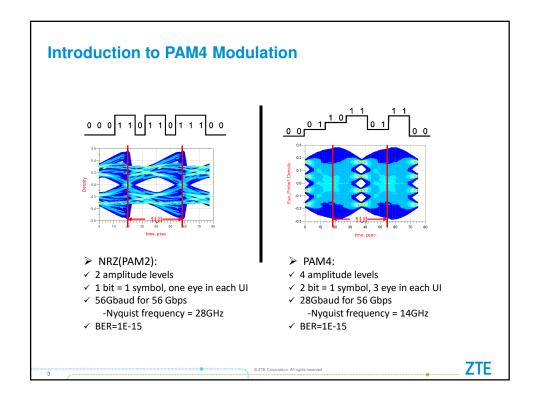

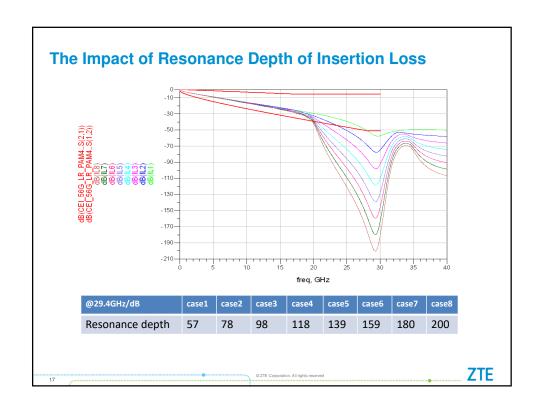

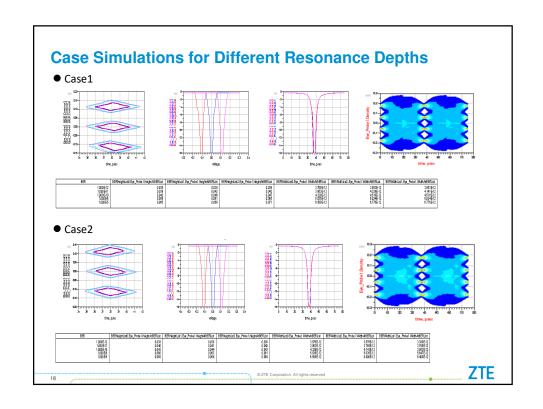

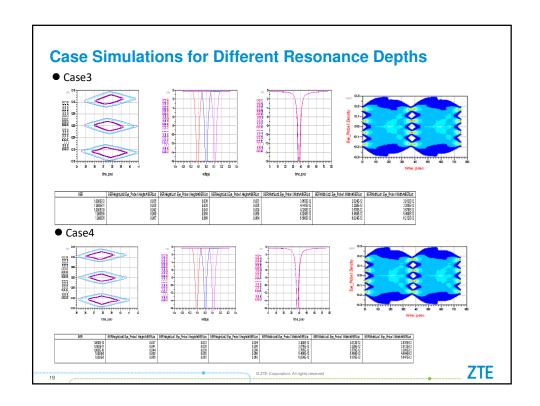

#### **Summary**

- The 56G-PAM4 standard is still in continuous update

- IBIS-AMI model works well for 56G PAM4 systems simulation, although the PAM4 modeling is new until today

- After the analysis, we obtain some conclusions about the impact of channel characteristics to the 56G-LR PAM4 systems

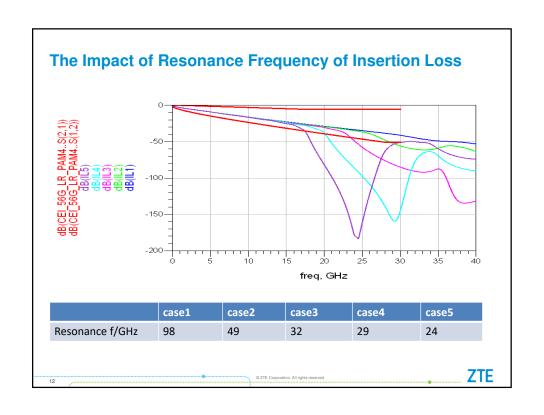

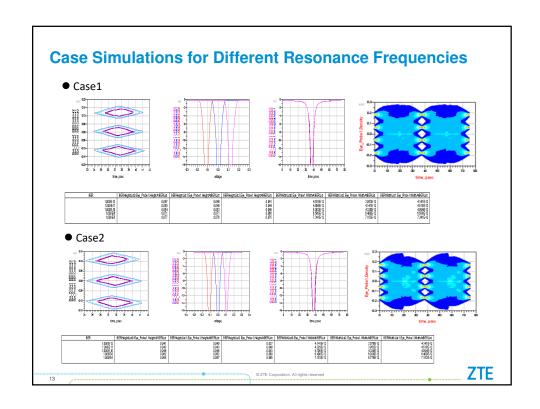

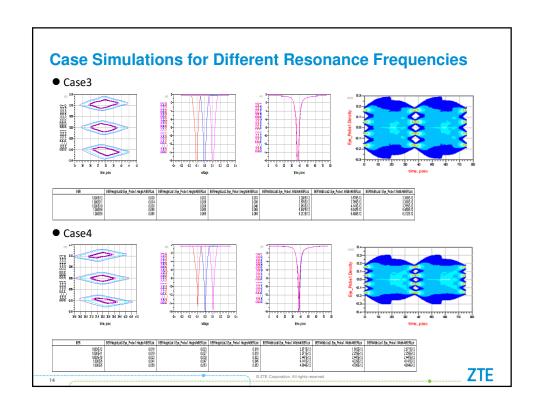

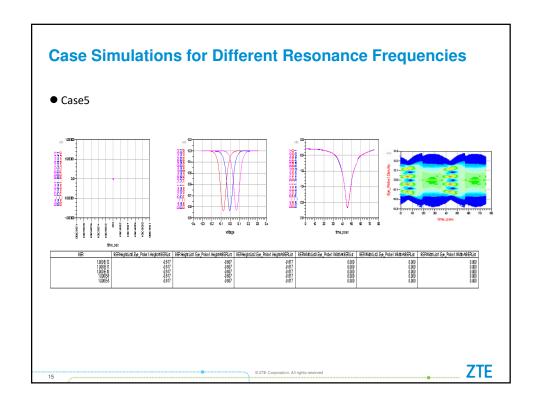

- —The IL resonance frequency should be more than 29GHz

- —The IL resonance depth should be as smaller as possible

- —The impedance tolerance is recommended to be less than or equal to +/-8%, and to reduce the discontinuity points as possible as you can

- —NEXT is playing the leading role in the crosstalk and you might pay more attention to NEXT than FEXT

- —ICN of crosstalk must be less than 4mV and is recommended to be less than  $3\mbox{mV}$

Dr. Wenliang Dai Xpeedic Technology Co., Ltd.

> Asian IBIS Summit Shanghai China November 11, 2016

Page 1

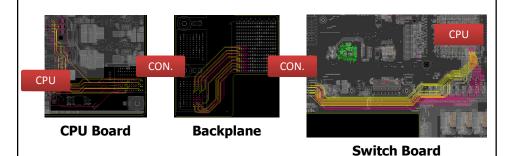

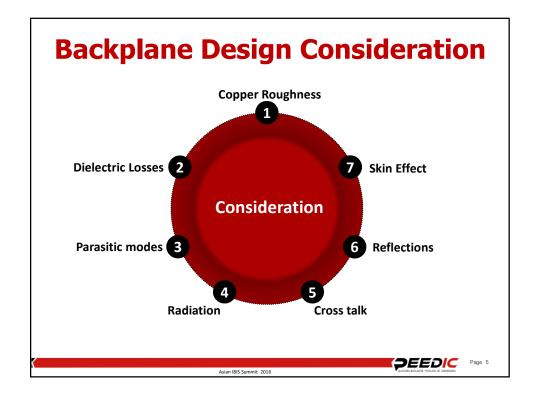

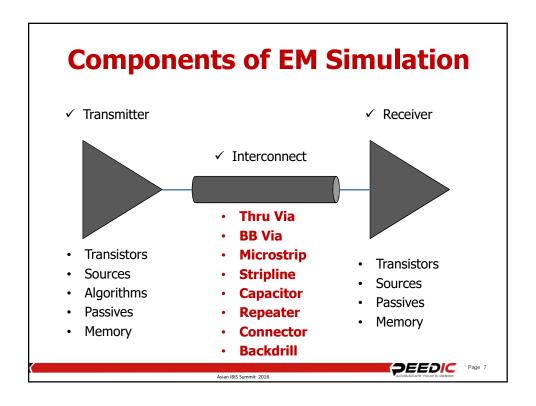

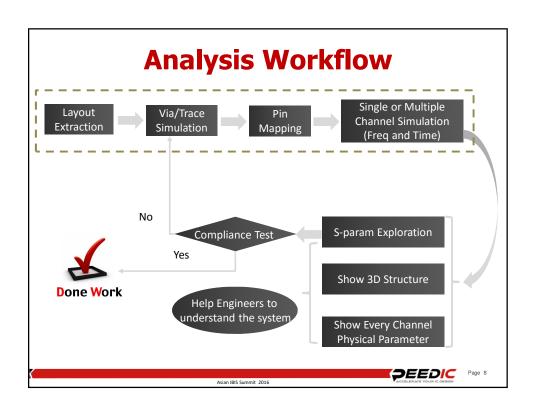

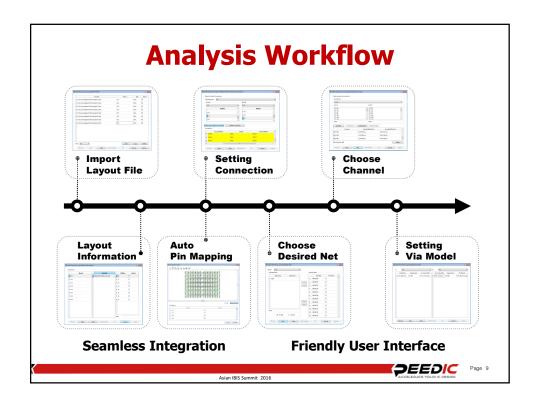

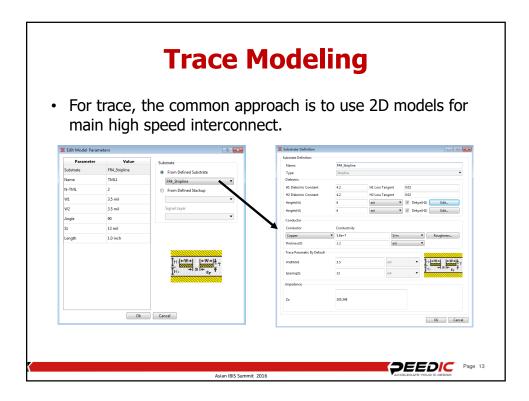

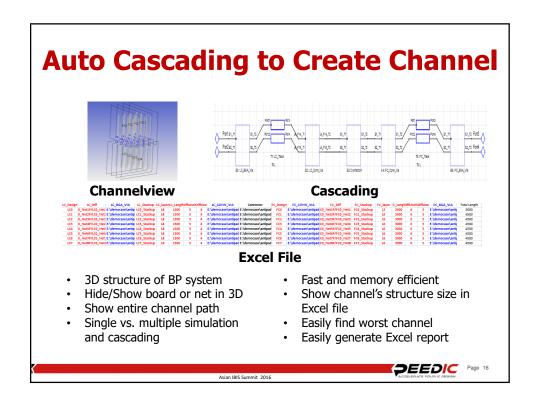

## **Outline**

- Introduction of backplane system

- Challenge to backplane system simulation

- Components of EM simulation

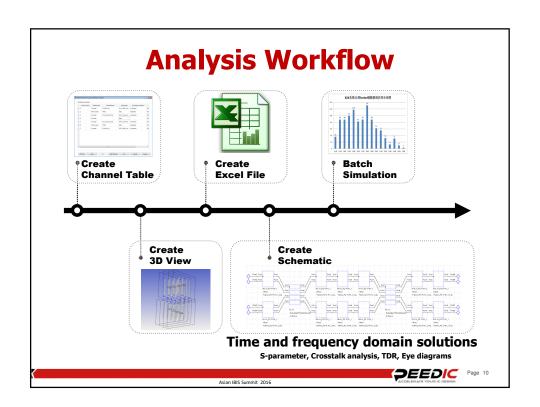

- · Analysis workflow

- Full backplane system SI simulation

- Summary

Page 2

Asian IBIS Summit 2016

## **Backplane System**

- Backplane system is used as a backbone to connect several printed circuit boards together to make up a complete system

- There are various configurations

- Traditional backplane

- Orthogonal direct

- Orthogonal mid-plane

- Coplanar

- Cable backplane

Page 3

# **Backplane System Example -- Server Board**

- · Complex PCB layout.

- Maybe system has capacitor or repeater, Engineer need to check repeater gain based on channel's loss.

Rose Formation Connector

PEEDIC

ian IBIS Summit 2016

# Challenges to Channel SI Simulation

- Reflection noise due to impedance mismatch, via, connector and other discontinuities.

- Need to capture all physical parasitic effects

- Reflection, Coupling, Delay, Freq. dependent Losses,...

- Measurements become very difficult,

- Parasitic values are small but important at high speed.

- Large number of ports for interconnects.

- EM simulation of the discontinuities is a must. However, the current flow suffers the following problems:

- Manual process to extract the via, trace, and other discontinuities

- Manual process to build all the channels

Page 6

Asian IBIS Summit 2016

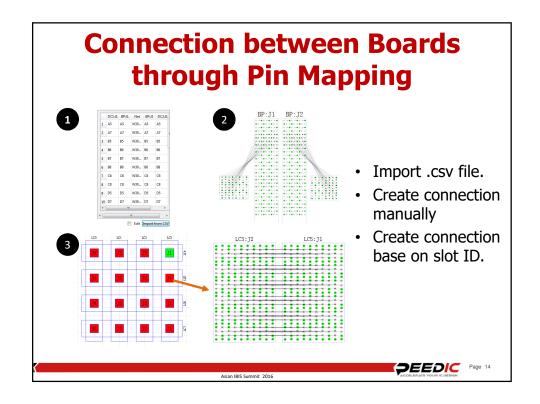

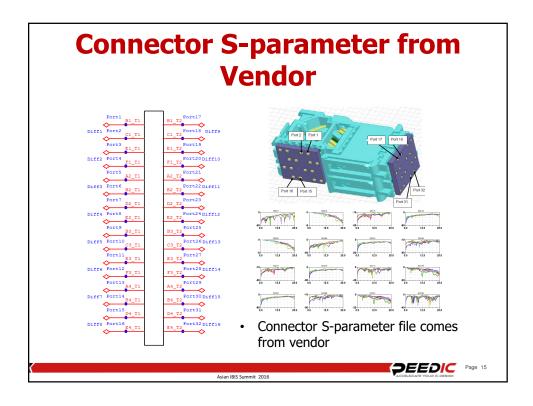

# **Post-Layout Extraction**

- · Import all the boards for the backplane system

- Extract vias and traces from layout

- Layout Files

- Model Template

- Self cleaning process

- Discrete components

- Area/Net selection

- Stackup definition

- Materials definition

- BB, Back drill definition

- Auto port definition

- Parameter/Optimization

- High flexibility

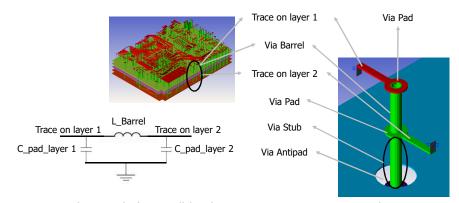

# 3D Via Modeling

- Via and ground plane will lead to parasitic capacitance and parasitic inductance.

- How to deal with a lot of via models?

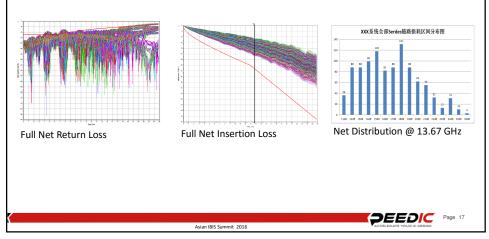

# Full Backplane SI Simulation - Frequency Domain

Full backplane SI simulation is achieved by sweeping all the channels

# **Summary**

- Passive channel modeling and simulation is essential to high speed channel design.

- Optimal channel design requires user friendly EDA tool to do layout extraction, via optimization, trace simulation, S-parameter cascading, S-parameter exploration, etc.

- Full backplane system SI simulation is achieved by sweeping all the channels with correct models.

IDIC Commit 2016

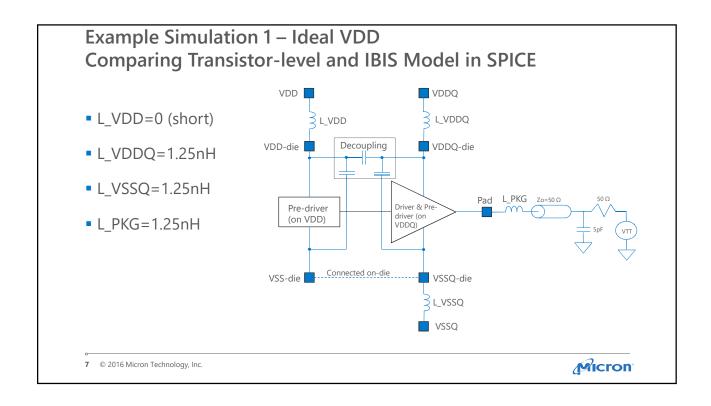

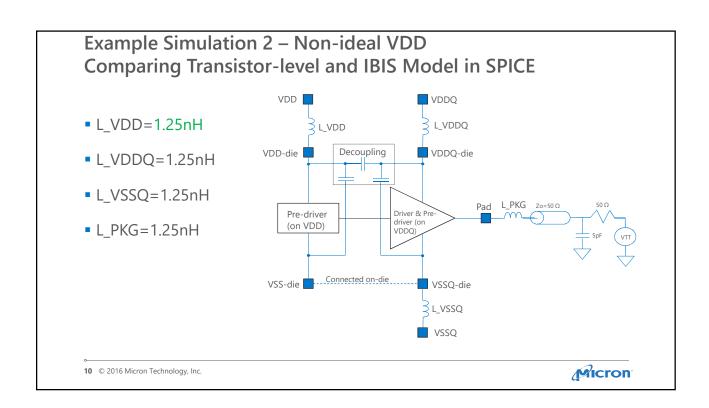

# On-Die Decoupling Model Improvements for IBIS Power Aware Models

Randy Wolff and Aniello Viscardi Micron Technology Asian IBIS Summit November 11, 2016, Shanghai, China (Previously given at the European IBIS Summit May 11, 2016 Turin, Italy)

©2016 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Statements regarding products, including regarding their features, availability, functionality, or compatibility, are provided for informational purposes only and do not modify the warranty, if any, applicable to any product. Drawings may not be to scale. Micron. the Micron logo, and all other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.

#### **Outline**

- IBIS Power-aware modeling overview

- On-die Decoupling models

- Multi-port Decoupling models

- Example Simulations

- Conclusions

2 © 2016 Micron Technology, Inc.

### **IBIS Power-aware Modeling Overview**

Power Integrity modeling uses [Composite Current], [ISSO PU], [ISSO PD] and an IBIS-ISS on-die decoupling circuit model

Decoupling model external to IBIS currently

L\_byp - Bypass current

L\_pre - Pre-Driver current

L\_cb - Crow-bar current

L\_term - Termination current (optional)

L\_VDDQ - On-die inductance of I/O Power

R\_VDDQ - On-die resistance of I/O Power

L\_GND - On-die inductance of Ground

R\_GND - On-die inductance of Ground

R\_GND - On-die resistance of Ground

C\_p+b - Bypass + Parasitic Capacitance

ESR - Equivalent Series Resistance for on-die Decap

ESL - Equivalent Series Inductance for on-die Decap

Pre-Driver ISSQ PU POWER Clamp

Circuit Issq Powered by VDDQ

\* Image from IBIS 6.0 Specification

\* Image from IBIS 6.0 Specification

3 © 2016 Micron Technology, Inc.

### **On-die Decoupling Models**

- SPICE model may have pre-driver circuits on separate power supplies

- May be one common ground ondie

- Decoupling model could include VDDQ, VSSQ, VDD, VSS

- What is needed for IBIS to correlate with SPICE?

4 © 2016 Micron Technology, Inc.

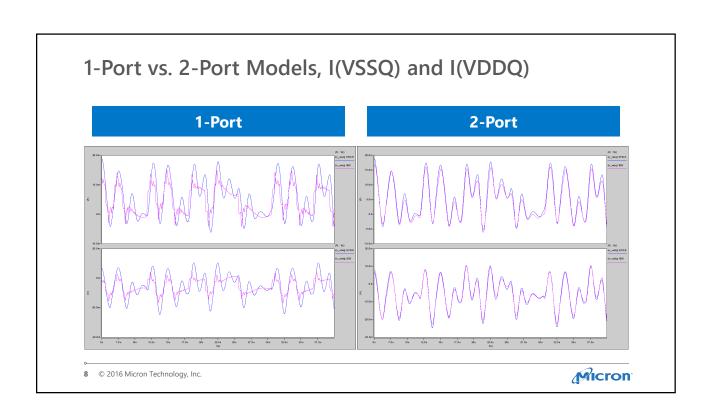

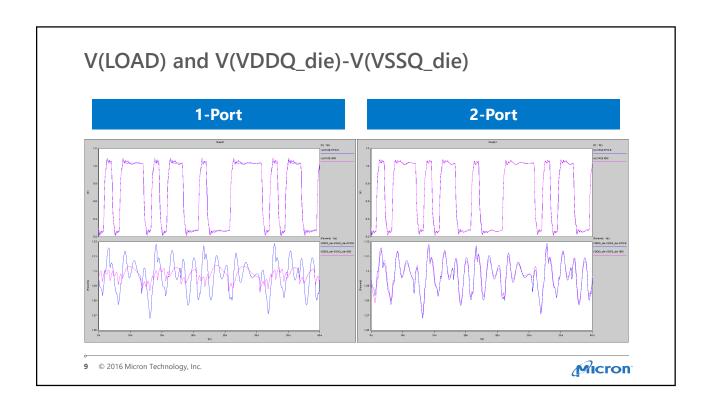

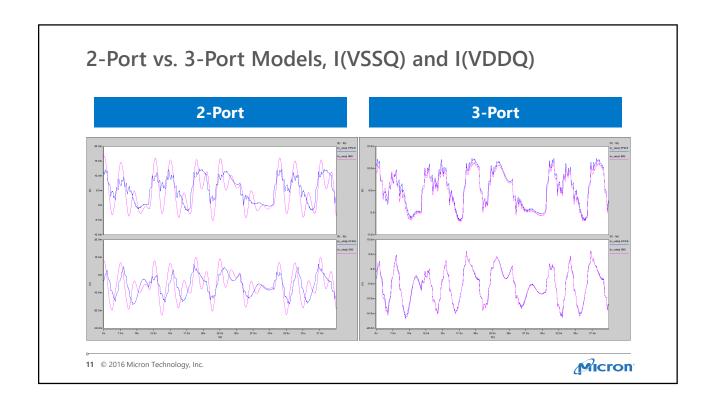

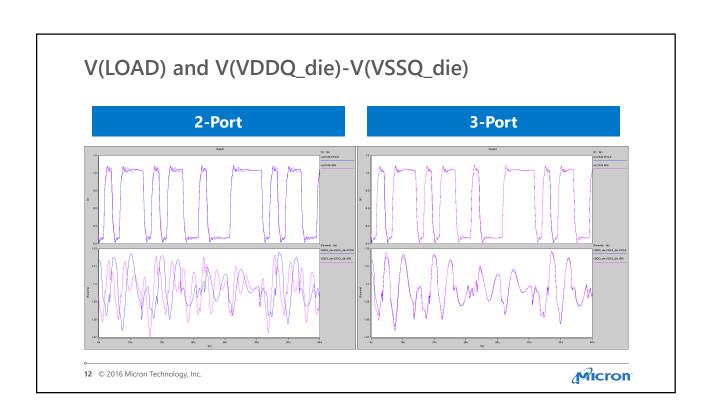

#### **Multi-port Decoupling Models**

- Decoupling circuits may contain proprietary modeling equations or process data

- A non-proprietary model can be an S-parameter or a broadband SPICE macromodel (of the S-parameter characterization)

- S-parameter port options

- 1-port: VDDQ with VSSQ reference

- 2-port: VDDQ, VSSQ, with 0 reference

- 3 or [4] port: VDDQ, VSSQ, VDD, [VSS], with 0 reference

5 © 2016 Micron Technology, Inc.

### **SPICE Setup Examples for Decoupling Model Creation**

- Buffer Instance in Hi-Z state:

- Xbuff ... VDDQ\_die VSSQ\_die ... Buffer\_name

- Port Definition:

- Single Port

- P1 VDDQ\_die VSSQ\_die port=1 Z0=50 DC VDDQ

- Multi Port

- P1 VDDQ\_die 0 port=1 Z0=50 DC VDDQ

- P2 VSSQ\_die 0 port=2 Z0=50 DC 0

- AC Analysis

- .lin sparcalc=1 filename='s\_model.sNp' format=touchstone dataformat=ma freqdigit=10 spardigit=10

- .ac dec 100 1 10e12

- 6 © 2016 Micron Technology, Inc.

#### **Conclusions**

- A 2-port S-parameter (3-terminal macro-model) for on-die decoupling is a better model than a 1-port model for power-aware simulations.

- This solution requires use of node 0 in the decoupling model.

- Correlating to a SPICE simulation that includes non-ideal supply connections to pre-driver circuits requires extra ports for non-ideal supplies in the decoupling model.

- A multi-port decoupling model is most versatile. Unused ports not connected to a package model should be connected to 0.

- The new IBIS Interconnect BIRD will allow the IBIS-ISS decoupling model to be connected properly to the package model.

13 © 2016 Micron Technology, Inc.

# IBISCHK6 V6.1.3 and Executable Model File Checking

Bob Ross, Teraspeed Labs bob@teraspeedlabs.com

Asian IBIS Summit Shanghai, China November 11, 2016

Copyright 2016 Teraspeed Labs

0 1

#### Goals and Contents

New ibischk6 V6.1.3 executables available at the same location:

www.ibis.org/ibischk6/

- Fixes 7 bugs

- Differences (new ibischk6 file names)

- New executable model file checking per BUG179 enhancement for [Algorithmic Model] Executable lines

- Source code quality assurance tests

- Some limitations

Copyright 2016 Teraspeed Labs

•2

# New BUGs 174-180 Fixed www.ibis.com/bugs/ibischk/

|     | Error with Legal List Tip in Reserved Parameters with Format List        | Mike LaBonte, Signal Intergrity Software (SiSoft)                          |

|-----|--------------------------------------------------------------------------|----------------------------------------------------------------------------|

|     | DLL SO Checking and Functional Existence and<br>Platform Information     | Mike LaBonte, SiSoft; Bob Ross, Teraspeed Labs; Lance Wang, IO Methodology |

|     | Error with Same Platform Compiler Bits for Rx and Tx of I/O* in IBIS-AMI | Michael Schaeder, Zuken; Bob Ross, Teraspeed Labs                          |

|     | Empty [Node Declarations] Stops Parser Completion                        | Arpad Muranyi, Mentor Graphics; and Bob Ross, Teraspeed Labs               |

| 176 | [External Model] Error Not Issued for Ports List<br>With Undeclared Port | Arpad Muranyi, Mentor Graphics; and Bob Ross, Teraspeed Labs               |

|     | Incorrect Model References Through [Model Selector] Not Reported         | Walter Katz, SiSoft                                                        |

|     | File Not Found Line Printed Under Some Operating<br>Systems              | Mike LaBonte, SiSoft and Bob Ross, Teraspeed Labs                          |

Copyright 2016 Teraspeed Labs

•3

### New Names for ibischk6

- Command line operation:

- Windows:

o ibischk6\_32.exe (versus ibischk6.exe)

o ibischk6\_64.exe (versus ibischk6.exe)

• Linux (Ubuntu):

ibischk6\_32 (versus ibischk6)ibischk6\_64 (versus ibischk6)

- Used for source code quality assurance tests per BUG179

- Macintosh osx\_32, osx\_64 (also uploaded), but not part of source code release

Copyright 2016 Teraspeed Labs

## New Command Line Based on ibischk6 Name

Example: ibischk6\_32.exe → "ibischk6\_32" command

# Can Rename ibischk6 File (Examples Below)

- ibischk6.exe as in earlier versions for "ibischk6" command

- ibischk613\_32.exe showing version and bits detail for "ibischk613\_32" command

- Etc. the new ibischk6 file name shows up in the Usage: lines, as shown on previous slide

Copyright 2016 Teraspeed Labs

• 6

## Syntax and Notation Related to BUG179

Under [Algorithmic Model] Executable, Executable\_Rx and Executable\_Tx lines have this information:

Platform\_Compiler\_Bits File\_Name Parameter\_File

- Platform is operating system such as Linux, Windows

- Bits is 32 or 64 for common platforms

- File\_Name is "executable model file" name such as abc.dll or abc.so

- · Parameter\_File is the .ami file

Copyright 2016 Teraspeed Labs

. 7

## Testing and Executable Combinations

- 32-bit and 64-bit operating system, ibischk6\_\* and executable model files are done consistent with the platform operating system

- Ibischk6\_32 will work on 64-bit platforms, but will load and test 32 bit executable model files

- Specification does not impose a requirement, but internal Windows requires executable names with at least a dot "."

- Message will give the recommended (but not required) extension

Copyright 2016 Teraspeed Labs

## bug179-1.ami Full Function Existence Checking

Copyright 2016 Teraspeed Labs

• 9

## **Function Existence Testing**

Each DLL/SO file must contain code symbols for exported functions in one of four possible combinations:

- A. Case 1: Executable model file has AMI\_Init, AMI\_GetWave and AMI\_Close. (IBIS 5.0 and above)

- B. Case 2: Executable model file has AMI\_Init and AMI\_Close. (IBIS 5.0 and above)

- C. Case 3: Executable model file has AMI\_Resolve, AMI\_Resolve\_Close, AMI\_Init, AMI\_GetWave and AMI\_Close. (IBIS 6.0 and above)

- D. Case 4: Executable model file has AMI\_Resolve, AMI\_Resolve\_Close, AMI\_Init and AMI\_Close. (IBIS 6.0 and above)

#### Test file names:

: noicgr No "C" combinations above and below

A: icg AMI\_Init, AMI\_Close, AMI\_GetWave

B: ic AMI\_Init, AMI\_Close

C: icgr AMI\_Init, AMI\_Close, AMI\_GetWave, AMI\_Resolve, AMI\_Resolve\_Close

D: icr AMI\_Init, AMI\_Close, AMI\_Resolve, AMI\_Resolve\_Close

Copyright 2016 Teraspeed Labs

# Some Tests for ibischk6\_32.exe when Checked with bug179-1.ami

```

| Normal case: GetWave and ResolveExists return true

Executable Windows_1_32 noicgr_32.dll

bug179-1.ami ← 5 Errors

bug179-1.ami ← 3 Errors

Executable Windows_2_32 ic_32.dll

Executable Windows_3_32 icq_32.dll

bug179-1.ami ← 2 Errors

bug179-1.ami ← Good

Executable Windows_4_32 icgr_32.dll

bug179-1.ami ← 1 Error

Executable Windows_5_32 icr_32.dll

bug179-1.ami ← Executable

Executable Windows_6_64 noicgr_64.dll

bug179-1.ami lines for 64-bit

Executable Windows_7_64 ic_64.dll

bug179-1.ami Windows lines

Executable Windows_8_64 icg_64.dll

bug179-1.ami not checked

Executable Windows_9_64 icgr_64.dll

Executable Windows_10_64 icr_64.dll

bug179-1.ami

```

#### Lines 112 to 121

Copyright 2016 Teraspeed Labs

•11

## Partial Report for ibischk6\_32.exe with New Error Codes

```

E4702 (line 112) - Code file noicgr_32.dll does not contain required AMI_Init() function E4703 (line 112) - Code file noicgr_32.dll does not contain required AMI_Close() function E4704 (line 112) - Code file noicgr_32.dll does not contain AMI_GetWave() function, required because GetWave_Exists=True in AMI file bug179-1.ami

E4705 (line 112) - Code file noicgr_32.dll does not contain AMI_Resolve() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4706 (line 112) - Code file noicgr_32.dll does not contain AMI_Resolve_Close() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4704 (line 113) - Code file ic_32.dll does not contain AMI_GetWave() function, required because GetWave_Exists=True in AMI file bug179-1.ami

E4705 (line 113) - Code file ic_32.dll does not contain AMI_Resolve() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4705 (line 113) - Code file ic_32.dll does not contain AMI_Resolve_Close() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4705 (line 114) - Code file ic_32.dll does not contain AMI_Resolve() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4706 (line 114) - Code file ic_32.dll does not contain AMI_Resolve() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4706 (line 114) - Code file ic_32.dll does not contain AMI_Resolve() function, required because Resolve_Exists=True in AMI file bug179-1.ami

E4706 (line 116) - Code file ic_32.dll does not contain AMI_Resolve_Close() function, required because Resolve_Exists=True in AMI file bug179-1.ami

```

#### Line 115 is Good (0 Errors):

Executable Windows 4 32 icgr 32.dll bug179-1.ami

Copyright 2016 Teraspeed Labs

## Summary for Platforms/Bits Test for Full Test Case

```

.. Status of [Algorithmic Model] Executables for Windows 32:

icr_64.dll:

Windows 64:

Not Checked

Windows 64:

icar 64.dll:

Not Checked

icg_64.dll:

Windows 64:

ic_64.dll:

Windows 64:

Not Checked

icr_32.dll:

Windows 32:

Checked

icgr_32.dll:

Windows 32:

Checked

icg_32.dll:

Windows 32:

ic_32.dll:

noicgr_64.dll:

Windows 32:

Checked

Windows 64:

Not Checked

icr_32.dl1:

Windows 64:

Not Checked

icgr_32.dll:

Windows 64:

Not Checked

icg_32.dll:

Windows 64:

Not Checked

ic_32.dll:

Windows 64:

Not Checked

noicgr_32.dll:

Windows 64:

Not Checked

icr_64.dll:

Windows 32:

Checked, has platform issue

icgr_64.dll:

icg_64.dll:

Checked, has platform issue

Checked, has platform issue

Windows 32:

Windows 32:

Windows 32:

Checked, has platform issue

noicgr_64.dll:

noicgr_32.dll:

Windows 32:

Checked, has platform issue

Windows 32:

Checked

```

Copyright 2016 Teraspeed Labs

•13

## Summary for Platforms/Bits Test for Full Test Case (Continued)

```

icr_64.so:

Linux 64:

Not Checked

icar 64.so:

Linux 64:

Not Checked

icg_64.so:

Linux 64:

Not Checked

ic_64.so:

Linux 64:

Not Checked

icr_32.so:

Linux 32:

Not Checked

icgr_32.so:

Linux 32:

Not Checked

icg_32.so:

Not Checked

ic_32.so:

Linux 32:

Not Checked

noicgr_64.so:

Linux 64:

Not Checked

icr_32.so:

Linux 64:

Not Checked

icgr_32.so:

Linux 64:

Not Checked

icg_32.so:

ic_32.so:

Linux 64:

Not Checked

Linux 64:

Not Checked

Linux 64:

noicgr_32.so:

icr_64.so:

Linux 32:

Not Checked

icgr_64.so:

Linux 32:

Not Checked

icg_64.so:

Linux 32:

Not Checked

Linux 32:

noicgr_64.so:

Linux 32:

Not Checked

noicgr 32.so:

Linux 32:

Not Checked

... This IBISCHK6 executable supports Windows 32 bit only

```

Errors : 28

File Failed

Copyright 2016 Teraspeed Labs

### **Status Report Lines**

- Checked

- Not checked

- · Checked, has platform issue

- Platform bits different than operating system platform Bits

- Executable model file does not have all or so extension

- Ibischk6\_32 cannot load 64-bit executable model files and visa versa

- "... This IBISCHK6 executable supports Windows 32 bit only"

- Refers to ibischk6\_32.exe used in test

Copyright 2016 Teraspeed Labs

**•**15

### Recommended Extensions

- Windows: dll

- Linux: so

- No requirement but some Windows versions require executable names with at least a dot "."

- Other messages may suggest .dll for Windows or .so for Linux)

Copyright 2016 Teraspeed Labs

### Limits and Issues

- ibischk6\_32 works on 64-bit platforms if 32-bit executable model files load and work on the platform

- Platform name examples shown in the IBIS

Specification some may be specified in the future

- Case insensitive Windows

- Case insensitive Linux

- For unknown platform names, ibischk6 will try to load executable model file and run the functional existence test

Copyright 2016 Teraspeed Labs

• 17

### **Future and Conclusion**

- No reference IBIS-AMI waveform checking

- Some commercial vendors offer reference IBIS-AMI waveform checking

- ibischk6 V6.1.3 valuable for function existence testing for Reserved\_Parameters documented in the .ami file

Copyright 2016 Teraspeed Labs

## TOUCHSTONE CONVERSION WRAPPER

ASIAN IBIS SUMMIT SHANGHAI CHINA NOVEMBER 11, 2016

Anders Ekholm

### **AGENDA**

- Using TSCHK2 for touchstone format conversion

- Problem statement

- > Fixing the problem using a Wrapper

- A Perl wrapper

- > Solves the current issue of losing comments

- > Wrapper avaliable on the IBIS webpage.

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 2 (10)

## USING TSCHK2 FOR TOUCHSTONE FORMAT CONVERSION

The touchstone checker TSCHK2 from IBIS Open Forum can also be used for converting Touchstone models (TS) to Touchstone 2 model format.

To do so use the option -canonical e.g.:

Tschk2 –canonical ts1.s4p > ts2.s4p

This will fit the data into the TS2 model format, but will not add any extra data.

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 3 (10)

### PROBLEM STATEMENT

However, doing so strips out any comments from the original touchstone file e.g.,

!Murata Part Number: GRM15XR11E222KA86

!These Parameters are Measured in Series Mode Connection

! o--II--0

!Port1 Port2

! o-----0

!Operation Temp=25[C], DC Bias Voltage=0[V]

| Freq. Start=300[kHz] Stop=6000000[kHz] 401[Steps]

# Hz S RI R 50

!Freq.(Hz)

S 11(Real)

S 11(Imag)

S 21(Real)

S 21(Imag)

S 12(Imag)

S 12(Imag)

S 22(Imag)

300000

0.8473370

-0.3552390

0.1526630

0.3552390

0.1526630

0.3552390

0.8473370

-0.3552390

307520

0.8409069

-0.3612905

0.1590931

0.3612905

0.1590931

0.3612905

0.8409069

-0.3612905

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 4 (10)

### PROBLEM STATEMENT

#### Becomes:

! Touchstone data file [Version] 2.0 # Hz S RI R 50 [Number of Ports] 2 [Two-Port Data Order] 12\_21 [Number of Frequencies] 401

#### [Network Data]

| ! freq<br>S22im     | S11re                   | S11im      | S12re    | S12im    | S21re | S21im     | S22re     |

|---------------------|-------------------------|------------|----------|----------|-------|-----------|-----------|

| 300000<br>0.847337  | 0.847337<br>-0.355239   | -0.355239  | 0.152663 | 0.355239 | 0     | .152663   | 0.355239  |

| 307520<br>0.8409069 | 0.8409069<br>-0.3612905 | -0.3612905 | 0.159093 | 0.36129  | 05    | 0.1590931 | 0.3612905 |

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 5 (10)

## FIXING THE PROBLEM USING A WRAPPER

So to mitigate the problem without having to change TSCHK2, I wrote a small Perl wrapper.

Wrapper is a software code that sort of wraps around another code in this case the tschk2.

- The Perl wrapper will take the file to convert as input. It will read all the comments before the data and all the comments after the data and save those in memory.

- >lt will then run the tschk2 on the file to convert and save the result in temp.ts2

- Then it will read the temp.ts2 file and reinsert the comments into the output file xxxxx.snp

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 6 (10)

### A PERL WRAPPER

#### #!/usr/bin/per

#TS1toTS2 is a small wrapper to IBIS Open Forums tschk2, since using the IBIS Open Forums converting feature to convert models will not retain comments from the original file

#So this wrapper will read and save the comments run tschk2 and convert the model, after this it will read the converted model and add the comments

#and output that as the converted file. It will use the same file name for the output and the old touchstone file will be saved as .TS1

#It will only convert touchstone files into touchstone 2 files.

#It is a command line tool. It implemented as a quick & dirty solution so feel free to enhance it if you need to.

#This section will pick up the ts filename from the command line if missing give you an error

\$options=join " ".@ARGV;

if (\$ARGV=~/-h/)

......

#read all the comments in the original file

open FIL,"<\$file" or die "n\nCan't open file: \$file";

.....

#Run tschk to convert file ....... system "copy \$file \$newfile";

# add the comments in the final model.

open FIL,"<temp.ts2" or die "\n\nCan't open file: temp.ts2";

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 7 (10)

## SOLVES THE CURRENT ISSUE OF LOSING COMMENTS

This solves our current problem of losing information from the original model when converting it into TS2.

We are trying to standardize on our S-parameter models in TS2 format.

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 8 (10)

## WRAPPER AVAILABLE ON THE IBIS WEBPAGE

The wrapper has been made available on the IBIS Open Forum webpage.

Please feel free to use it.

It is distributed in source code format so you can adapt it to your specific needs.

http://www.ibis.org/tschk2/

Touchstone conversion wrapper | Asian IBIS Summits 2016 | Anders Ekholm | 2016-10-25 | Page 9 (10)