# How to Fix DDR4 Signal Integrity Issue about "Pin" and "Die"

Meng Liqiang, Zhu Shunlin Meng.liqiang@zte.com.cn; zhu.shunlin@zte.com.cn

0000

Asian IBIS Summit, Shanghai, China, November 14, 2018

**Overview**

Summary

"Pin" and "Die" Specification in IBIS Model

Comparative Analysis of two Simulation Cases

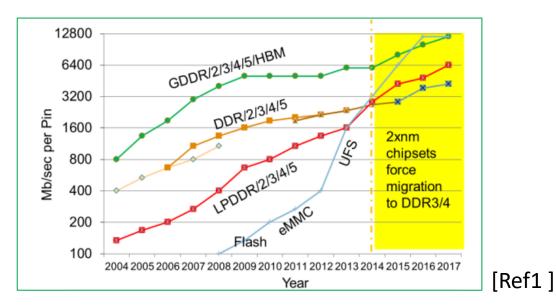

#### **Overview DDRx Evolution Trend**

JEDEC Standards for DDRx

- DDR4 JESD79-4B JUNE 2017

- DDR5 publication is forecasted for 2018 [Ref2]

DDRx Speed

- DDR4 3200MT/S

- DDR5 reach up to 6400MT/S

DDRx Model

- DDR4 [IBIS ver] 5.1

- ➢ DDR5 [IBIS ver] ?

Ref1: DDR4/LPDDR4: A Practical Design Methodology or High-Speed Memory Systems ,April 12th, 2015, page7, Keysight, Stephen Slater, https://www.keysight.com/upload/cmc\_upload/All/HSDSeminarPaper1.pdf Ref2 :https://www.jedec.org/news/pressreleases/jedec-ddr5-nvdimm-p-standards-under-development

© ZTE All rights reserved

# Agenda

- Overview

- "Pin" and "Die" Specification in IBIS Model

- Comparative Analysis of two Simulation Cases

- Design Considerations for the Next Generation of DDR

- Summary

# [Package]& [Pin] Information in IBIS Model

- The [Package Model] data overrides the values in the [Package] keyword. Regardless, the data listed under the [Package] keyword must still contain valid data.

- Six columns for Pin can be used to override the default package values (specified under [Package]) FOR THAT PIN ONLY. When using six columns, the headers R\_pin, L\_pin, and C\_pin must be listed.[Ref3]

- Priority ranking [Package Model] > [Pin] > [Package]

| [Package]                                                                                                 | ]                  |            |               |                |            |  |

|-----------------------------------------------------------------------------------------------------------|--------------------|------------|---------------|----------------|------------|--|

| variabl<br>D =k=                                                                                          |                    | mi:<br>10  | n<br>0.00m    | max<br>300.00m |            |  |

| R_pkg                                                                                                     | 200.00m<br>2.00-10 |            |               |                |            |  |

| L_pkg                                                                                                     | 2.00nH             |            | 00nH          | 3.00nH         |            |  |

| C_pkg                                                                                                     | 1.35pF             | 1.         | 20pF          | 1.50pF         |            |  |

| [pin] s                                                                                                   | signal_name        | model_name | P pin         | L_pin          | C_pin      |  |

|                                                                                                           | DDRA_A0_A7A8       |            | 3.30E+03mOhm  | 5.33E+00nH     | 2.81E+00pF |  |

|                                                                                                           | DDRA_A10           | d4_addr    | 2.56E+03mOhm  | 4.19E+00nH     | 1.62E+00pF |  |

|                                                                                                           | DDRA_A11           | d4_addr    | 3.28E+03mOhm  | 5.16E+00nH     | 2.57E+00pF |  |

|                                                                                                           | DDRA_A12           | d4_addr    | 3.31E+03mOhm  | 5.20E+00nH     | 2.60E+00pF |  |

|                                                                                                           | DDRA A13           | d4_addr    | 1.84E+03mOhm  | 3.24E+00nH     | 1.54E+00pF |  |

| H117 1                                                                                                    | JOAR RIS           |            | 1.041.050.010 | 3.24E100III    | 1.34610000 |  |

| [Pin] signal_name model_name R_pin L_pin C_pin                                                            |                    |            |               |                |            |  |

| [Pin] signal_name model_name R_pin L_pin C_pin<br>A31 c0_ddr4_dqs_c[3]   HP_POD12_DCI_F_OUT40_IN60_PE2400 |                    |            |               |                |            |  |

| HOI CO_GGI4_GGS_C[O]   M_TODI2_DCI_F_O0140_IM00_FE2400                                                    |                    |            |               |                |            |  |

| [Package Model] Controller D                                                                              |                    |            |               |                |            |  |

| [rackage model] Controller D                                                                              |                    |            |               |                |            |  |

There may be some misunderstanding between R\_pin /L\_pin/C\_pin and R\_pkg/L\_pkg/C\_pkg when running corner simulation,Which one will the tool call?

Ref3: I/O Buffer Information Specification IBIS Version 6.1 page 21 , <u>http://ibis.org/ver6.1/ver6\_1.pdf</u>

#### [Package]& [Pin] Information in IBIS File

There may be some misunderstanding between Package typ min max in model and Slow-Weak ,Typical , Fast -Strong mode in simulation because R\_pin/L\_pin/C\_pin has only one value for specified pin, but [Package] has three different value.

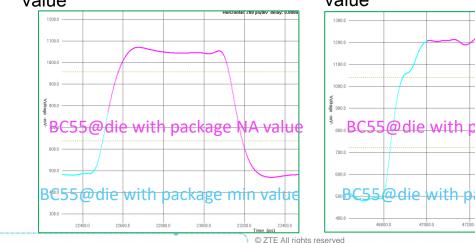

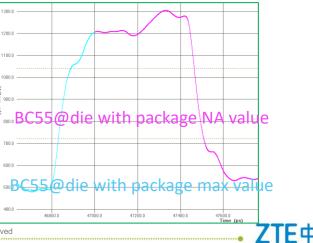

The typical (typ) column must be specified. If data for the other columns are not available, they must be noted with "NA", so three experiments show that R\_pin, L\_pin, and C\_pin only override the default package typical values. For example, experiment 2 with/without Package model under slow corner simulation, they have the same waveform.

Experiment 1 Using BC55 and BB54 pin for typical corner simulation

Experiment 2 Using BC55 for Slow corner simulation by setting Packge min wtih default and NA value

Experiment 3 Use BC55 for Fast -Strong corner simulation by setting Packge max wtih default and NA value

## Si\_location and Timing\_location

Model default loaction

- Si\_location pin

- Timing\_location pin

Modify for auto measurement

- Si\_location Die

- Timing\_location Die

#### 5 COMPONENT DESCRIPTION

Keyword:

[Component]

Required:

Yes

Description:

Marks the beginning of the IBIS description of the integrated circuit named after the keyword.

Sub-Params:

Si\_location, Timing\_location

*Usage Rules:* If the .ibs file contains data for more than one component, each section must begin with a new [Component] keyword. The length of the component name must not exceed 40 characters, and blank characters are allowed.

NOTE: Blank characters are not recommended due to usability issues.

Si\_location and Timing\_location are optional and specify where the Signal Integrity and Timing measurements are made for the component. Allowed values for either subparameter are "Die" or "Pin". The default location is at the "Pin".

#### Example:

[Component] 7403398 MC452 | Si\_location Pin | Optional subparameters to give measurement Timing\_location Die | location positions

| [Component]<br>Timing_locat |          | oller     |              |            |            |

|-----------------------------|----------|-----------|--------------|------------|------------|

| [Manufacturer] A            |          |           |              |            |            |

| Package Generic             |          |           |              |            |            |

| [Package]                   |          |           |              |            |            |

| variable                    | typ      |           | in           | max        |            |

| R_pkg                       | 200.00m  |           | 00.00m       | 300.00m    |            |

| L_pkg                       | 2.00nH   |           | . 00nH       | 3.00nH     |            |

| C_pkg                       | 1.35pF   | 1         | .20pF        | 1.50pF     |            |

|                             |          |           |              |            |            |

|                             | al_name  | model_nam | ∋ R_pin      | L_pin      | C_pin      |

| AM56 DDRA                   | _A0_A7A8 | $d4_addr$ | 3.30E+03mOhm | 5.33E+00nH | 2.81E+00pF |

| AN51 DDRA                   | _A10     | d4_addr   | 2.56E+03mOhm | 4.19E+00nH | 1.62E+00pF |

| AT54 DDRA                   | _A11     | d4_addr   | 3.28E+03mOhm | 5.16E+00nH | 2.57E+00pF |

| AR54 DDRA                   | _A12     | $d4_addr$ | 3.31E+03mOhm | 5.20E+00nH | 2.60E+00pF |

Ref3: I/O Buffer Information Specification IBIS Version 6.1 page 20, <u>http://ibis.org/ver6.1/ver6\_1.pdf</u>

# Agenda

- Overview

- "Pin" and "Die" Specification in IBIS Model

- Comparative Analysis of two Simulation Cases

- Design Considerations for the Next Generation of DDR

- Summary

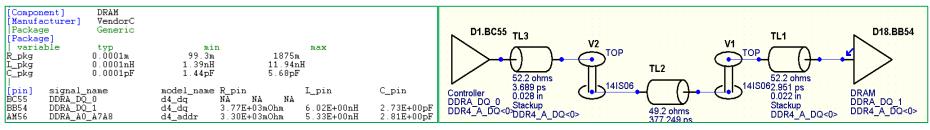

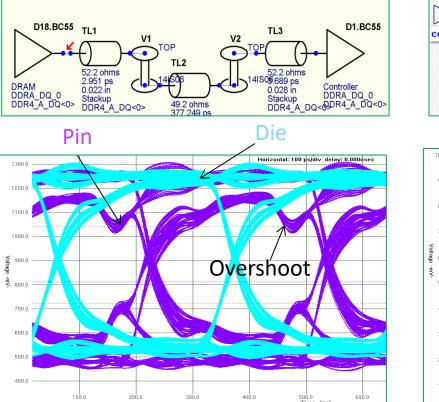

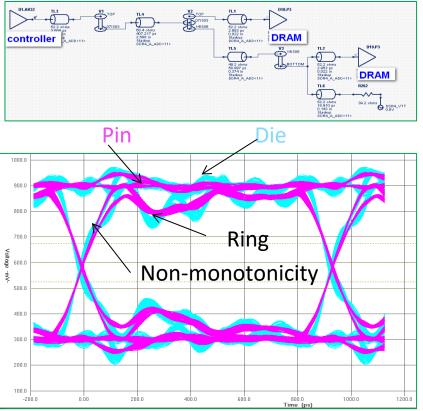

## Introduction of Two DDR4 Simulation Cases

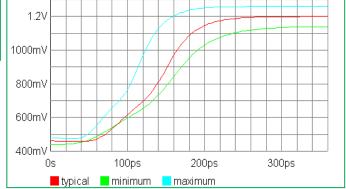

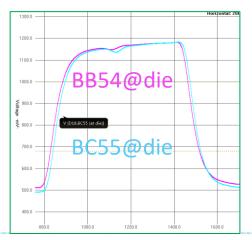

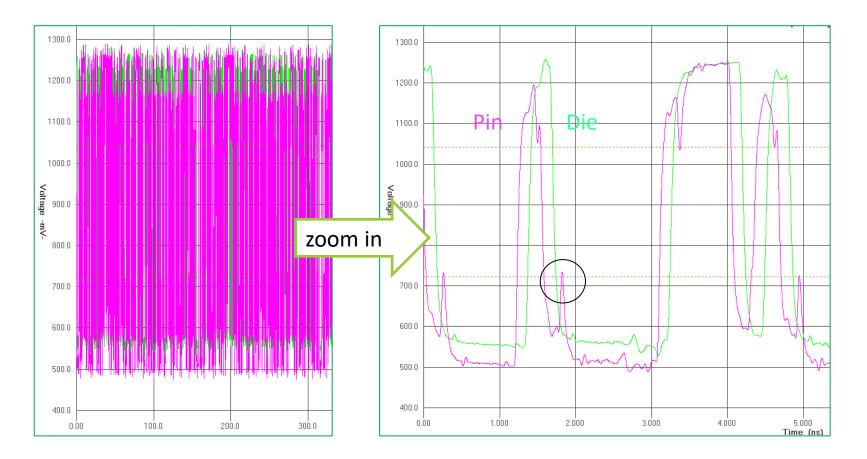

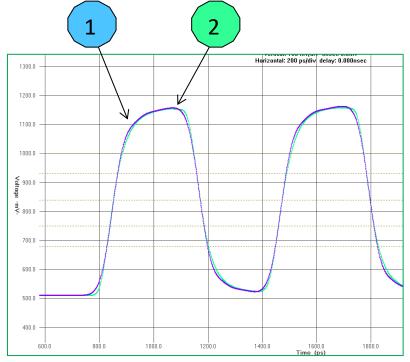

Case1: Pin VS Die

- DQ read

- Simulation @3200Mbps

- Point to Point

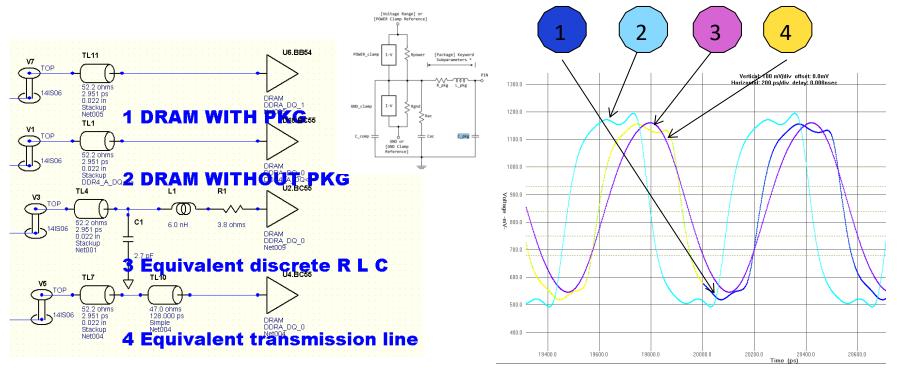

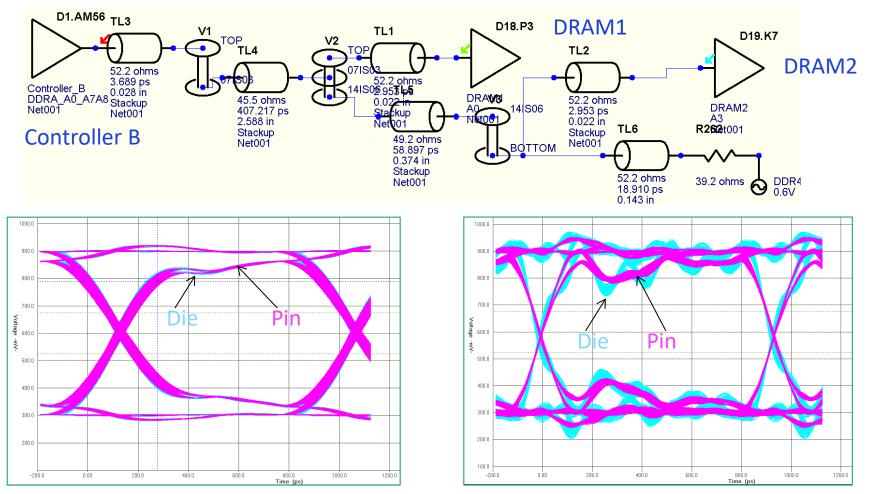

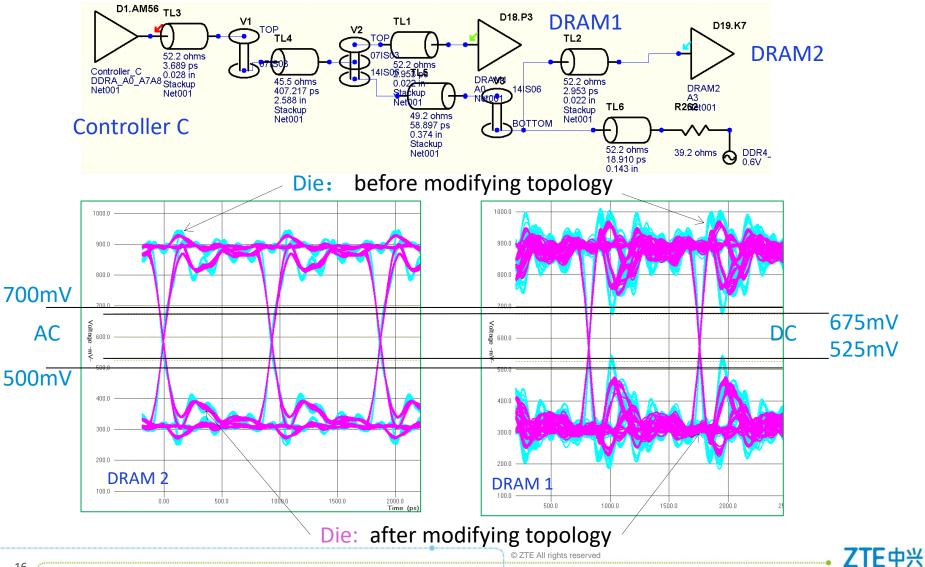

#### Case2: Pin VS Die

- > CMD

- Simulation @2133Mbps 1T mode

- T Topology

Package can cause rings and non-monotonicity when doing simulation or testing

- Simulation @3200Mbps, 1T mode

- PRBS 7

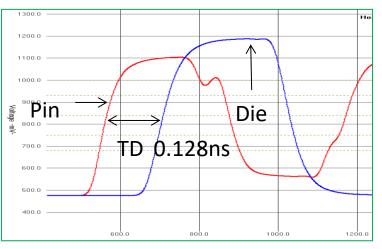

Pin Information: L\_pin and C\_pin value contribute the TD of the package

|           | in                                                                        | may                                                                                                                        |                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 200.00m 1 | 00.00m                                                                    | 300.00m                                                                                                                    |                                                                                                                                                                                                                                                                                                                         |

|           |                                                                           |                                                                                                                            |                                                                                                                                                                                                                                                                                                                         |

| 1.35pr 1  | .20pr                                                                     | I.SUPr                                                                                                                     |                                                                                                                                                                                                                                                                                                                         |

|           |                                                                           | L_pin                                                                                                                      | C_pin                                                                                                                                                                                                                                                                                                                   |

|           |                                                                           |                                                                                                                            | 2.73E+00pF<br>2.81E+00pF                                                                                                                                                                                                                                                                                                |

| d4_addr   | 2.56E+03mOhm                                                              | 4.19E+00nH                                                                                                                 | 1.62E+00pF                                                                                                                                                                                                                                                                                                              |

|           | 200.00m 1<br>2.00nH 1<br>1.35pF 1<br>me model_nam<br>d4_dq<br>7&8 d4_addr | 200.00m 100.00m<br>2.00nH 1.00nH<br>1.35pF 1.20pF<br>ne model_name R_pin<br>d4_dq 3.77E+03mOhm<br>7&8 d4_addr 3.30E+03mOhm | 200.00m         100.00m         300.00m           2.00nH         1.00nH         3.00nH           1.35pF         1.20pF         1.50pF           me         model_name R_pin         L_pin           d4_dq         3.77E+03mOhm         6.02E+00nH           7&8         d4_addr         3.30E+03mOhm         5.33E+00nH |

Verification: Set R\_pkg/L\_pkg/C\_pkg to Zero, the waveform is same between Pin and Die

| varia<br>R_pkg<br>L_pkg<br>C_pkg | ble typ<br>0.001m<br>0.001nH<br>0.001pF | min<br>  NA P<br>NA<br>NA          | max<br>VA<br>NA<br>NA |            |

|----------------------------------|-----------------------------------------|------------------------------------|-----------------------|------------|

| [pin]<br>BC55                    | signal_name<br>DDRA DQ 0                | model_name R_pin<br>d4 dq NA NA NA | L_pin                 | C_pin      |

| AM56                             | DDRA_A0_A7A8                            | d4_ddr 3.30E+03mOhm                | 5.33E+00nH            | 2.81E+00pF |

**ノート**中兴

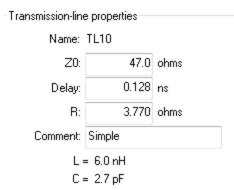

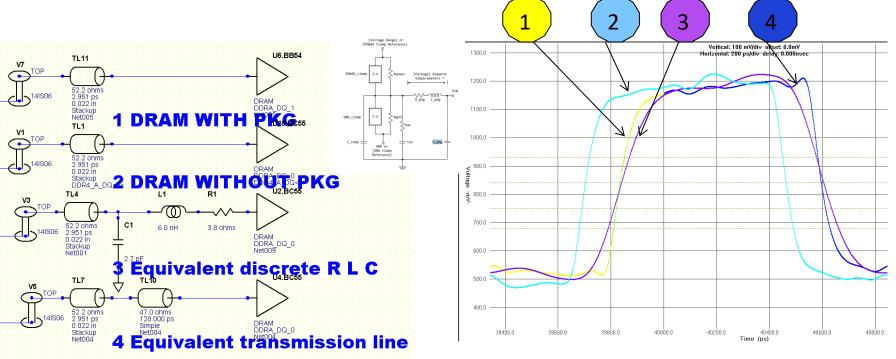

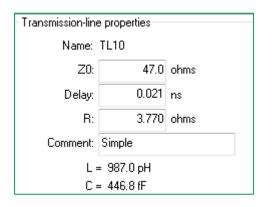

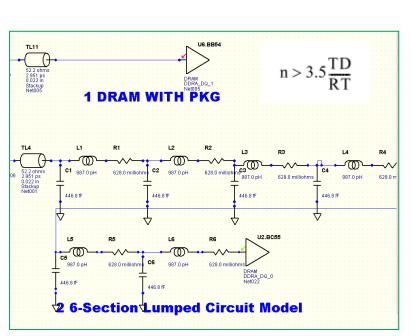

- Simulation @667Mbps

- R\_pin = 3.77mohm, L\_pin = 6.02nH, C\_pin = 2.73pF

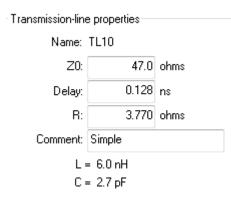

- Use transmission line TL10 matching pin parameter well

- Equivalent discrete R L C value R/L/C\_pin have Similar envelope as T LINE

- All observation points are at the die

- Simulation @3200Mbps

- Transmission line TL10 still works well

- Equivalent discrete R L C value distorts the waveform as the frequency goes up

- If a transmission line that has a time delay of TD, we wish to approximate it with an n-section lumped-circuit model

- All observation points are at the die

- Simulation @3200Mbps

- If a transmission line that has a time delay of TD and we wish to approximate it with an n-section lumped-circuit model

- Ctotal = TD/Z0 = 0.128ns/470hm = 2.7pF

- Ltotal = Z0XTD = 47\*0.128 = 6.016nH

- n > 3.5\*0.128/0.072 (20%~80% rise time) = 6

- 6-Section Lumped Circuit Model compared with the T line well

from SIGNAL AND POWER INTEGRITY-SIMPLIFIED SECOND EDITION Eric Bogatin page 305

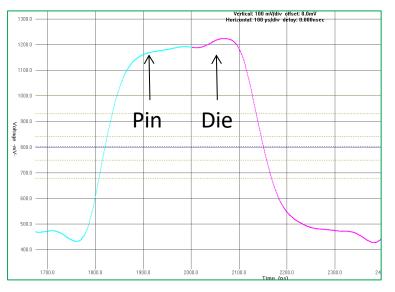

#### Measurement base the same topology with 2133Mbps DDR4 1T mode

With medium controller model

#### With fast controller model

Measurement on same topology with 2133Mbps DR4 1T mode, Controller C Unfortunately, just have one type controller mode. Topology needed adjustment.

Overview

Summary

"Pin" and "Die" Specification in IBIS Model

Comparative Analysis of two Simulation Cases

- System Designers

- ✓ Impact on DDRX when using "Low loss" and "Ultra-low-loss" materials for high speed I/O design

- ✓ Short, more reflective channel, wider lines

- ✓ Different load, DRAM number from 1 to 9, single or twin Die

- ✓ SI-PI "co-simulation"

- ✓ Full coverage for both all DDRx nets and different vendor models

- Model Creators

- ✓ [Pin] name is physical pin name A1, A2, A3, B1; Not 1, 2, 3

- ✓ Tx: FIR; Rx: CTLE, FFE, DFE for ISI

- ✓ Types of effects need to be simulated, Simultaneous Switching Noise with Power Aware

- ✓ Power Delivery (PDN) Network

- ✓ Single ended and differential signals

- EDA Tool Vendors

- ✓ Support SI-PI "co-simulation"

- ✓ Multi channels simulations

- ✓ Batch simulation

- ✓ Automatic measurement and report generation

Overview

Summary

"Pin" and "Die" Specification in IBIS Model

Comparative Analysis of two Simulation Cases

#### Summary

- The non-monotonic waveform of the pin is a common phenomenon in the test sections and simulation

- Use transmission line matching Package parameters well

- The deterioration of pin waveform over "Die" is in accordance with the expected simulation, but there are exceptions

- From system application's perspective, it is recommended that the coming DDR5 models and tools can support all the DDRx nets and SI-PI co-simulation