## Channel Simulation Over DDR4/5 and Above

Kumar Keshavan, Ambrish Varma, Ken Willis, Skipper Liang Asian IBIS Summit Shanghai, China November 1, 2019

#### cādence®

#### Two Concerns:

- As the transmission rate of memory bus goes beyond 5Gbps, besides the wellknown timing and overshoot/undershoot analysis, it requires BER prediction analysis and channel analysis

- Two additional concerns we need to face while using channel engine to deal with memory bus:

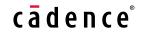

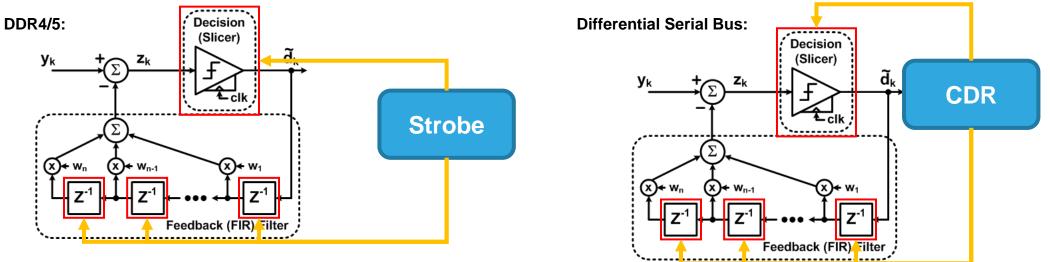

- Asymmetric rising/falling edges

Different from differential serial buses, single-ended memory buses will have non-symmetrical rising and falling edges due to the inherent difference between these two kinds of circuits

Strobes as timing reference

While the sampling clock ticks in serial bus are recovered from the signal itself by CDR, the sampling clocks or the timing references in memory bus will be the strobes rather than any recoveries

## Asymmetric Rising and Falling Edges

© 2019 Cadence Design Systems, Inc. All rights reserved.

#### Circuits

cādence°

© 2019 Cadence Design Systems, Inc.

4

#### Overview

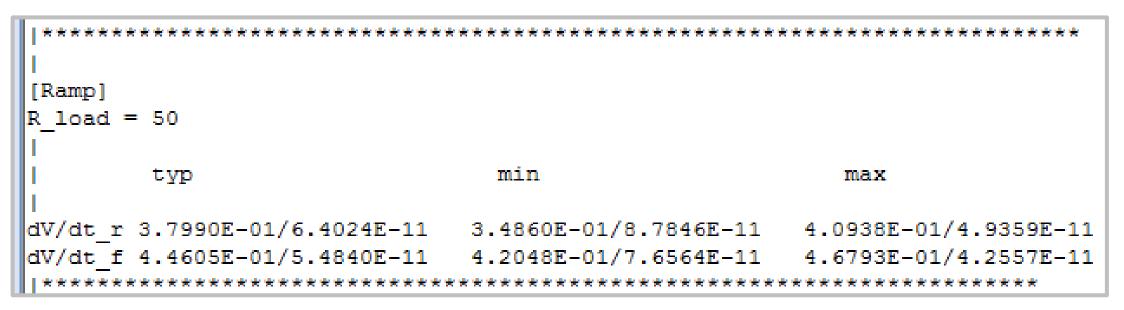

- As channel simulation and IBIS-AMI modeling methods are adapted from serial link to DDR interface analysis, we encounter IBIS I/O models with asymmetric rising and falling edges

- This is different from the highly symmetric drivers we typically encounter with serial link analysis

- Traditional single-step response methods for impulse response generation may not reproduce circuit simulation results accurately enough

- These slides show how an EDA tool can handle this (without changes to the IBIS specification)

- All cases use <u>Micron</u>'s **y11a.ibs** file for 8Gbps DDR5

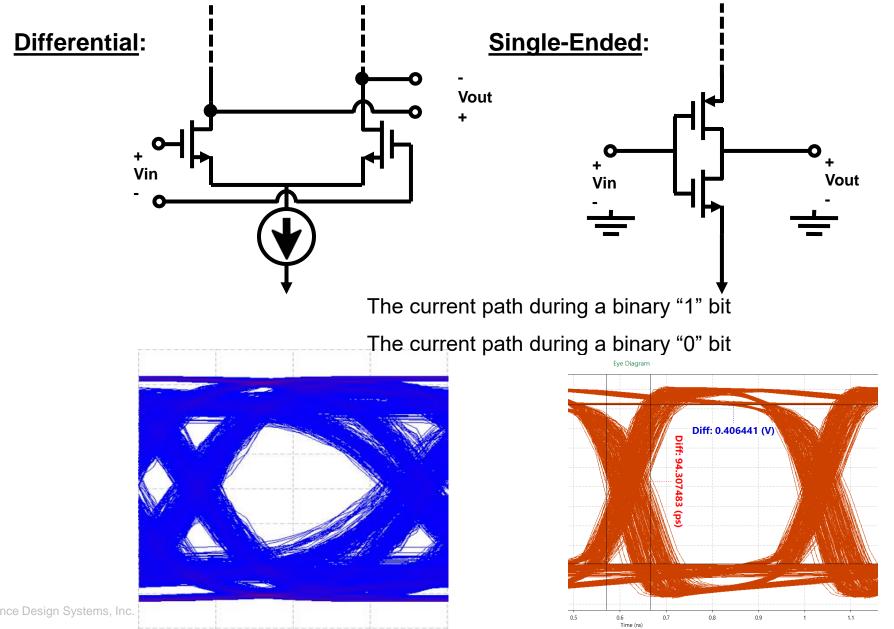

#### Testbench

- Package block uses an extracted RLCK SPICE model

- PCB block uses W-elements with 0.3 meter lengths

#### Characterizing with Step Function – One Rising Transition

#### cādence<sup>°</sup>

### Characterizing with both Rising and Falling Transition

#### cādence<sup>®</sup>

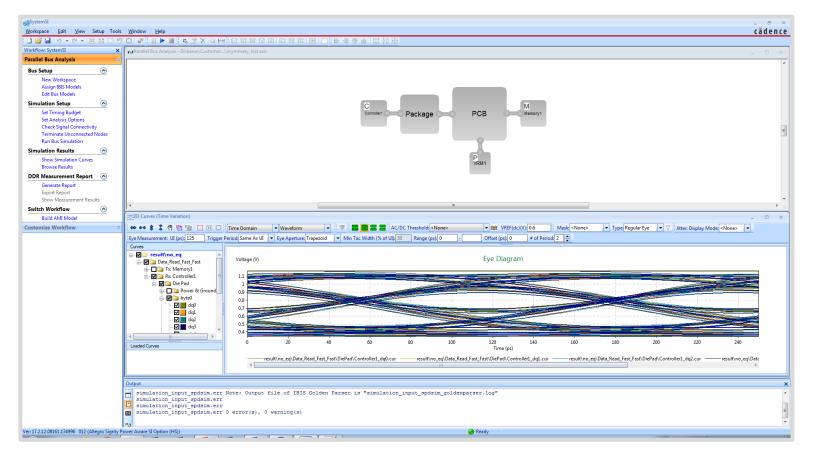

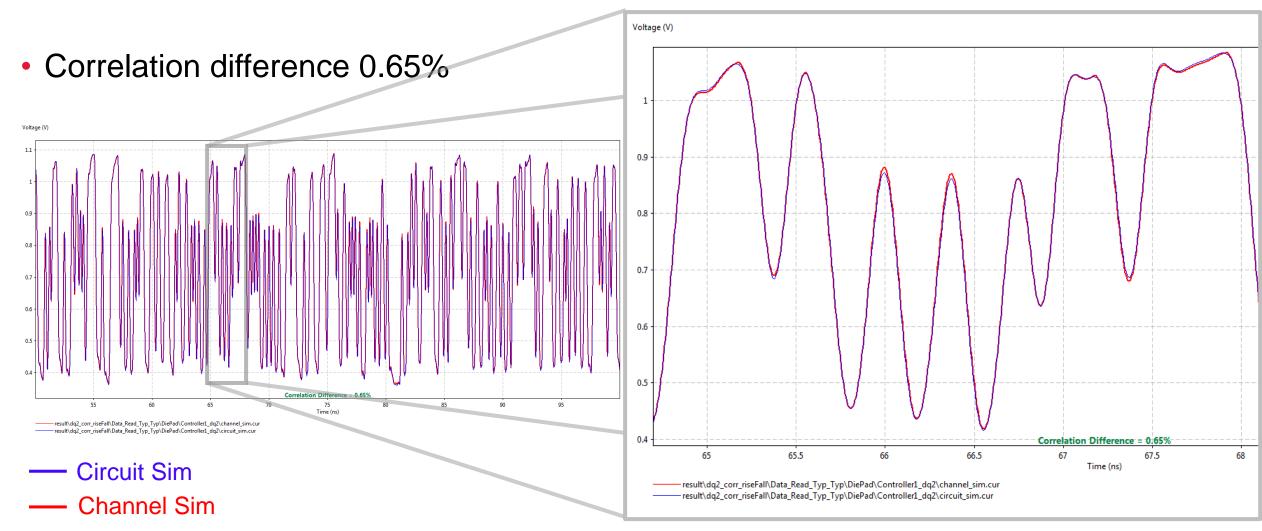

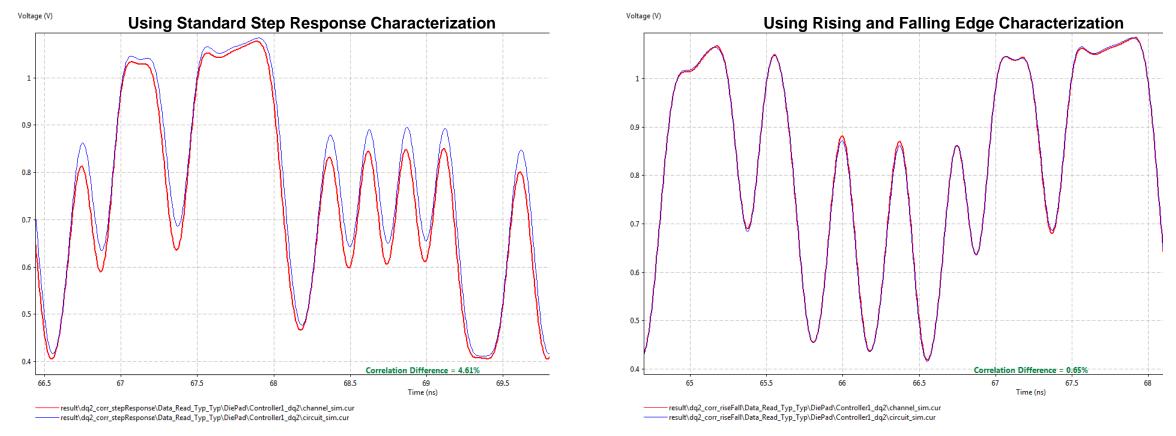

#### Comparison between Two Different Methods

• Correlation error vs. circuit simulation reduced by about 4%

#### Summary

- The **DQ\_34\_3600** I/O model has some asymmetry in its rising and falling edges

- Standard SerDes step response characterization did not do a great job in capturing this behavior, as seen in the circuit / channel sim correlation

- Characterization methods using rising and falling edges captured this behavior very well for channel simulation

## Strobe as Timing Reference

11 © 2019 Cadence Design Systems, Inc. All rights reserved.

### Overview(1)

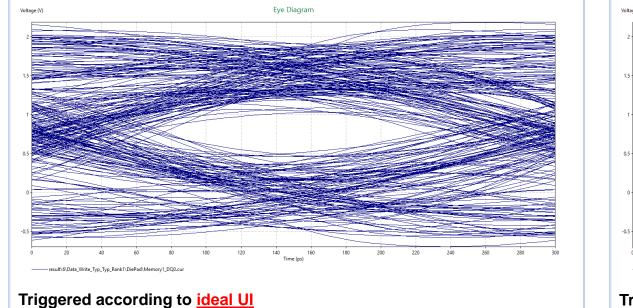

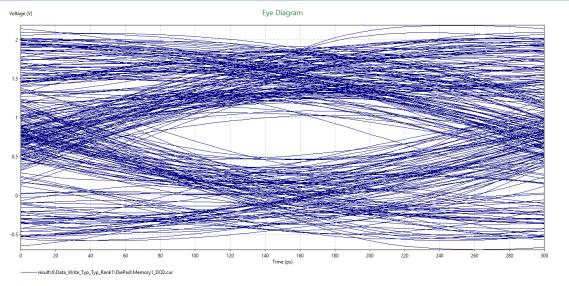

• Different timing reference – Different selection of "trigger" can result in different eye opening

Triggered according to Strobe

© 2019 Cadence Design Systems, Inc. All rights reserved.

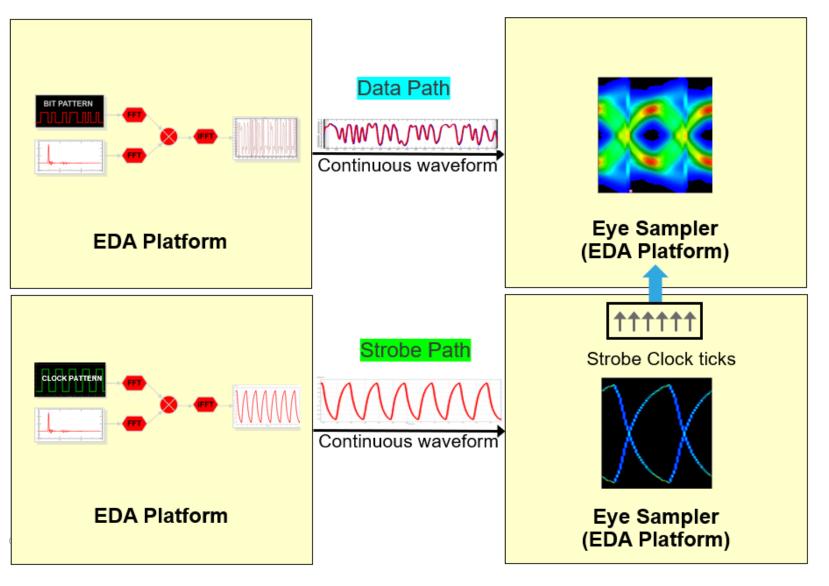

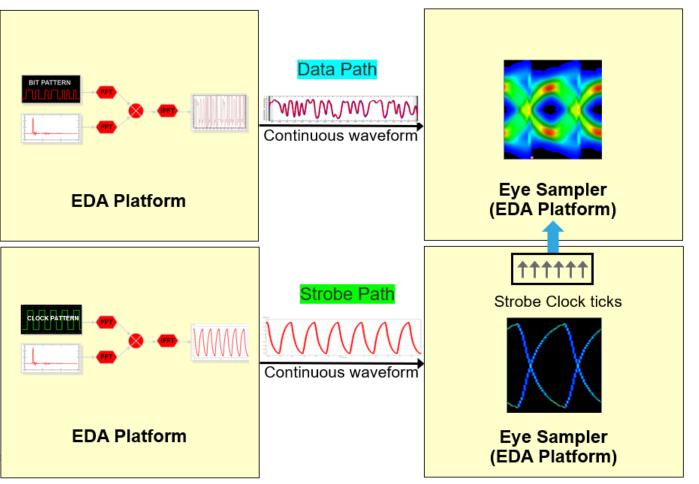

DFE's clock in memory bus will be supplied by Strobe rather than CDR, which can be seen in most differential serial bus

- As channel simulation and IBIS-AMI modeling methods are adapted from serial link to DDR interface analysis, serial link CDR algorithms are often used for analysis

- What is the impact?

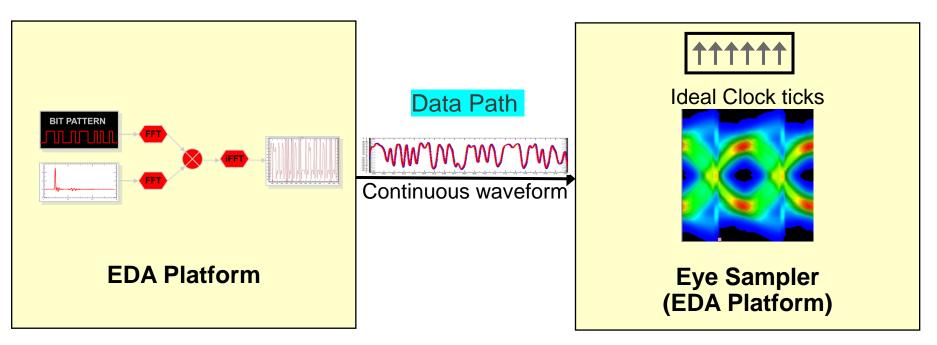

#### **Current CDR-Based Method**

- Centers the eye for each individual signal

- Ideal clock ticks are generated internally by the eye sampler

- Clock ticks can also be generated by AMI models and sent to the eye sampler

Some controllers have some individual bit de-skewing

## True Strobe Timing (TST)

- Clock ticks are collected from the strobe channel instead of the data channel

- With real strobe, this is done for entire byte lane

- Strobe channel is only fed with 0101 data

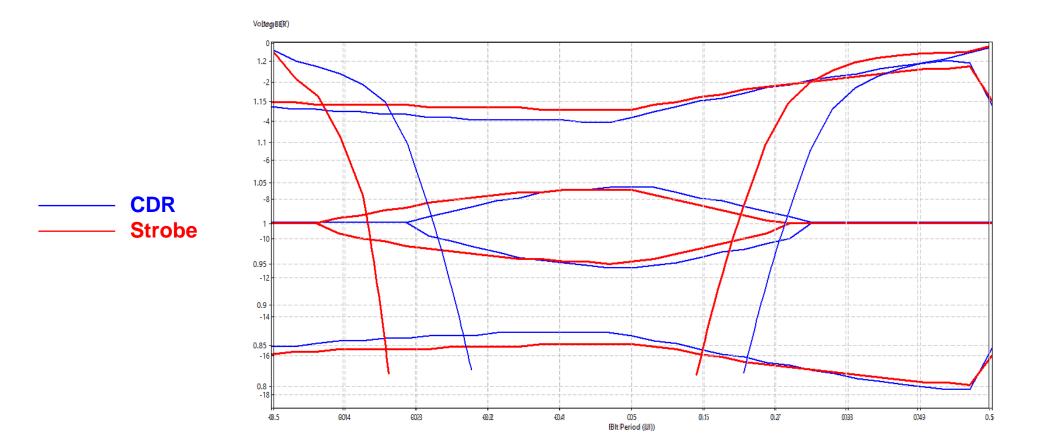

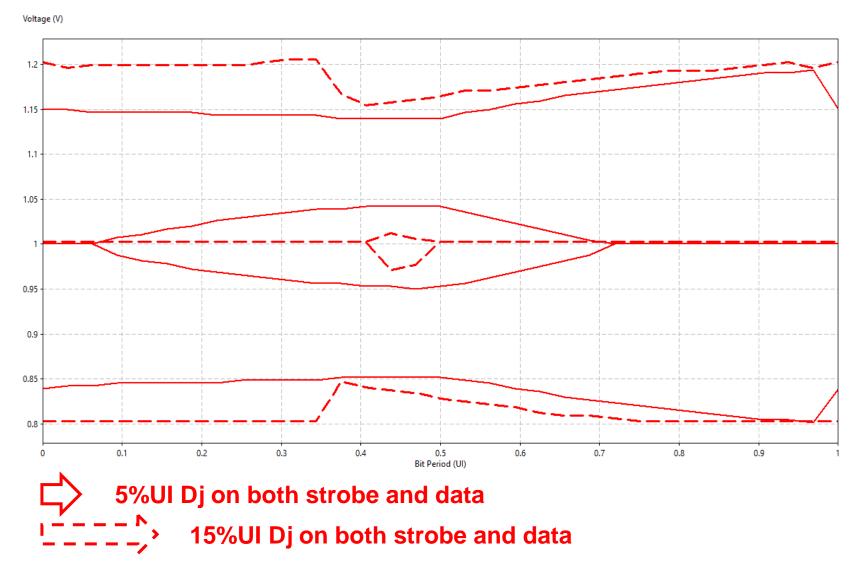

#### **Comparison of Results**

- CDR vs. TST

- CDR vs. TST with jitter impairments

- Test configuration

- 1 data line is used for simulations

- 6 Gbps

- Rx CTLE

- Rx 4 tap DFE

- In phase between strobe and data

#### cādence<sup>®</sup>

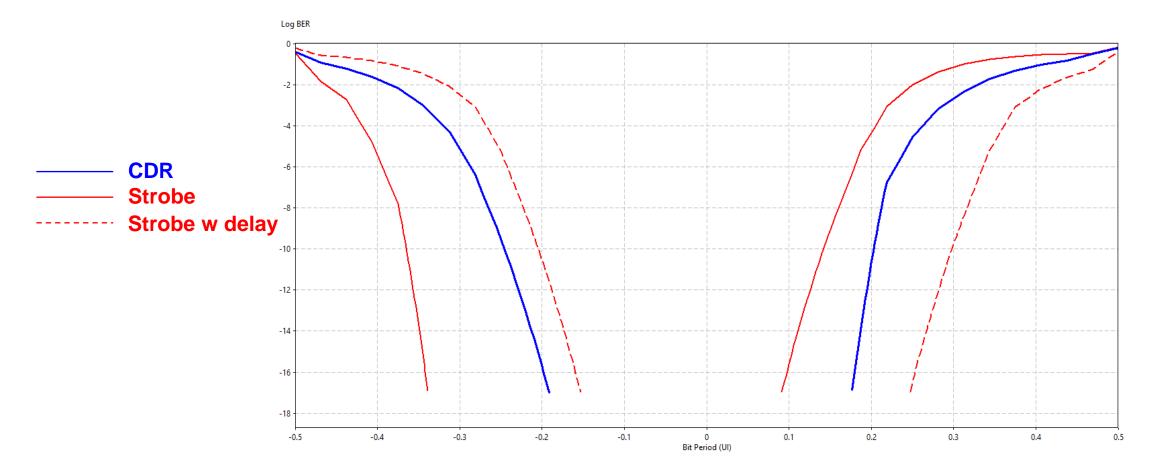

#### CDR vs. TST

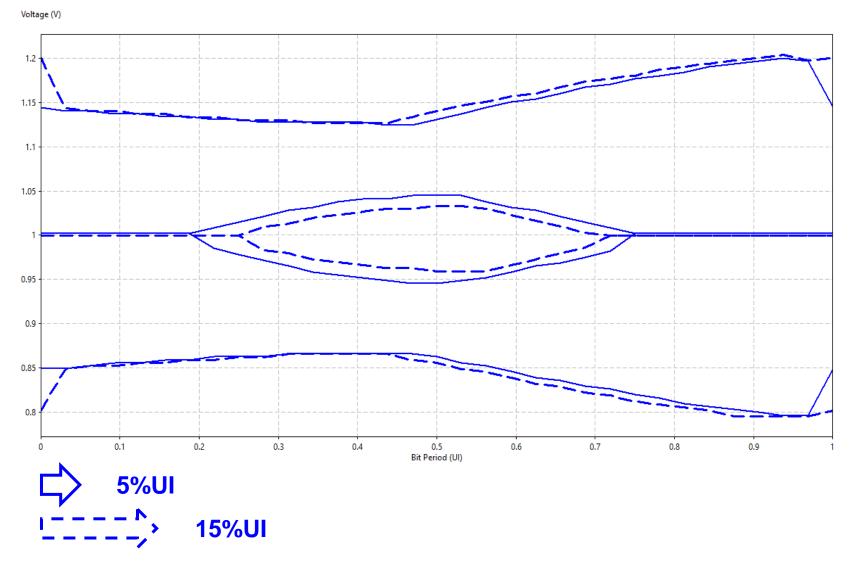

#### CDR Results with Dj Applied at Tx

#### Strobe Results with Dj Applied at Tx

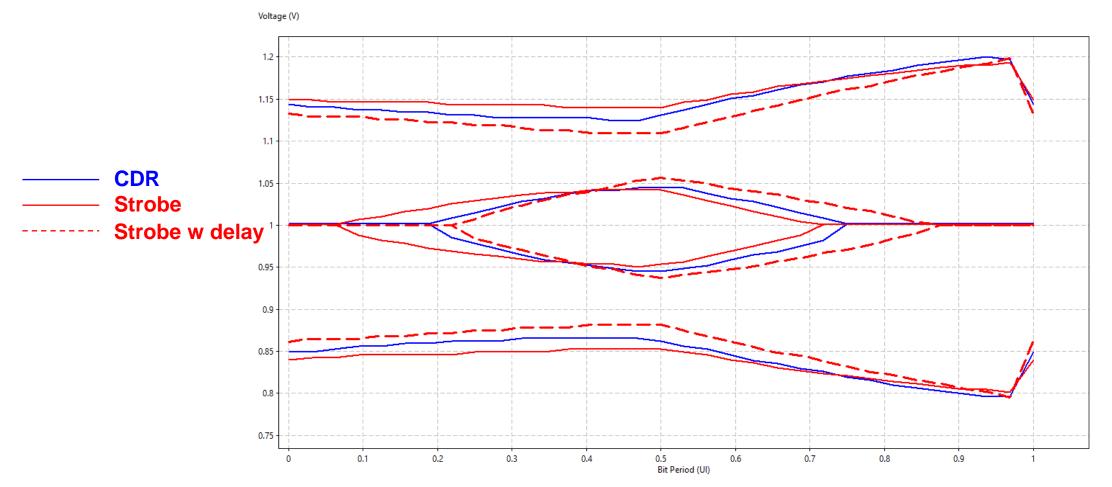

## CDR vs. TST

#### • After delaying by 0.2 UI

#### cādence<sup>®</sup>

## CDR vs. TST

• After delaying by 0.2 UI

#### Summary

- Using default CDR instead of actual strobe to get clock risks will miss important impairments/jitter for parallel bus topology

- Analysis results show false optimism using CDR approach as compared to true strobe timing methodology

- Need to model delay accurately

# cādence®

© 2019 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.