# Expectations for IBIS 7.1

Randy Wolff

Micron Technology

2021 Virtual Asian IBIS Summit – Japan

November 12, 2021

(Previously presented August 17, 2021, by Michael Mirmak, with modifications)

#### Agenda

- History of IBIS 7.1 Development

- Major and Minor Features

- Complex C\_comp Modeling

- On-die Power Distribution Networks

- EMD: Electrical Module Descriptions

- Other Major Changes

- What Comes Next

#### IBIS 7.1 Taking Shape...

- Editorial Task Group re-convened February 26, 2021, to assemble IBIS 7.1

- Weekly meetings Wednesday, 8 AM US Pacific time

- Technical content closed with 13 BIRDs approved for inclusion on July 16

- Current Editorial work focused on

- Clarity and consistency of text

- Delivery to the Open Forum for review and vote in Q4'21

- Documents and minutes available at <a href="https://ibis.org/editorial\_wip">https://ibis.org/editorial\_wip</a>

#### Major and Minor Features of 7.1

- BIRD195.1: Enabling [Rgnd] and [Rpower] Keywords for Input Models

- BIRD197.7: New AMI Reserved Parameter DC\_Offset

- BIRD198.3: Keyword Additions for On-Die PDN (Power Distribution Network) Modeling

- BIRD199: Fix Rx\_Receiver\_Sensitivity Inconsistencies

- BIRD200: C\_comp Model Using IBIS-ISS or Touchstone

- BIRD202.3: Electrical Descriptions of Modules

- BIRD203: Submodel Clarification

- BIRD205: New AMI Reserved Parameter for Sampling Position in AMI\_Init Flow

- BIRD206: Clarification of text "transition time"

- BIRD207: New AMI Reserved Parameters Component\_Name and Signal\_Name

- BIRD208: Clock-Data Pin Relationship Keyword

- BIRD209: Make Clock Times Output Required for Clock Executable Models

- BIRD212: Clarification of PAM4\_UpperThreshold, PAM4\_CenterThreshold, PAM4\_LowerThreshold

- BIRD214: Change "bit\_time" to "symbol\_time"

- BIRD215: Back-channel Statistical Optimization Editorial Update

#### Individual changes documented at https://ibis.org/birds/

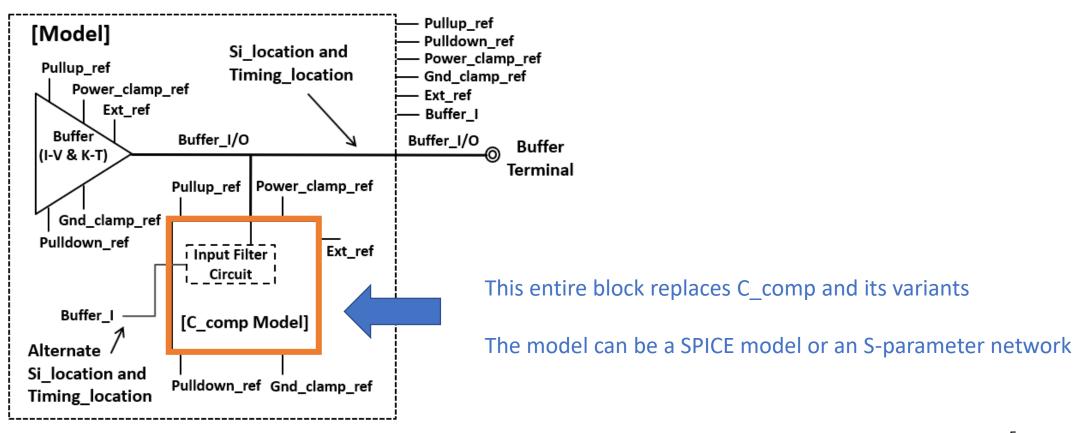

#### Complex C\_comp Modeling

• Modeling impedance using complex frequency- or time-dependent networks rather than single capacitors

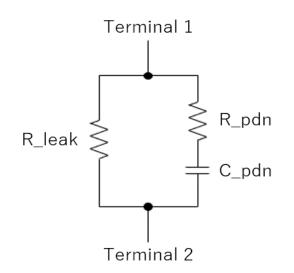

#### **On-Die Power Distribution Networks**

A new set of keywords has been added to describe decoupling networks on the device <u>die</u>, to capture power supply noise effects, "especially in the high-frequency range"

PDN networks are simply described, and connect between signal names or bus labels (terminals) described as PDN Domains

This connects rails, not just pins

Variations are independent of [Model] typ/min/max corners

This is an alternative to Series and Interconnect Model keyword representations and can coexist with them

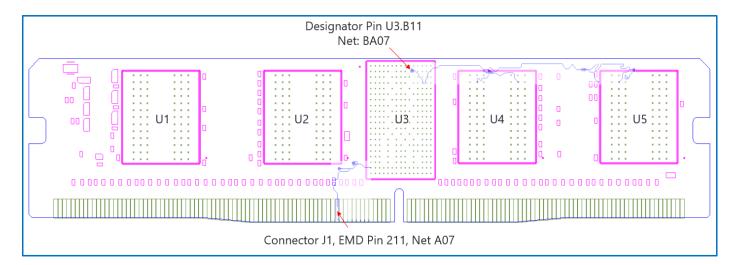

#### EMD: Electrical Module Descriptions

- A way to describe complex networks of devices and/or interconnects that can in turn be used as modules in other networks

- Imagine a DIMM electrical model: a PCB and DRAM device which, together, can be used in multiple instances in a PCB system model

- The successor to EBD, the Electrical Board Description (EBD) format

- EBD had many limitations on connectivity and electrical modeling capabilities

Four devices here are instances of a single IBIS component

The devices are combined on a substrate with its own interconnect description

The substate is a DIMM, which would be simulated in a larger system

### Summary of Other Major Changes

- DC Offset

- Expands support for single-ended interfaces (e.g., DDR) by communicating channel DC level to IBIS-AMI receivers

- Back-channel Statistical Optimization

- Expands model-to-model training of equalization beyond bitstream simulation

- Sampling Position in AMI\_Init Flow

- Enables more model-level control of signal sampling in statistical IBIS-AMI simulations

- Expanding Architectural Descriptions, Including Clocking and Clock-Forwarding Support

- Adding Component\_Name and Signal\_Name enables buffer-specific information to be passed into IBIS-AMI models at the component level

- DQ/DQS GetWave support enables clock ticks to be used in data latching across models

- Explicit links between clock and data pins permits tools to monitor and impose component latching relationships

#### What's Next

- A more detailed overview of IBIS 7.1 will be presented at a future IBIS Summit

- Until then, IBIS Editorial and the Open Forum will be reviewing the document in preparation for approval

## Please review the draft IBIS 7.1 documents – your feedback is gratefully accepted!