# SiSoff

## IBIS QUALITY COMMITTEE UPDATE PCB\_EAST IBIS SUMMIT Oct 21, 2003

Robert Haller rhaller@sisoft.com Signal Integrity Software, Inc. 6 Clock Tower Place – Suite 250 Maynard MA. 01754 978-461-0449 X 15

#### **Quality IBIS Models Imperative**

#### **IBIS Quality Subcommittee Group Effort !**

Committee is represented by Semiconductor vendors, EDA vendors, and IBIS end-users.

SiSoft - Barry Katz (Chairman), Robert Haller, Eric Brock, Kevin Fisher Siemens – Eckhard Lenski, Katja Koller IBM - Greg Edlund EMC - Brian Arsenault Cadence - Lynne Green Apple – John Figueroa, Kim Helliwell Mentor – John Angulo, Hazem Hegazy, Sherif Hammad, Cisco – Mike LaBonte, Todd Westerhoff Hitachi ULSI Systems – Shoji Kazuyoshi, Nonoyama Sadahiro Leventhal Design & Communications - Roy Leventhal Intel – Benjamin Silva Teraspeed – Bob Ross, Tom Dagostino AMCC - Peter LaFlamme Fairchild – Adam Tambone

### IBIS Problem Areas IQ committee belaboured

#### • C\_comp

- Varies with voltage and frequency

- Varies for Driver vs. Receiver (I/O cell)

- On Die termination

- Both Curves Over entire Range (No interpolation)

- Excessive Currents in IV curves

- VT Table "Lead in time"

- Excessive "lead in" causes over-clocking issues

- How to specify "excessive dead time"

- · VT versus IV crosscheck

- Differential Models with Only Ramps

- Are 4 curves necessary ?

- · SPICE2IBIS

- creates some of these problems !

### IBIS Confusion Among so called "experts"

- Terminology

- Corner Conditions Fast Slow versus min and max

- What does IBISCHK Check and limits ?

- C\_comp

- Min Typ Max versus Process Corner

- On Die termination

- Non-Monotonic/Combination of Curves

- Pull\_up and Clamps

- Pull\_down and Clamps

- Package model

- Vendors translates IBIS models, Added features

- Lumped versus distributed

#### **IBIS Quality Subcommittee**

#### Goals

- Rating system that is easy to understand and adopt

- Communicate to vendors/users.

- Cover overall file, component, and model sections

- Check for completeness, correctness, accuracy

- Leverage of prior work Meet every 2 weeks (Tuesdays 11:00 EDT for 1 hour)

- Mailing list

- lbis-quality@freelists.org

- http://www.freelists.org/archives/ibis-quality

- Web Site

- http://www.sisoft.com/ibis-quality

#### Status and To Do

- Preliminary Documentation Available

- Quality levels

- Level 0 Passes IBISCHK (checked by Software)

- Level 1 Complete and correct (manual checks)

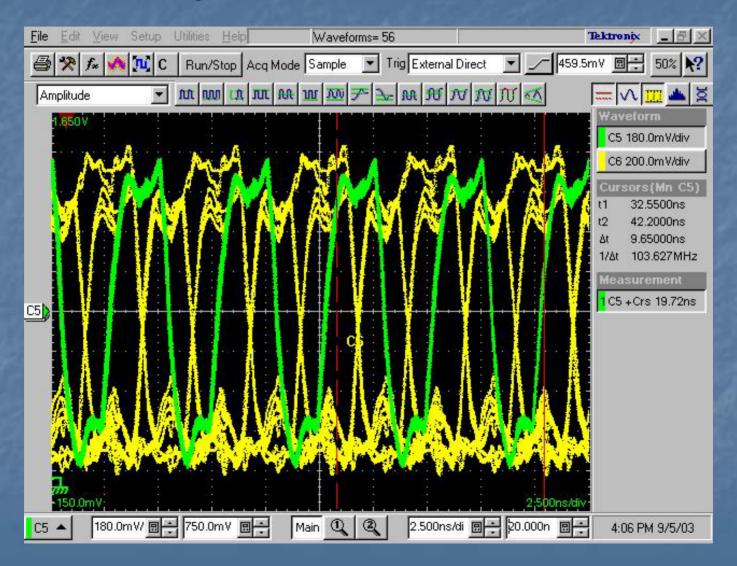

- Level 2a, 2b Correlation: Simulation, Measurement

- Level 3 All of the above

- Reference IBIS Accuracy Handbook

- Need to update IBIS Quality checklist

- http://www.sisoft.com/ibis-quality/

- Submit BIRDS and IBISCHK enhancements

- Final Documentation

#### Summary

- Quality IBIS models Imperative

- IBIS problems and confusion among "experts"

- Draft Documentation Available !

- Please Review Documentation