# **Correlation study for DDR style terminations with IBIS models**

Arpad Muranyi

arpad.muranyi@intel.com

# **Signal Integrity Engineering**

September 13, 2001

http://www-fmec.fm.intel.com/sie

- This study was done to find out what the response of IBIS models is when the buffer is terminated to the middle of the voltage swing (as it is done in DDR buses) instead of one of the rails.

- Traditionally the V\_fixture parameters of IBIS models use Vcc and GND in attempt to obtain waveforms for the on/off characteristics of the pullup and pulldown structures.

- The question is, how are IBIS models going to behave if models made with such waveforms are used in a circuit where the termination voltage is not one of the rails, but a voltage half way between, as it is done in DDR buses.

- This presentation shows the results obtained using HSPICE's B-element. The plan is to try out as many other IBIS simulators as possible with the same IBIS model so that a decision could be made regarding what the best method is for making IBIS models for DDR buffers, and/or whether a change in the IBIS specification or simulation tool algorithms is necessary.

intel® 1

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

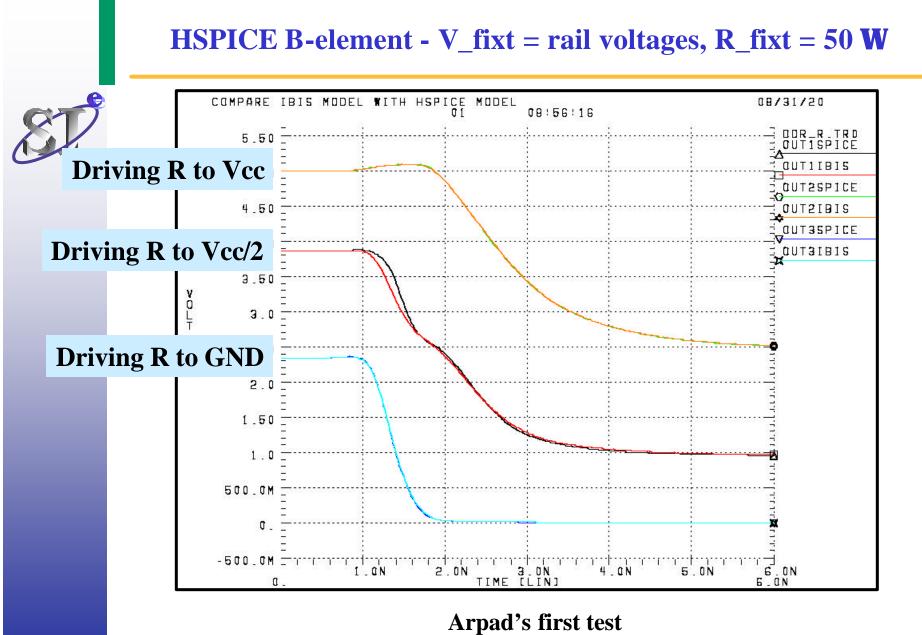

### **HSPICE B-element - V\_fixt = rail voltages, R\_fixt = 50 W**

Arpad's first test

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

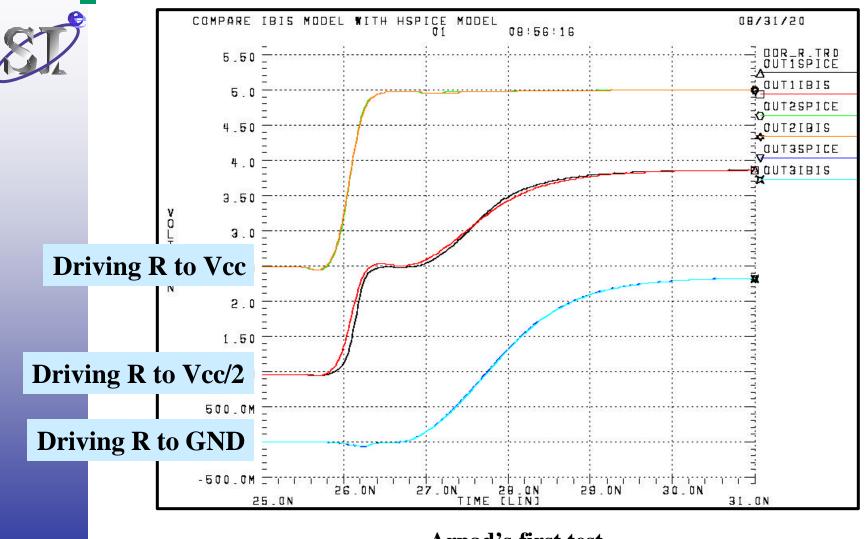

### HSPICE B-element - V\_fixt = Vcc/2, R\_fixt = 50 W

Arpad's first test

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

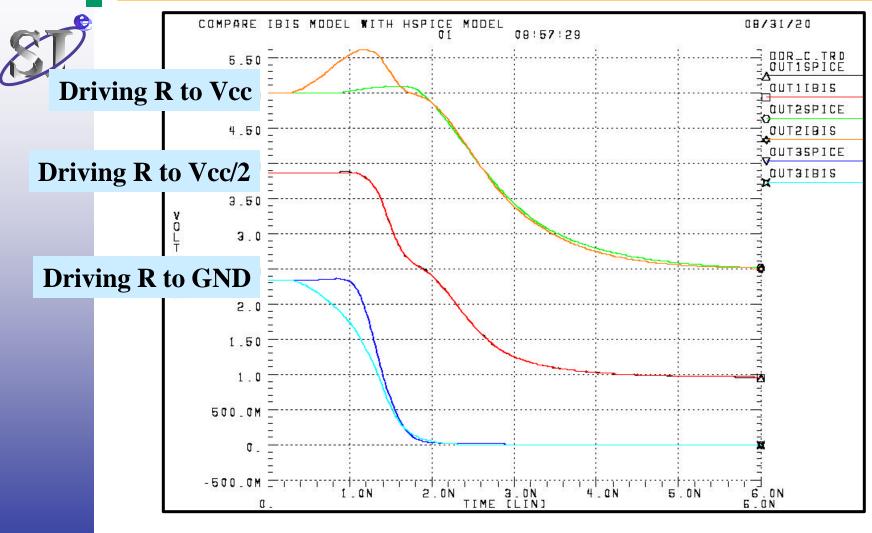

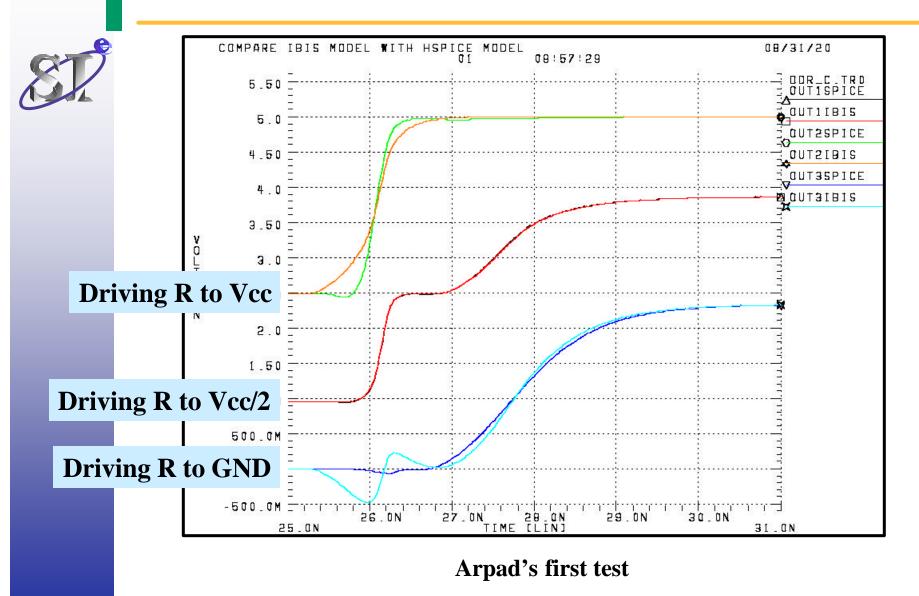

#### HSPICE B-element - V\_fixt = Vcc/2, R\_fixt = 50 W

intel®

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

#### **HSPICE B-element - V\_fixt = rail voltages, R\_fixt = 80 W** COMPARE IBIS NODEL WITH HSPICE NODEL 09/13/20 13:48:39 01 DDR\_R80.TR0 5.50 OUT15PICE Driving R to Vcc OUT1IBIS OUT2SPICE QUT2IBIS **Driving R to Vcc/2 OUT35PICE OUT3IBIS** 3.50 **Driving R to GND** 2.50 Ň 2.0 1.50 1.0 500.0M 0 -500.0M IT 1 Б. 0N JINE (LIN) 4.0N 5.0N 1.0N 2. 0N 0. 6.0N

Scott: cover the signal's voltage span around Vtt with the V-t curves

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

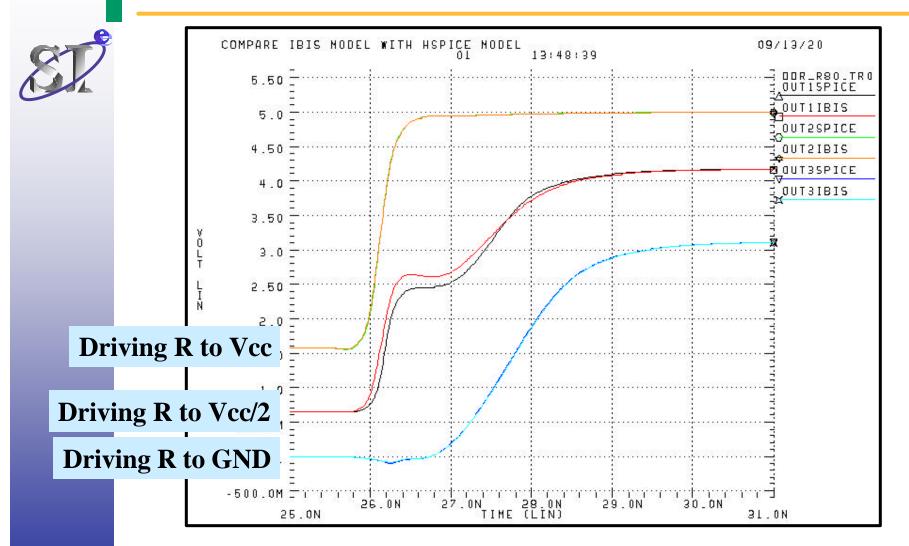

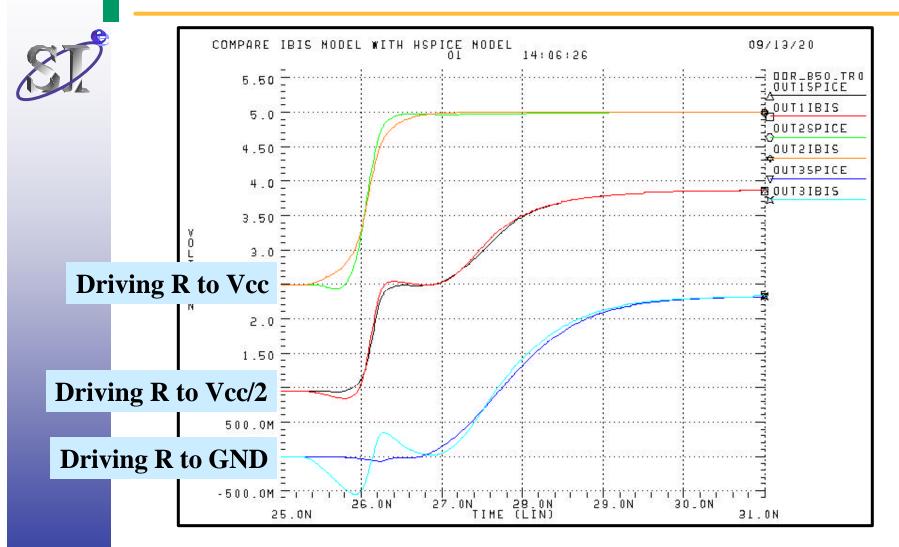

# **HSPICE B-element - V\_fixt = rail voltages, R\_fixt = 80 W**

Scott: cover the signal's voltage span around Vtt with the V-t curves

**Bob: try V\_fixture values between Vtt and the rail voltages**

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

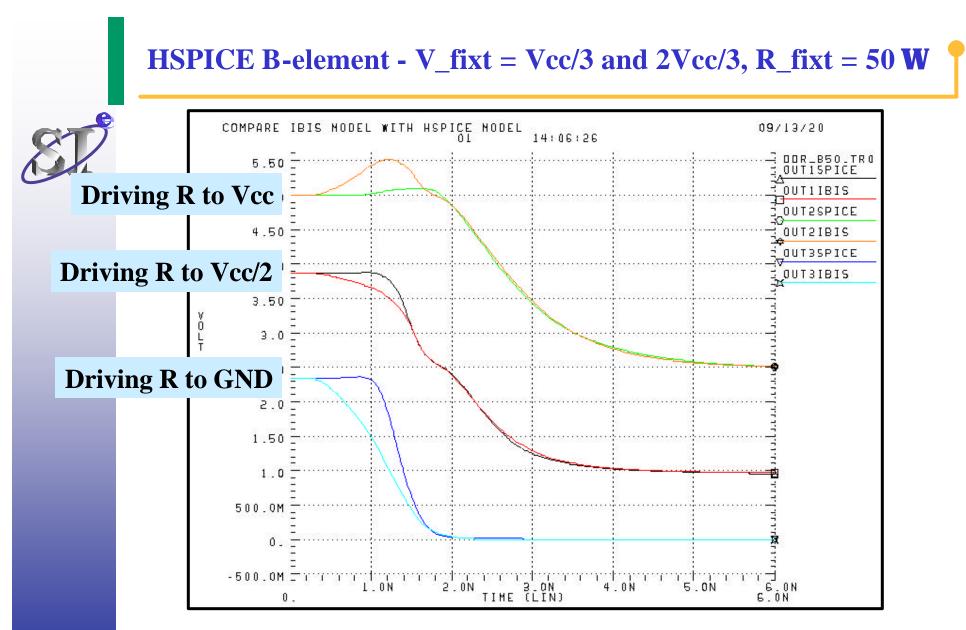

# HSPICE B-element - V\_fixt = Vcc/3 and 2Vcc/3, R\_fixt = 50 W

**Bob: try V\_fixture values between Vtt and the rail voltages**

5/29/2001 http://www-fmec.fm.intel.com/sie \*Other brands and names are the property of their respective owners

# Conclusions

- HSPICE's B-element will give correct results if the waveforms for the IBIS models are made with V\_fixture that is the same as Vtt of the bus that the buffer will drive.

- Theoretically the waveforms should always match, regardless of what V\_fixture is in the model, and not have this dependency.

- Further study is required to run the same tests in other tools to see whether this is an HSPICE phenomena or a general IBIS problem.