Date: Thu Feb 06 2014 - 22:45:39 PST

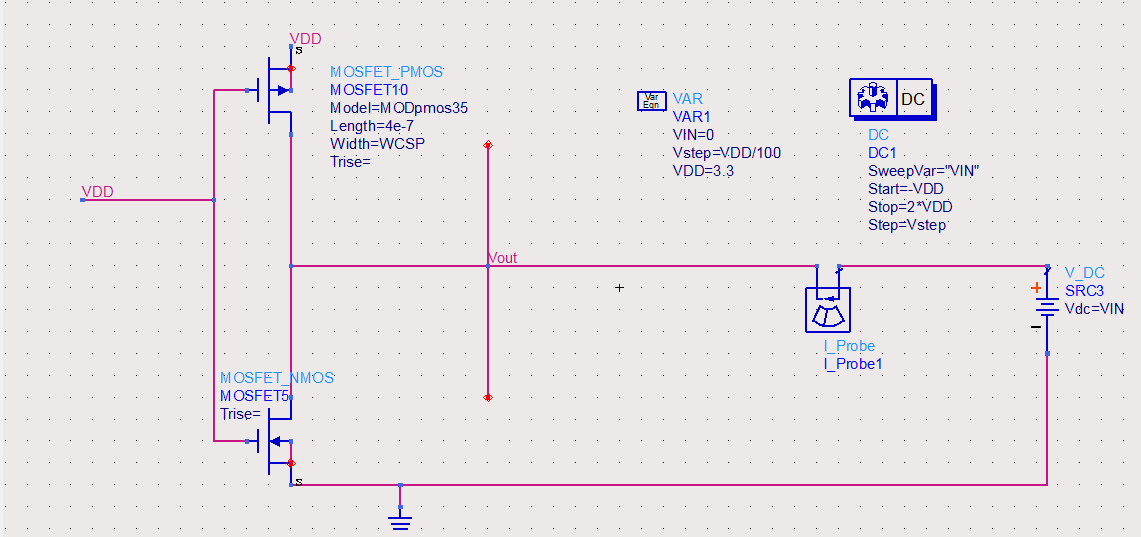

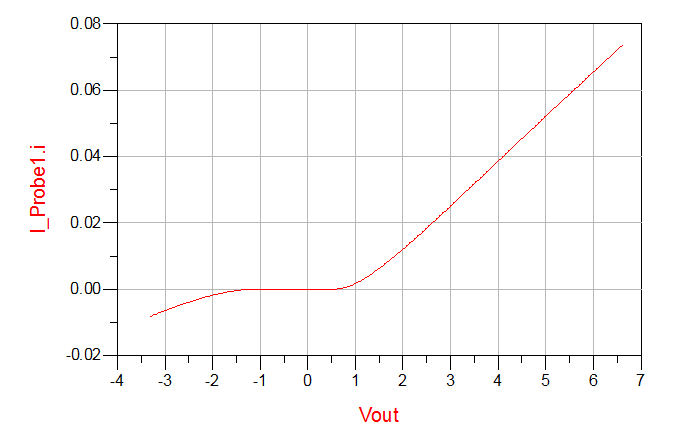

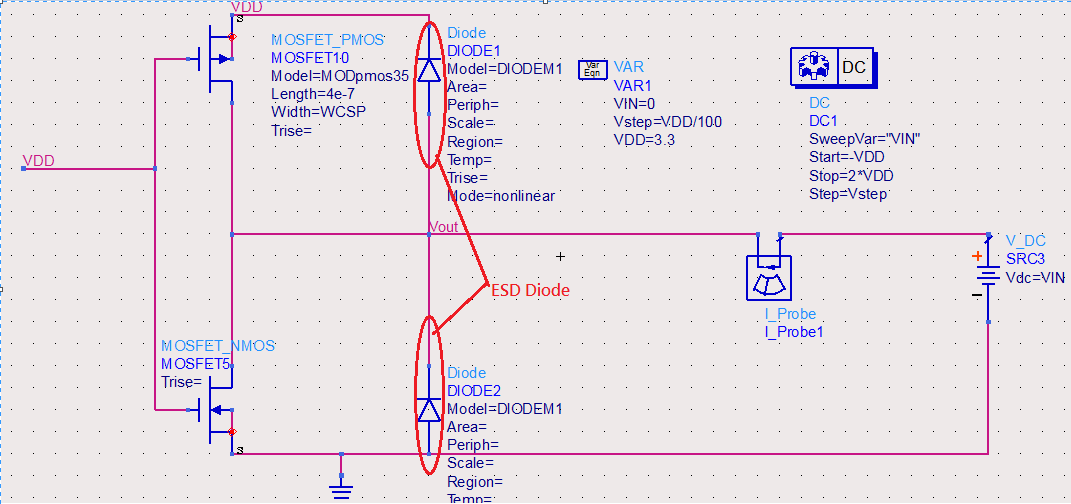

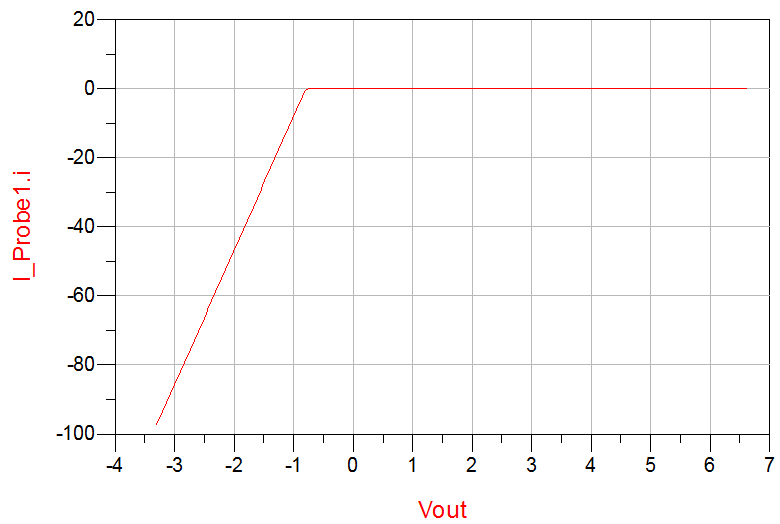

Dear sir, Sorry for bothering you. I tried to follow the IBIS cook book to setup the simulation for I-V curve pull-down extracting with Agilent tool(Please see Figure1),and got the result(as Figure2). Also added the ESD diode(as Figure3) to emulating the GND clamp, extracted the I-V curve as Figure4. Would you help check whether all setup and results were correct for I-V curve extracting? If any I missed, please feel free let me know. Thanks in advance. Figure1. [cid:image001.png@01CF2413.44CC1E00] Figure2. [cid:image002.png@01CF2413.44CC1E00] Figure3. [cid:image003.png@01CF2413.44CC1E00] Figure4. [cid:image004.png@01CF2413.44CC1E00] Thanks a lot. Sincerely, Aje Good day. -- This message has been scanned for viruses and dangerous content by MailScanner, and is believed to be clean. -------------------------------------------------------------------- |For help or to subscribe/unsubscribe, e-mail mikelabonte@eda-stds.org |or ibis-request@eda-stds.org | |IBIS reflector archives exist under: | | http://www.eda-stds.org/ibis/email_archive/ Recent | http://www.eda-stds.org/ibis/users_archive/ Recent | http://www.eda-stds.org/ibis/email/ E-mail since 1993