## IBIS 5.1 draft <u>v135v140</u>

## **Contents**

| 1             | General Introduction                                          |                |

|---------------|---------------------------------------------------------------|----------------|

| 2             | Statement of Intent                                           |                |

| 3             | General Syntax Rules and Guidelines                           | 6              |

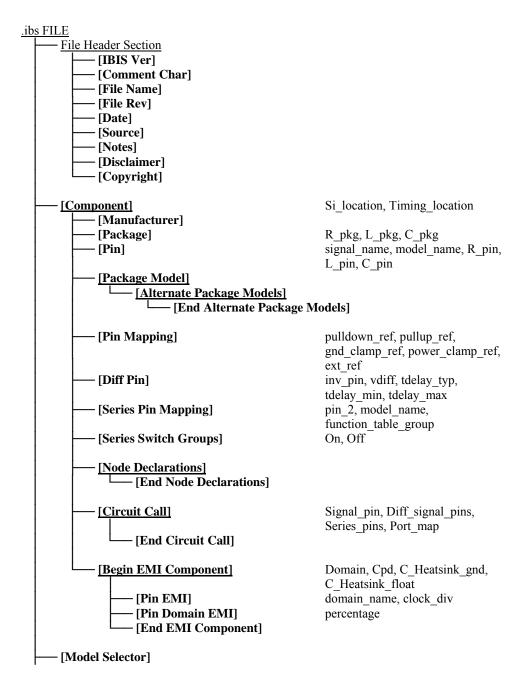

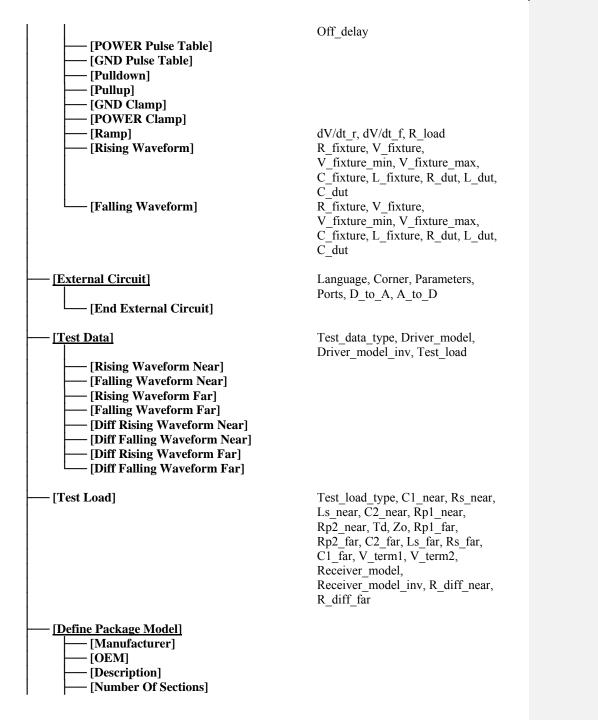

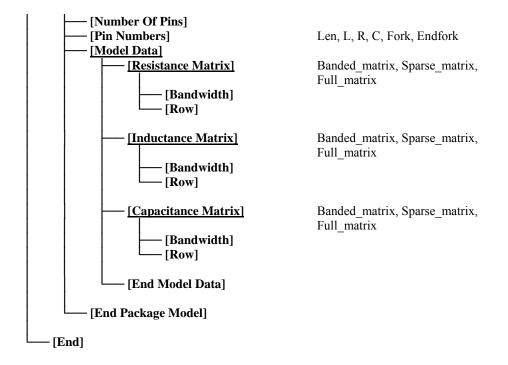

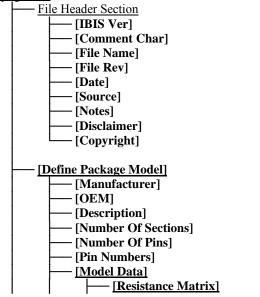

| 3A            | Keyword Hierarchy                                             |                |

| 4             | File Header Information                                       |                |

| 5             | Component Description                                         |                |

| 6             | Model Statement                                               |                |

| <u>6</u> A    | Add Submodel Description                                      |                |

| 6B            | Multi-Lingual Model Extensions                                |                |

| 6C            | Algorithmic Modeling Interface (AMI)                          |                |

| 6D            | Test Load and Data Description                                |                |

| 7             | Package Modeling                                              |                |

| 8             | Electrical Board Description                                  |                |

| 9             | Notes on Data Derivation Method                               |                |

| 10            | Notes on Algorithmic Modeling Interface and Programming Guide |                |

| 10.1          | Overview                                                      |                |

| 10.2          | Application Scenarios                                         |                |

| 10.2.1        | Statistical simulations                                       |                |

| 10.2.2        | Time domain simulations                                       |                |

| 10.2.3        | Reference Flows                                               |                |

| 10.3          | Function Signatures                                           |                |

| 10.4          | Code Segment Examples                                         |                |

| 10A           | AMI Parameter Definition File Structure                       |                |

| 11            | EMI Parameters                                                |                |

| 1             | General Introduction                                          | 2              |

| 2             | Statement of Intent                                           |                |

| 3             | General Syntax Rules and Guidelines                           |                |

| <u>3A</u>     | Keyword Hierarchy                                             |                |

| 4             | File Header Information                                       |                |

| 5             | Component Description                                         |                |

| 6             | -Model Statement                                              |                |

| <u>6A</u>     | -Add Submodel Description                                     |                |

| <del>6B</del> | - <u>Multi-Lingual Model Extensions</u>                       |                |

| <del>6C</del> | <u> Algorithmic Modeling Interface (AMI)</u>                  |                |

| 6D            | Test Load and Data Description                                |                |

| 7             | Package Modeling                                              |                |

| 8             | - <u>Electrical Board Description</u>                         |                |

| 9             | -Notes on Data Derivation Method                              |                |

| 10            | Notes on Algorithmic Modeling Interface and Programming Guide |                |

| 10.1          | Overview                                                      | <del>169</del> |

| 10.2          | -Application Scenarios                                        | <del>169</del> |

| 10.2.1        | Statistical simulations                                       |                |

| 1022          | Time domain simulations                                       | 171            |

Formatted: Default Paragraph Font Formatted: Default Paragraph Font

# IBIS 5.1 draft v1<del>35<u>40</u></del>

| 10.2.3 Reference Flows                                    |       | Formatted: Default P |

|-----------------------------------------------------------|-------|----------------------|

| 10.3 Function Signatures                                  |       | Formatted: Default P |

| 10.4 <u>Code Segment Examples</u>                         |       | Formatted: Default P |

| <u>10A</u> <u>AMI Parameter Definition File Structure</u> |       | Formatted: Default P |

| 11 <u>EMI Parameters</u> 210                              | 1. 1. | Formatted: Default P |

| Formatted: I | Default | Paragraph | Font |

|--------------|---------|-----------|------|

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

| Formatted:   | Default | Paragraph | Font |

## **1 GENERAL INTRODUCTION**

This section gives a general overview of the remainder of this document.

Sections 2 and 3 contain general information about the IBIS versions and the general rules and guidelines. Several progressions of IBIS documents are referenced in Section 2 and in the discussion below. They are IBIS Version 1.1 (ratified August 1993), IBIS Version 2.1 (ratified as ANSI/EIA-656 in December 1995), IBIS Version 3.2 (ratified as ANSI/EIA-656-A in October 1999 and renewed on August 17, 2005), IBIS Version 4.2 (ratified as ANSI/EIA-656-B on March 1, 2007), and IBIS Version 5.0 (ratified on August 29, 2008)

The functionality of IBIS follows in Sections 3A through 8. Sections 3A through 6 describe the format of the core functionality of IBIS Version 1.1 and the extensions in later versions. The data in these sections are contained in .ibs files. Section 7 describes the package model format of IBIS Version 2.1 and a subsequent extension. Package models can be formatted within .ibs files or can be formatted (along with the Section file header keywords) as .pkg files. Section 8 contains the Electrical Board Description format of IBIS Version 3.2. Along with Section 4 header information, electrical board descriptions must be contained in separate .ebd files.

Sections 6C, 10, and 11 are new in IBIS Version 5.0 and contain reference and modeling information related to the algorithmic modeling interface support, and EMI parameters. Sections 6D and 10A are new in IBIS 5.1, to place test loads and data appropriately in the keyword hierarchy and to more fully describe algorithmic model files, respectively.

Section 9 contains some notes regarding the extraction conditions and data requirements for IBIS files. This section focuses on implementation conditions based on measurement or simulation for gathering the IBIS compliant data.

# 2 STATEMENT OF INTENT

In order to enable an industry standard method to electronically transport IBIS modeling data between semiconductor vendors, EDA tool vendors, and end customers, this template is proposed. The intention of this template is to specify a consistent format that can be parsed by software, allowing EDA tool vendors to derive models compatible with their own products.

One goal of this template is to represent the current state of IBIS data, while allowing a growth path to more complex models/methods (when deemed appropriate). This would be accomplished by a revision of the base template, and possibly the addition of new keywords or categories.

Another goal of this template is to ensure that it is simple enough for semiconductor vendors and customers to use and modify, while ensuring that it is rigid enough for EDA tool vendors to write reliable parsers.

Finally, this template is meant to contain a complete description of the I/O elements on an entire component. Consequently, several models will need to be defined in each file, as well as a table that equates the appropriate buffer to the correct pin and signal name.

Version 5.0 of this electronic template was finalized by an industry-wide group of experts representing various companies and interests. Regular "IBIS Open Forum" meetings were held to accomplish this task.

**Commitment to Backward Compatibility**. Version 1.0 is the first valid IBIS ASCII file format. It represents the minimum amount of I/O buffer information required to create an accurate IBIS model of common CMOS and bipolar I/O structures. Future revisions of the ASCII file will add items considered to be "enhancements" to Version 1.0 to allow accurate modeling of new, or other I/O buffer structures. Consequently, all future revisions will be considered supersets of Version 1.0, allowing backward compatibility. In addition, as modeling platforms develop support for revisions of the IBIS ASCII template, all previous revisions of the template must also be supported.

**Version 1.1 update**. Version 1.1, (published as "ver1\_1.ibs") is conceptually the same as the 1.0 version of the IBIS ASCII format (published as "ver1\_0.ibs"). However, various comments have been added for further clarification.

**Version 2.0 update**. Version 2.0 maintains backward compatibility with Versions 1.0 and 1.1. All new keywords and elements added in Version 2.0 are optional. A complete list of changes to the specification is in the IBIS Version 2.0 Release Notes document ("ver2\_0.rn.txt").

**Version 2.1 update**. Version 2.0 contains clarification text changes, corrections, and two additional waveform parameters beyond Version 2.0.

**Version 3.0 update**. Version 3.0 adds a number of new keywords and functionality. A complete list of functions can be found on eda.org under /pub/ibis/birds/birds/birddir.txt showing the approved Buffer Issue Resolution Documents (BIRDs) that have been approved for Version 3.0.

**Version 3.1 update**. Version 3.1 contains a major reformatting of the document and a simplification of the wording. It also contains some new technical enhancements that were unresolved when Version 3.0 was approved.

**Version 3.2 update**. Version 3.2 adds more technical advances and also a number of editorial changes documented in 12 BIRDs and also in responses to public letter ballot comments.

**Version 4.0 update**. Version 4.0 adds more technical advances and a few editorial changes documented in 11 BIRDs.

**Version 4.1 update**. Version 4.1 adds more technical advances and a few editorial changes documented in 10 BIRDs.

**Version 4.2 Update**. Version 4.2 adds more technical advances and some editorial changes documented in 13 BIRDs.

**Version 5.0 Update**. Version 5.0 adds more technical advances and some editorial changes documented in 10 BIRDs.

**Version 5.1 Update**. Version 5.1 adds more technical advances and some editorial changes documented in 23 BIRDs. Additionally, Version 5.1 uses a new document format.

IBIS 5.1 draft v1<del>35<u>40</u></del>

## **3 GENERAL SYNTAX RULES AND GUIDELINES**

This section contains general syntax rules and guidelines for ASCII IBIS files:

- 1. The content of the files is case sensitive, except for reserved words and keywords.

- The following words are reserved words and must not be used for any other purposes in the document:

POWER - reserved model name, used with power supply pins,

GND - reserved model name, used with ground pins,

- NC reserved model name, used with no-connect pins,

- NA used where data not available,

CIRCUITCALL - used for circuit call references in Section 6B.

3. To facilitate portability between operating systems, file names used in the IBIS file must only have lower case characters. File names should have a basename of no more than forty (40) characters followed by a period ("."), followed by a file name extension of no more than three characters. The file name and extension must use characters from the set (space, "", 0x20 is not included):

a b c d e f g h i j k l m n o p q r s t u v w x y z

0123456789\_^\$~!#%&-{})(@``

The file name and extension are recommended to be lower case on systems that support such names.

- 4. A line of the file may have at most 120 characters, followed by a line termination sequence. The line termination sequence must be one of the following two sequences: a linefeed character, character or a carriage return followed by linefeed character.

- 5. Anything following the comment character is ignored and considered a comment on that line. The default "|" (pipe) character can be changed by the keyword [Comment Char] to any other character. The [Comment Char] keyword can be used anywhere in the file as desired.

- 6. Keywords must be enclosed in square brackets, "[]", and must start in column 1 of the line. No space or tab is allowed immediately after the opening bracket "[" or immediately before the closing bracket "]". If used, only one space (" ") or underscore ("\_") character separates the parts of a multi-word keyword.

- 7. Underscores and spaces are equivalent in keywords. Spaces are not allowed in subparameter names.

- 8. Valid scaling factors are:

| T = tera | k = kilo  | n = nano  |

|----------|-----------|-----------|

| G = giga | m = milli | p = pico  |

| M = mega | u = micro | f = femto |

When no scaling factors are specified, the appropriate base units are assumed. (These are volts, amperes, ohms, farads, henries, and seconds.) The parser looks at only one alphabetic character after a numerical entry, therefore it is enough to use only the prefixes to scale the parameters. However, for clarity, it is allowed to use full abbreviations for the units, (e.g., pF, nH, mA, mOhm). In addition, scientific notation IS allowed (e.g., 1.2345e-12).

- The I-V data tables should use enough data points around sharply curved areas of the I-V curves to describe the curvature accurately. In linear regions there is no need to define unnecessary data points.

- 10. The use of tab characters is legal, but they should be avoided as much as possible. This is to eliminate possible complications that might arise in situations when tab characters are automatically converted to multiple spaces by text editing, file transferring and similar software. In cases like that, lines might become longer than 120 characters, which is illegal in IBIS files.

- 11. Currents are considered positive when their direction is into the component.

- 12. All temperatures are represented in degrees Celsius.

- 13. Important supplemental information is contained in Section 9, "NOTES ON DATA DERIVATION METHOD", concerning how data values are derived.

- 14. Only ASCII characters, as defined in ANSI Standard X3.4-1986, may be used in an IBIS file. The use of characters with codes greater than hexadecimal 07E is not allowed. Also, ASCII control characters (those numerically less than hexadecimal 20) are not allowed, except for tabs or in a line termination sequence. As mentioned in item 10 above, the use of tab characters is discouraged.

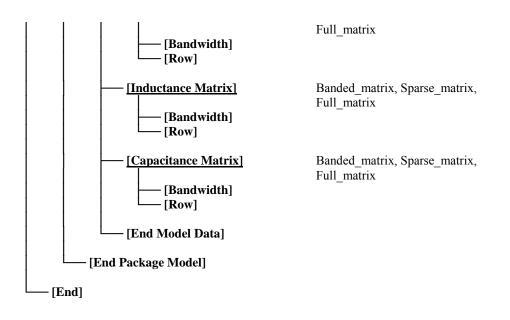

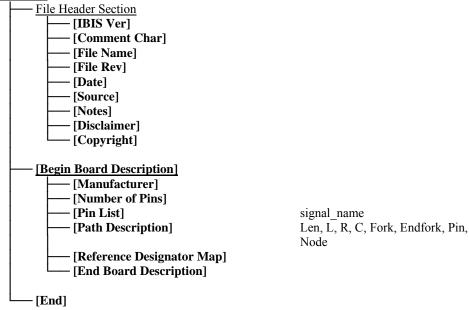

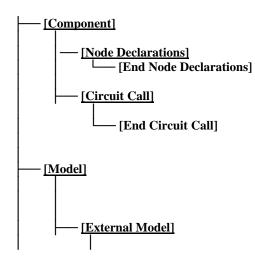

## 3A KEYWORD HIERARCHY

# IBIS 5.1 draft v135v140

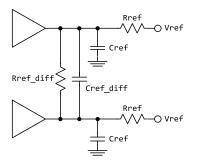

| — [ <u>Model]</u>                                                                                                                                                                                                                               | Model_type, Polarity, Enable,<br>Vinl, Vinh, C_comp, C_comp_pullup,<br>C_comp_pulldown,<br>C_comp_power_clamp,<br>C_comp_gnd_clamp<br>Vmeas, Cref, Rref, Vref<br>Rref_diff, Cref_diff                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

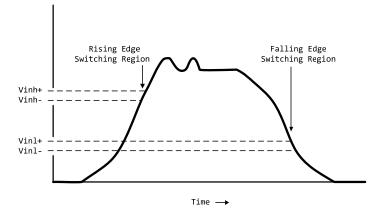

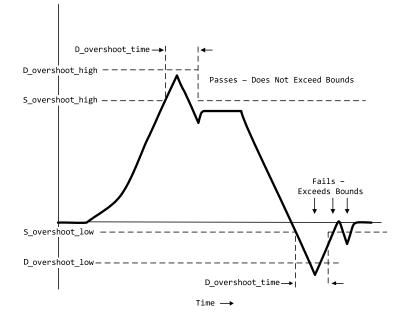

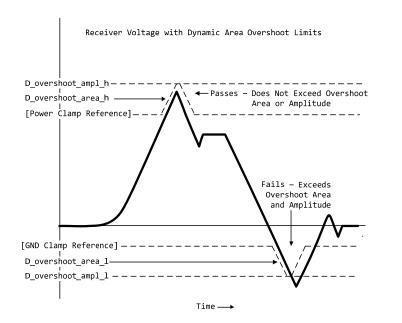

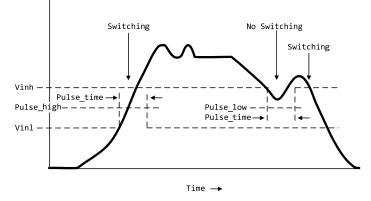

| [Model Spec]                                                                                                                                                                                                                                    | Vinh, Vinl, Vinh+, Vinh-, Vinl+,<br>Vinl-, S_overshoot_high,<br>S_overshoot_low, D_overshoot_high,<br>D_overshoot_low, D_overshoot_time,<br>D_overshoot_area_h,<br>D_overshoot_area_l,<br>D_overshoot_ampl_h,<br>D_overshoot_ampl_l,<br>Pulse_high, Pulse_low, Pulse_time,<br>Vmeas, Cref, Rref, Vref, Cref_rising,<br>Cref_falling, Rref_rising,<br>Rref_falling, Vref_rising,<br>Vref_falling, Vmeas_rising,<br>Vmeas_falling,<br>Rref_diff, Cref_diff,<br>Weak_R, Weak_I, Weak_V |

| [Receiver Thresholds]                                                                                                                                                                                                                           | Vth, Vth_min, Vth_max, Vinh_ac,<br>Vinh_dc, Vinl_ac, Vinl_dc,<br>Threshold_sensitivity,<br>Reference_supply, Vcross_low,<br>Vcross_high, Vdiff_ac, Vdiff_dc,<br>Tslew ac, Tdiffslew ac                                                                                                                                                                                                                                                                                              |

| [Add Submodel]         [Driver Schedule]         [Temperature Range]         [Voltage Range]         [Pullup Reference]         [Pulldown Reference]         [POWER Clamp Reference]         [GND Clamp Reference]         [External Reference] | Totem_ac, Tantotem_ac                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| [C Comp Corner]                                                                                                                                                                                                                                 | C_comp, C_comp_pullup,<br>C_comp_pulldown,<br>C_comp_power_clamp,<br>C_comp_gnd_clamp                                                                                                                                                                                                                                                                                                                                                                                               |

| [TTgnd]<br>[TTpower]                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

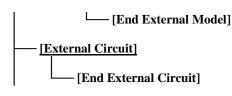

[Pulldown] [Pullup] [GND Clamp] [POWER Clamp] [ISSO PU] [ISSO PD] [Rgnd] [Rpower] [Rac] - [Cac] - [On] - [Off] - [R Series] - [L Series] - [RI Series] [C Series] [Lc Series] [Rc Series] [Series Current] [Series MOSFET] [Ramp] [Rising Waveform] - [Composite Current] [Falling Waveform] [Composite Current] [External Model] - [End External Model] [Algorithmic Model] - [End Algorithmic Model] [Begin EMI Model] └── [End EMI Model] [Submodel] --- [Submodel Spec]

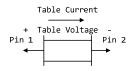

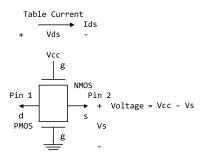

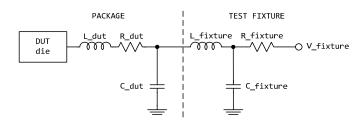

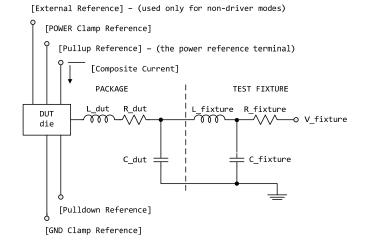

Vds dV/dt\_r, dV/dt\_f, R\_load R\_fixture, V\_fixture, V\_fixture\_min, V\_fixture\_max, C\_fixture, L\_fixture, R\_dut, L\_dut, C\_dut

R\_fixture, V\_fixture, V\_fixture\_min, V\_fixture\_max, C\_fixture, L\_fixture, R\_dut, L\_dut, C\_dut

Language, Corner, Parameters, Ports, D\_to\_A, A\_to\_D

Executable

Model\_emi\_type, Model\_Domain

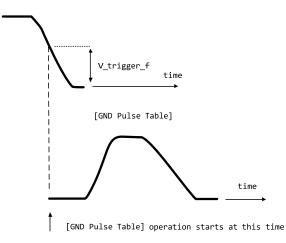

Submodel\_type V\_trigger\_r, V\_trigger\_f,

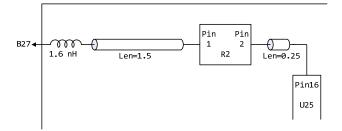

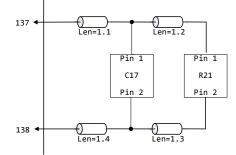

Len, L, R, C, Fork, Endfork

Banded\_matrix, Sparse\_matrix,

## IBIS 5.1 draft v135v140

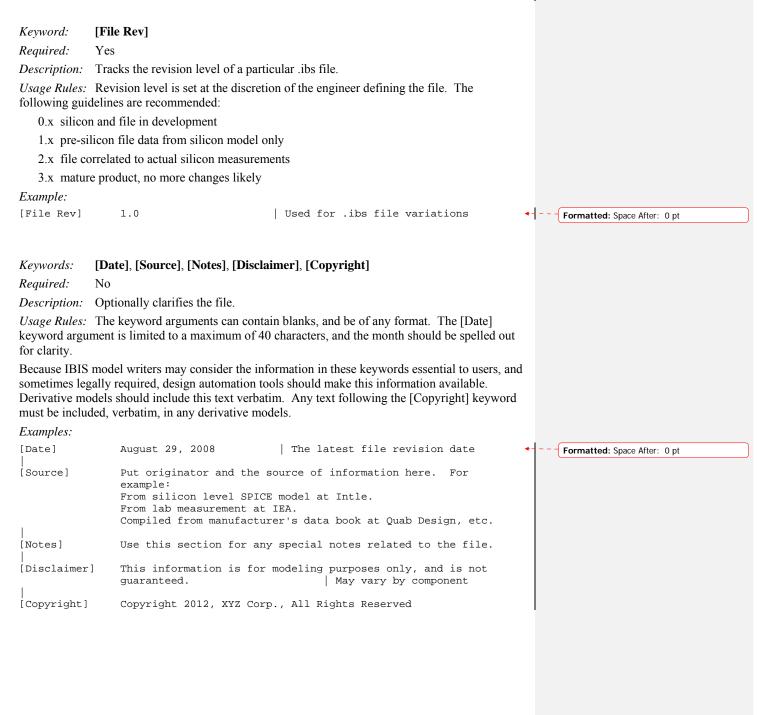

# **4** FILE HEADER INFORMATION

Keyword: [IBIS Ver]

Required: Yes

*Description:* Specifies the IBIS template version. This keyword informs electronic parsers of the kinds of data types that are present in the file.

*Usage Rules:* [IBIS Ver] must be the first keyword in any IBIS file. It is normally on the first line of the file, but can be preceded by comment lines that must begin with a "|".

Example:

[IBIS Ver] 5.1 | Used for template variations

### Keyword: [Comment Char]

Required: No

*Description:* Defines a new comment character to replace the default "|" (pipe) character, if desired.

*Usage Rules:* The new comment character to be defined must be followed by the underscore character and the letters "char". For example: "|\_char" redundantly redefines the comment character to be the pipe character. The new comment character is in effect only following the [Comment Char] keyword. The following characters MAY be used:

! " # \$ % & ' ( ) \* , : ; < > ? @ \ ^ ` { | } ~

*Other Notes:* The [Comment Char] keyword can be used anywhere in the file, as desired. *Example:*

[Comment Char] |\_char

Keyword: [File Name]

Required: Yes

Description: Specifies the name of the IBIS file.

*Usage Rules:* The file name must conform to the rules in paragraph 3 of Section 3, "GENERAL SYNTAX RULES AND GUIDELINES". In addition, the file name must use the extension ".ibs", ".pkg", or ".ebd". The file name must be the actual name of the file.

Example:

[File Name] ver5\_1.ibs

Formatted: Space After: 0 pt

IBIS 5.1 draft v135v140

# **5 COMPONENT DESCRIPTION**

Keyword: [Component]

Required: Yes

*Description:* Marks the beginning of the IBIS description of the integrated circuit named after the keyword.

Sub-Params: Si\_location, Timing\_location

*Usage Rules:* If the .ibs file contains data for more than one component, each section must begin with a new [Component] keyword. The length of the component name must not exceed 40 characters, and blank characters are allowed.

NOTE: Blank characters are not recommended due to usability issues.

Si\_location and Timing\_location are optional and specify where the Signal Integrity and Timing measurements are made for the component. Allowed values for either subparameter are "Die" or "Pin". The default location is at the "Pin".

Example:

| [Component]                    | 7403398    | MC452                                                         |

|--------------------------------|------------|---------------------------------------------------------------|

|                                |            |                                                               |

| Si_location<br>Timing_location | Pin<br>Die | Optional subparameters to give measurement location positions |

## Keyword: [Manufacturer]

Required: Yes

Description: Specifies the name of the component's manufacturer.

*Usage Rules:* The length of the manufacturer's name must not exceed 40 characters (blank characters are allowed, e.g., Texas Instruments). In addition, each manufacturer must use a consistent name in all .ibs files.

Example:

[Manufacturer] Intle NoName Corp.

Keyword: [Package]

Required: Yes

*Description:* Defines a range of values for the default packaging resistance, inductance, and capacitance of the component pins.

Sub-Params: R\_pkg, L\_pkg, C\_pkg

*Usage Rules:* The typical (typ) column must be specified. If data for the other columns are not available, they must be noted with "NA".

*Other Notes:* If RLC parameters are available for individual pins, they can be listed in columns 4-6 under keyword [Pin]. The values listed in the [Pin] description section override the default values defined here. Use the [Package Model] keyword for more complex package descriptions.

Formatted: Space After: 0 pt

- - Formatted: Space After: 0 pt

If defined, the [Package Model] data overrides the values in the [Package] keyword. Regardless, the data listed under the [Package] keyword must still contain valid data.

### Example:

| [Package] |        |        |        |

|-----------|--------|--------|--------|

| variable  | typ    | min    | max    |

| R_pkg     | 250.Om | 225.Om | 275.Om |

| L_pkg     | 15.0nH | 12.0nH | 18.0nH |

| C_pkg     | 18.0pF | 15.0pF | 20.0pF |

Keyword: [Pin]

*Required:* Yes

*Description:* Associates the component's I/O models to its various external pin names and signal names.

Sub-Params: signal\_name, model\_name, R\_pin, L\_pin, C\_pin

*Usage Rules:* All pins on a component must be specified. The first column must contain the pin name. The second column, signal\_name, gives the data book name for the signal on that pin. The third column, model\_name, maps a pin to a specific I/O buffer model or model selector name. Each model\_name must have a corresponding model or model selector name listed in a [Model] or [Model Selector] keyword below, unless it is a reserved model name (POWER, GND, or NC).

The model\_name column cannot be used for model or model selector names that reference Series and Series switch models.

Each line must contain either three or six columns. A pin line with three columns only associates the pin's signal and model. Six columns can be used to override the default package values (specified under [Package]) FOR THAT PIN ONLY. When using six columns, the headers R\_pin, L\_pin, and C\_pin must be listed. If "NA" is in columns 4 through 6, the default packaging values must be used. The headers R\_pin, L\_pin, and C\_pin may be listed in any order.

Column length limits are:

| [Pin]       | 5 characters max  |

|-------------|-------------------|

| model_name  | 40 characters max |

| signal_name | 40 characters max |

| R_pin       | 9 characters max  |

| L_pin       | 9 characters max  |

| C pin       | 9 characters max  |

Example:

| [Pin]<br> | signal_name | model_name | R_pin  | L_pin | C_pin |

|-----------|-------------|------------|--------|-------|-------|

| 1         | RAS0#       | Buffer1    | 200.Om | 5.0nH | 2.0pF |

| 2         | RAS1#       | Buffer2    | 209.Om | NA    | 2.5pF |

| 3         | EN1#        | Input1     | NA     | 6.3nH | NA    |

| 4         | A0          | 3-state    |        |       |       |

| 5         | DO          | I/01       |        |       |       |

| 6         | RD#         | Input2     | 310.Om | 3.0nH | 2.0pF |

- - Formatted: Space After: 0 pt

## - - Formatted: Space After: 0 pt

| 7<br>8<br>9<br>10<br>11<br>12<br> | WR#<br>Al<br>Dl<br>GND<br>RDY#<br>GND | Input2<br>I/O2<br>I/O2<br>GND<br>Input2<br>GND            |                  | 6.7nH<br>5.3nH | 3.4pF<br>4.0pF                    |

|-----------------------------------|---------------------------------------|-----------------------------------------------------------|------------------|----------------|-----------------------------------|

| 18<br>19<br>20<br>21<br>22        | Vcc3<br>NC<br>Vcc5<br>BAD1<br>BAD2    | POWER<br>NC<br>POWER<br>Series_switchl<br>Series_selector | 226.0m<br> <br>L | 5              | 1.0pF<br>assignment<br>assignment |

| Keyword: [I | Package | Model |

|-------------|---------|-------|

|-------------|---------|-------|

Required: No

*Description:* Indicates the name of the package model to be used for the component.

*Usage Rules:* The package model name is limited to 40 characters. Spaces are allowed in the name. The name should include the company name or initials to help ensure uniqueness. The EDA tool will search for a matching package model name as an argument to a [Define Package Model] keyword in the current IBIS file first. If a match is not found, the EDA tool will next look for a match in an external .pkg file. If the matching package model is in an external .pkg file, it must be located in the same directory as the .ibs file. The file names of .pkg files must follow the rules for file names given in Section 3, "GENERAL SYNTAX RULES AND GUIDELINES".

*Other Notes:* Use the [Package Model] keyword within a [Component] to indicate which package model should be used for that component. The specification permits .ibs files to contain [Define Package Model] keywords as well. These are described under "Package Modeling" in Section 7. When package model definitions occur within a .ibs file, their scope is "local", i.e., they are known only within that .ibs file and no other. In addition, within that .ibs file, they override any globally defined package models that have the same name.

## Example:

[Package Model] QS-SMT-cer-8-pin-pkgs

Formatted: Space After: 0 pt

### Keywords: [Alternate Package Models], [End Alternate Package Models]

Required: No

Description: Used to select a package model from a list of package models.

*Usage Rules:* The [Alternate Package Models] keyword can be used in addition to the [Package Model] keyword. [Alternate Package Models] shall be used only for components that use the [Package Model] keyword.

Each [Alternate Package Models] keyword specifies a set of alternate package model names for only one component, which is given by the previous [Component] keyword. The [Alternate Package Models] keyword shall not appear before the first [Component] keyword in an IBIS file.

### IBIS 5.1 draft v135v140

The [Alternate Package Models] keyword applies only to the [Component] section in which it appears, and must be followed by an [End Alternate Package Models] keyword.

All alternate package model names must appear below the [Alternate Package Models] keyword, and above the following [End Alternate Package Models] keyword. The package model names listed under the [Alternate Package Models] must follow the rules of the package model names associated with the [Package Model] keyword. The package model names correspond to the names of package models defined by [Define Package Model] keywords. EDA tools may offer users a facility for choosing between the default package model and any of the alternate package models, when analyzing occurrences of the [Component].

The package model named by [Package Model] can be optionally repeated in the [Alternate Package Models] list of names.

### Example:

```

[Alternate Package Models]

```

```

208-pin_plastic_PQFP_package-even_mode | Descriptive names are shown

208-pin_plastic_PQFP_package-odd_mode

208-pin_ceramic_PQFP_package-even_mode

208-pin_ceramic_PQFP_package-odd_mode

```

[End Alternate Package Models]

### Keyword: [Pin Mapping]

Required: No

*Description:* Used to indicate the power and/or ground buses to which a given driver, receiver or terminator is connected.

Sub-Params: pulldown\_ref, pullup\_ref, gnd\_clamp\_ref, power\_clamp\_ref, ext\_ref

*Usage Rules:* The [Pin Mapping] keyword names the connections between POWER and/or GND pins and buffer and/or terminator voltage supply references using unique bus labels. All buses with identical labels are assumed to be connected with an ideal short. Each label must be associated with at least one pin whose model\_name is POWER or GND. Bus labels must not exceed 15 characters.

Each line must contain either three, five or six entries. Use the reserved word NC where an entry is required but a bus connection is not made.

The first column contains a pin name. Each pin name must match one of the pin names declared in the [Pin] section of the [Component].

For buffers and terminators, the remaining columns correspond to the voltage supply references for the named pin. Each [Model] supply reference is connected to a particular bus through a bus label in the corresponding column.

The second column, pulldown\_ref, designates the ground bus connections for the buffer or termination associated with that pin. The bus named under pulldown\_ref is associated with the [Pulldown] I-V table for non-ECL [Model]s. This is also the bus associated with the [GND Clamp] I-V table and the [Rgnd] model unless overridden by a label in the gnd\_clamp\_ref column.

#### Formatted: Space After: 0 pt

The third column, pullup\_ref, designates the power bus connection for the buffer or termination. The bus named under pullup\_ref is associated with the [Pullup] table for non-ECL [Model]s (for ECL models, this bus is associated with the [Pulldown] table). This is also the bus label associated with the [POWER Clamp] I-V table and the [Rpower] model unless overridden by a label in the power\_clamp\_ref column.

The fourth and fifth columns, gnd\_clamp\_ref and power\_clamp\_ref, contain entries, if needed, to specify additional ground bus and power bus connections for clamps. Finally, the sixth column, ext\_ref, contains entries to specify external reference supply bus connections.

The usage of the columns changes for GND and POWER pins. For GND pins, the pulldown\_ref column contains the name of the bus to which the pin connects; the pullup\_ref column in this case must contain the reserved word NC. Similarly, for POWER (including external reference) pins, the pullup\_ref column contains the name of the bus to which the pin connects; the pulldown\_ref column in this case must contain the reserved word NC.

If the [Pin Mapping] keyword is present, then the bus connections for EVERY pin listed under the [Pin] keyword must be given.

If a pin has no connection, then both the pulldown\_ref and pullup\_ref subparameters for it will be NC.

The column length limits are:

| [Pin Mapping]   | 5 characters max  |

|-----------------|-------------------|

| pulldown_ref    | 15 characters max |

| pullup_ref      | 15 characters max |

| gnd_clamp_ref   | 15 characters max |

| power_clamp_ref | 15 characters max |

| ext_ref         | 15 characters max |

For compatibility with models developed under previous IBIS versions, [Pin Mapping] lines which contain ext\_ref column entries must also explicitly include entries for the pulldown\_ref, pullup\_ref, gnd\_clamp\_ref and power\_clamp\_ref columns. These entries can be NC.

When six columns of data are specified, the headings gnd\_clamp\_ref, power\_clamp\_ref and ext\_ref must be used on the line containing the [Pin Mapping] keyword. Otherwise, these headings can be omitted.

Example: [Pin Mapping] pulldown\_ref pullup\_ref gnd\_clamp\_ref power\_clamp\_ref ext\_ref 1 GNDBUS1 PWRBUS1 Signal pins and their associated 2 GNDBUS2 PWRBUS2 ground, power and external reference connections 3 GNDBUS1 PWRBUS1 GNDCLMP PWRCLAMP 4 5 6 7 GNDBUS2 PWRBUS2 GNDCLMP PWRCLAMP GNDBUS2 PWRBUS2 PWRCLAMP REFBUS1 NC GNDBUS2 PWRBUS2 GNDCLMP NC GNDBUS2 PWRBUS2 GNDCLMP NC REFBUS2 Some possible clamping connections are shown above for illustration purposes

- - Formatted: Space After: 0 pt

# IBIS 5.1 draft v135v140

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDBUS1                                                                                                                                                                                          | NC                                                         |              | One set of ground connections.                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDBUS1                                                                                                                                                                                          | NC                                                         |              | NC indicates no connection to                                                                                                             |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDBUS1                                                                                                                                                                                          | NC                                                         |              | power bus.                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDBUS2                                                                                                                                                                                          | NC                                                         |              | Second set of ground connections                                                                                                          |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDBUS2                                                                                                                                                                                          | NC                                                         |              |                                                                                                                                           |

| 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDBUS2                                                                                                                                                                                          | NC                                                         |              |                                                                                                                                           |

| .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRBUS1                                                    |              | One set of power connections.                                                                                                             |

| 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRBUS1                                                    |              | NC indicates no connection to                                                                                                             |

| 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRBUS1                                                    |              | ground bus.                                                                                                                               |

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRBUS2                                                    |              | Second set of power connections                                                                                                           |

| 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRBUS2                                                    |              |                                                                                                                                           |

| 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRBUS2                                                    |              |                                                                                                                                           |

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GNDCLMP                                                                                                                                                                                          | NC                                                         |              | Additional power connections                                                                                                              |

| 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | PWRCLMP                                                    |              | for clamps                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | REFBUS1                                                    |              | External reference connections                                                                                                            |

| 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                               | REFBUS2                                                    |              |                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| The followin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | g [Pin] list                                                                                                                                                                                     | t correspon                                                | lds          | to the [Pin Mapping] shown above.                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |                                                            |              |                                                                                                                                           |

| <br>[Pin] signal_n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ame model_na                                                                                                                                                                                     | ame R_pin L                                                | _p           | in C_pin                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  | _                                                          | q_i          |                                                                                                                                           |

| <br>1 OUT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | output_                                                                                                                                                                                          | _buffer1                                                   | q            | in C_pin<br>  Output buffers                                                                                                              |

| <br>1 OUT1<br>2 OUT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | output_<br>output_                                                                                                                                                                               | _buffer1<br>_buffer2                                       | q            | Output buffers                                                                                                                            |

| <br>1 OUT1<br>2 OUT2<br>3 IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | output_<br>output_<br>io_buff                                                                                                                                                                    | _buffer1<br>_buffer2<br>fer1                               | _p           |                                                                                                                                           |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | output_<br>output_<br>io_buff<br>io_buff                                                                                                                                                         | _buffer1<br>_buffer2<br>fer1<br>fer2                       | _p           | Output buffers                                                                                                                            |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1                                                                                                                                                                                                                                                                                                                                                                                                                                                           | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf                                                                                                                                              | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1              | _p           | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no                                                                 |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2                                                                                                                                                                                                                                                                                                                                                                                                                                             | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>io_buff                                                                                                                                   | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | p            | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3                                                                                                                                                                                                                                                                                                                                                                                                                               | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>io_buff<br>ref_buf                                                                                                                        | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | _p           | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no                                                                 |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1                                                                                                                                                                                                                                                                                                                                                                                                                    | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>ref_buf<br>ref_buf                                                                                                                        | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | p            | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1                                                                                                                                                                                                                                                                                                                                                                                                         | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>ref_buf<br>GND<br>GND                                                                                                                     | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | ď            | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1                                                                                                                                                                                                                                                                                                                                                                                              | output_<br>output_<br>io_buff<br>io_buff<br>io_buff<br>ref_buf<br>GND<br>GND<br>GND                                                                                                              | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | <b>q_</b> -ı | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>21 VSS2                                                                                                                                                                                                                                                                                                                                                                                   | output_<br>output_<br>io_buff<br>io_buff<br>ref_buff<br>ref_buff<br>GND<br>GND<br>GND<br>GND                                                                                                     | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | qı           | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>21 VSS2<br>22 VSS2                                                                                                                                                                                                                                                                                                                                                                        | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>ref_buf<br>GND<br>GND<br>GND<br>GND<br>GND                                                                                                | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | qı           | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>21 VSS2<br>22 VSS2<br>23 VSS2                                                                                                                                                                                                                                                                                                                                                             | output_<br>output_<br>io_buff<br>io_buff<br>ref_buff<br>ref_buff<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND                                                                                | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | q_ı          | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>21 VSS2<br>22 VSS2<br>23 VSS2<br>31 VCC1                                                                                                                                                                                                                                                                                                                                                                | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>ref_buff<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>POWER                                                                        | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | <u>p_</u> 1  | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>13 VSS1<br>21 VSS2<br>22 VSS2<br>23 VSS2<br>31 VCC1<br>32 VCC1                                                                                                                                                                                                                                                                                                                            | output_<br>output_<br>io_buff<br>io_buff<br>ref_buff<br>ref_buff<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>POWER<br>POWER                                                              | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | ď            | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>13 VSS1<br>21 VSS2<br>22 VSS2<br>23 VSS2<br>31 VCC1<br>33 VCC1                                                                                                                                                                                                                                                                                                                            | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>ref_buf<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>POWER<br>POWER<br>POWER                                                       | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | <u>م_</u> ا  | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |

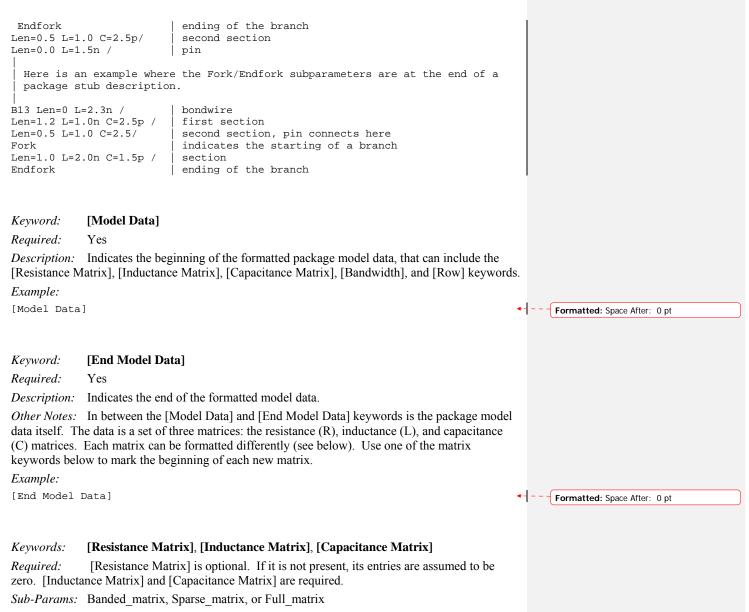

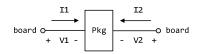

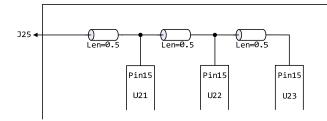

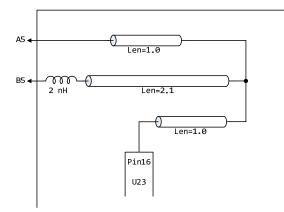

| <br>1 OUT1<br>2 OUT2<br>3 IO3<br>4 IO4<br>5 SPECIAL1<br>6 SPECIAL2<br>7 SPECIAL3<br>11 VSS1<br>12 VSS1<br>13 VSS1<br>13 VSS1<br>21 VSS2<br>22 VSS2<br>23 VSS2<br>23 VSS2<br>31 VCC1<br>32 VCC1<br>33 VCC1<br>41 VCC2                                                                                                                                                                                                                                                                                           | output_<br>output_<br>io_buff<br>io_buff<br>ref_buf<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>POWER<br>POWER<br>POWER<br>POWER<br>POWER                                                       | _buffer1<br>_buffer2<br>fer1<br>fer2<br>ffer1<br>fer_term1 | <b>đ</b> _r  | Output buffers<br>Input/output buffers<br>Buffers with POWER CLAMP but no<br>GND CLAMP I-V tables; two use                                |