# IBIS Based Buck Converter DC Modeling

### Zhiping Yang, Songping Wu, Shuai Jin, Zhenxue Xu

Google Inc.

IBIS Summit at 2020 IEEE Virtual Symposium on EMC+SIPI

August 28, 2020

### Objective

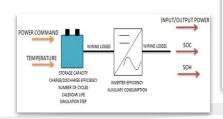

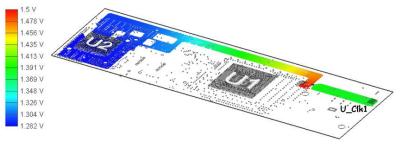

System-Level Power Simulation Coverage

- System level DC simulations, including IR drop, DC resistance

- AC simulations, i.e. PDN impedance

- Transient load response, i.e. transient power noise

- System power consumption and efficiency

- Power/thermal co-simulation

### Outline

- Background: DC simulation common methodology

- Proposed buck converter IBIS Model

- Validation by measurement

- Conclusion

- Future work

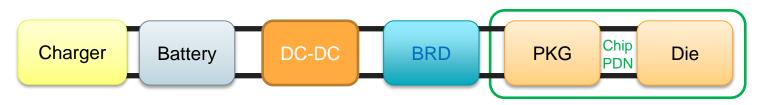

### Background: DC Simulation Common Methodology

- Charger & Battery not modeled. Model from DC-DC to Die IR drop.

- DC-DC model as voltage source

- BRD & all the passive components on board as a resistance network

- PKG resistance network

- Die as current sink/load

### Common DC Simulation Shortcomings and Proposal

- Shortcomings

- No DC-DC converter information. No power consumption or power efficiency information.

- Have to readout and key in current load and voltage source values for all the rails manually. Easy to make a mistake.

- Proposal

- DC-DC converter vendor to provide detailed chip model in IBIS format to model switching and conduction power loss.

- Advantage

- System power consumption and efficiency can be evaluated.

- With the DC-DC converter IBIS model available, DC simulation for all power rails can be set up automatically.

- Efficient to optimize the PCB layout.

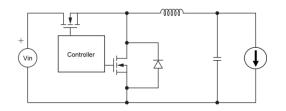

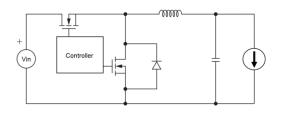

#### Introduction to Buck Converter

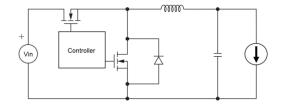

• Buck converter is composed of two switches, one inductor and capacitors.

Buck converter is step down DC-DC converter. It converts high voltage to low voltage and serves as voltage source to the sink IC. It is a type of switching mode power supply (SMPS). It provides much higher power efficiency than a linear regulator.

#### Proposed Buck Converter IBIS Model Standard Format

The proposed IBIS model includes the following key parameters.

#### Device physical parameters (from vendor)

Inductor

- 1) Inductance: L

- 2) Inductor ESR: R<sub>L\_ESR</sub>

#### High side switch

- 1) Resistance when high side MOSFET is on:  $R_{on HS}$

- 2) Rising time and falling time of high side MOSFET:  $t_{\text{on\_HS}}$  and  $t_{\text{off\_HS}}$

- 3) FET gate charge on high side MOSFET:  $Q_{FET_G_{HS}}$

- 4) MOSFET output capacitance on high side: Coss\_HS

#### Low side switch

- 1) Resistance when low side MOSFET is on:  $R_{on\_LS}$

- 2) FET gate charge on low side MOSFET:  $Q_{FET_G_{LS}}$

- 3) Low side body diode charge:  $Q_{body\_diode\_LS}$

- 4) Low side body diode threshold voltage:  $V_{th}$

- 5) MOSFET output capacitance on low side:  $C_{oss\_LS}$

#### System controlled parameters (from designer)

- 1) Input voltage: V<sub>in</sub>

- 2) Output voltage: V<sub>o</sub>

- 3) Output current: I<sub>o</sub>

- 4) Switching frequency: freq

- 5) Gate drive voltage: V<sub>gs</sub>

- 6) Dead time for rising and falling:  $t_{r\_dead}$  and  $t_{f\_dead}$ ; the dead time is the time to turn off both FETs to avoid shunt through current from power directly to ground.

#### **Referenced Power Consumption Calculation**

- The proposed IBIS model parameters are shown in the previous slide. The simulation tool defines how to use these parameters to calculate the power consumption in their own solver. The referenced equations to calculate buck converter power consumption in CCM are shown in the following pages.

- The buck converter power loss mainly comes from three parts: inductor conduction loss, FET conduction loss and FET switching loss. The loss from capacitors are relatively small and are not included. The PCB DCR loss can be obtained from the EDA tool.

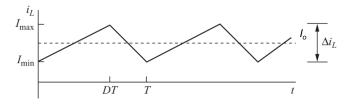

# **Continuous Current Mode**

#### Non-ideal Buck Converter DC Modeling (1)

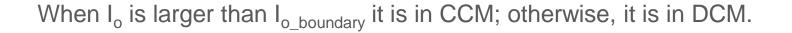

The following formulas are for the CCM mode.

• Inductor conduction loss: P<sub>L\_ESR</sub>= I<sub>L\_rms</sub><sup>2</sup>\*R<sub>L\_ESR</sub>

where  $I_{L_{rms}}$ =sqrt( $I_{o}^{2}$ + $I_{L_{delta}}^{2}$ /12) and  $R_{L_{ESR}}$  is the inductor ESR;

I<sub>o</sub> is the load current;

$I_{L_{delta}} = (V_{in} - V_o) * D/freq/L;$

V<sub>in</sub> and V<sub>o</sub> are input and output voltage for the buck converter, respectively;

D is duty cycle equal to  $V_o/V_{in}$ ;

freq is the switching frequency;

L is the inductance.

#### Non-ideal Buck Converter DC Modeling (2)

• High side MOSFET conduction Loss: P<sub>CL\_HS</sub> = I<sub>rms\_HS</sub><sup>2</sup>\*R<sub>on\_HS</sub>

where  $R_{on_{LS}}$  is conduction resistance on high side FET and  $I_{rms_{HS}}$ =sqrt(D)\* $I_{L_{rms}}$

• High side switching loss:  $P_{SL_{HS}}=0.5*V_{in}*(I_{L_{min}}*t_{on_{HS}}+I_{L_{max}}*t_{off_{HS}})*freq$

where  $V_{in}$  is input voltage;  $I_{L_{min}}$  and  $I_{L_{max}}$  are minimum inductor current ( $I_o$ -0.5\* $I_{delta}$ ) and maximum inductor current( $I_o$ +0.5\* $I_{delta}$ ), respectively;  $t_{on_{HS}}$  and  $t_{off_{HS}}$  are rising time and falling time, respectively.

• High side Gate Drive Loss: P<sub>GDL\_HS</sub>=V<sub>GS</sub>\*Q<sub>FET\_G\_HS</sub>\*freq

where  $V_{GS}$  is the gate drive voltage;  $Q_{FET_G_{HS}}$  is the high side MOSFET gate charge.

• High side FET Coss Loss: P<sub>CL\_HS</sub>=0.5\*C<sub>oss\_HS</sub>\*V<sub>in</sub><sup>2</sup>\*freq

where  $C_{oss_{HS}}$  is the high side MOSFET output capacitance.

#### Non-ideal Buck Converter DC Modeling (3)

• Low side MOSFET conduction Loss: P<sub>CL\_LS</sub>= I<sub>rms\_LS</sub><sup>2</sup>\*R<sub>on\_LS</sub>

where  $I_{rms_{LS}}$ =sqrt(1-D)\* $I_{L_{rms}}$ ;

I<sub>L\_rms</sub> is the inductor rms current;

R<sub>on\_LS</sub> is conduction resistance on low side FET.

#### Non-ideal Buck Converter DC Modeling (4)

• Low side body diode reverse recovery loss: P<sub>BDRRL\_LS</sub>=V<sub>in</sub>\*Q<sub>body\_diode\_LS</sub>\*freq

*where* **Q**<sub>body\_diode\_LS</sub> is reverse distributed charge when high side MOSFET is on and reverse bias is applied.

• Low side body diode conduction loss:  $P_{BDCL_{LS}} = V_{th} * (I_{L_{min}} * t_{r_{dead}} + I_{L_{max}} * t_{f_{dead}}) * freq$

where  $V_{th}$  is the diode threshold voltage, 0.7V.  $t_{r_{dead}}$  and  $t_{f_{dead}}$  are the dead time for rising and falling, respectively.

Low side gate drive loss: P<sub>GDL\_LS</sub>=V<sub>GS</sub>\*Q<sub>FET\_G\_LS</sub>\*freq

where  $Q_{FET_G_{LS}}$  is the low side MOSFET gate charge.

• Low side FET Coss loss: P<sub>CL\_LS</sub>=0.5\*C<sub>oss\_LS</sub>\*freq\*V<sub>in</sub><sup>2</sup>

where  $C_{oss\_LS}$  is the low side MOSFET output capacitance.

#### **Summary of Buck Converter Power Consumption**

The total power loss is the summation of the inductor DCR loss, the FET conduction loss and the FET switching loss.

| Inductor conduction loss                  | $P_{L_ESR} = I_{L_rms}^{2*} R_{L_ESR}$                                                    |

|-------------------------------------------|-------------------------------------------------------------------------------------------|

| High side MOSFET conduction loss          | $P_{CL_{HS}} = I_{ms_{HS}}^{2*} R_{on_{HS}}$                                              |

| High side switching loss                  | $P_{SL\_HS} = 0.5^* V_{in}^* (I_{L\_min}^* t_{on\_HS} + I_{L\_max}^* t_{off\_HS})^* freq$ |

| High side Gate Drive Loss                 | P <sub>GDL_HS</sub> =V <sub>GS</sub> *Q <sub>FET_G_HS</sub> *freq                         |

| High side FET Coss Loss                   | $P_{CL_{HS}}=0.5*C_{oss_{HS}}*V_{in}^{2}*freq$                                            |

| Low side MOSFET conduction loss           | $P_{CL\_LS} = I_{rms\_LS}^{2*} R_{on\_LS}$                                                |

| Low side body diode reverse recovery loss | $P_{BDRRL_{L}S} = V_{in}^* Q_{body\_diode\_{L}S}^* freq$                                  |

| Low side body diode conduction loss       | $P_{BDCL\_LS} = V_{th}^* (I_{L\_min}^* t_{r\_dead}^* + I_{L\_max}^* t_{f\_dead})^* freq$  |

| Low side gate drive loss                  | $P_{GDL_LS} = V_{GS} * Q_{FET_G_LS} * freq$                                               |

| Low side FET Coss loss                    | $P_{CL_{LS}}=0.5*C_{oss_{LS}}*freq*V_{in}^{2}$                                            |

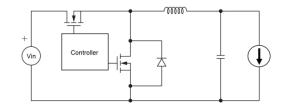

#### Criteria for CCM and DCM

The boundary for CCM and DCM is:

$I_{L_ripple} = \frac{1}{2} | I_{L_delta}$ = (V<sub>in</sub>-V<sub>o</sub>)\*D/freq/L/2; CCM: I<sub>o</sub>>I<sub>L\_ripple</sub> DCM: I<sub>o</sub><I<sub>L\_ripple</sub>

$I_{o\_boundary} = (V_{in} - V_o)V_o / (2V_{in} + L^{+}freq)$

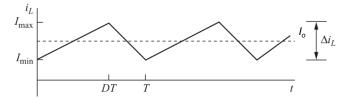

# **Discontinuous Current Mode**

#### Non-ideal Buck Converter DC Modeling (1)

The following formulas are for the DCM mode.

• Inductor conduction loss: P<sub>L\_ESR</sub>= I<sub>L\_rms</sub><sup>2</sup>\*R<sub>L\_ESR</sub>

where  $I_{L_{rms}}=I_{L_{pk}}$ \*sqrt(( $D_1+D_2$ )/3) and  $R_{L_{ESR}}$  is the inductor ESR;

$I_{L_pk}$ =sqrt( $V_o*I_o*2(V_{in}-V_o)/V_{in}/L/freq$ ), is the peak inductor current; Note: the efficiency is assumed to be 100% for the peak current calculation.

$V_{in}$  and  $V_o$  are input and output voltage for the buck converter, respectively;  $I_o$  is the load current;

$D_1 = I_{L_pk} / (V_{in} - V_o) * L*freq;$

$D_2 = I_{L_pk} / V_o * L*freq;$

freq is the switching frequency;

L is the inductance.

#### Non-ideal Buck Converter DC Modeling (2)

• High side MOSFET conduction Loss: P<sub>CL\_HS</sub>= I<sub>rms\_HS</sub><sup>2</sup>\*R<sub>on\_HS</sub>

where  $R_{on_{LS}}$  is conduction resistance on high side FET and  $I_{rms_{HS}}$ =sqrt( $D_1/3$ )\* $I_{L_pk}$ ;

• High side switching loss: P<sub>SL\_HS</sub>=0.5\*V<sub>in</sub>\*I<sub>L\_pk</sub>\*t<sub>off\_HS</sub>\*freq

where  $V_{in}$  is input voltage;  $I_{L_{pl}}$  is peak inductor current;  $t_{off_{HS}}$  is the FET falling time.

• High side Gate Drive Loss: P<sub>GDL\_HS</sub>=V<sub>GS</sub>\*Q<sub>FET\_G\_HS</sub>\*freq

where  $V_{GS}$  is the gate drive voltage;  $Q_{FET_G_{HS}}$  is the high side MOSFET gate charge.

• High side FET Coss Loss: P<sub>CL\_HS</sub>=0.5\*C<sub>oss\_HS</sub>\*V<sub>in</sub><sup>2</sup>\*freq

where  $C_{oss_{HS}}$  is the high side MOSFET output capacitance.

#### Non-ideal Buck Converter DC Modeling (3)

• Low side MOSFET conduction Loss: P<sub>CL\_LS</sub>= I<sub>rms\_LS</sub><sup>2\*</sup>R<sub>on\_LS</sub>

where  $I_{rms_LS}$ =sqrt( $D_2/3$ )\* $I_{L_pk}$ ;  $R_{on_LS}$  is conduction resistance on low side FET.

• Low side body diode conduction loss:  $P_{BDCL_{LS}} = V_{th} * I_{L_{pk}} * t_{f_{dead}} * freq$

where  $V_{th}$  is the diode threshold voltage, 0.7V.  $t_{r_{dead}}$  and  $t_{f_{dead}}$  are the dead time for rising and falling, respectively.

• Low side gate drive loss: P<sub>GDL\_LS</sub>=V<sub>GS</sub>\*Q<sub>FET\_G\_LS</sub>\*freq

where  $Q_{FET_G_{LS}}$  is the low side MOSFET gate charge.

• Low side FET Coss loss: P<sub>CL\_LS</sub>=0.5\*C<sub>oss\_LS</sub>\*freq\*V<sub>in</sub><sup>2</sup>

where  $C_{oss_{LS}}$  is the low side MOSFET output capacitance.

#### **Summary of Buck Converter Power Consumption**

The total power loss is the summation of the inductor DCR loss, the FET conduction loss and the FET switching loss.

| Inductor conduction loss            | $P_{L_{ESR}} = I_{L_{ms}}^{2*} R_{L_{ESR}}$                   |

|-------------------------------------|---------------------------------------------------------------|

| High side MOSFET conduction loss    | $P_{CL_{HS}} = I_{rms_{HS}}^{2*} R_{on_{HS}}$                 |

| High side switching loss            | $P_{SL_{H}S} = 0.5^* V_{in} * I_{L_{P}k} t_{off_{H}S} * freq$ |

| High side Gate Drive Loss           | $P_{GDL_{HS}} = V_{GS} * Q_{FET_{G_{HS}}} * freq$             |

| High side FET Coss Loss             | $P_{CL_{HS}}=0.5^{*}C_{oss_{HS}}^{*}V_{in}^{2*}freq$          |

| Low side MOSFET conduction loss     | $P_{CL\_LS} = I_{rms\_LS}^{2*} R_{on\_LS}$                    |

| Low side body diode conduction loss | $P_{BDCL\_LS} = V_{th}^* I_{L\_max}^* t_{f\_dead}^* freq$     |

| Low side gate drive loss            | $P_{GDL_LS} = V_{GS} * Q_{FET_G_LS} * freq$                   |

| Low side FET Coss loss              | $P_{CL\_LS}=0.5^{*}C_{oss\_LS}^{*}freq^{*}V_{in}^{2}$         |

#### **Example: Power Consumption of a Buck Converter**

| Device<br>Parameters |                           | Value    |  | System<br>Parameters                | Value    |

|----------------------|---------------------------|----------|--|-------------------------------------|----------|

| Inductor             | L                         | 2.2 uH   |  | V <sub>in</sub>                     | 20 V     |

|                      | R <sub>L_ESR</sub>        | 21 mohm  |  | V <sub>o</sub>                      | 7.7 V    |

| High side<br>switch  | R <sub>on_HS</sub>        | 7 mohm   |  | I <sub>o</sub>                      | 1 A      |

|                      | t <sub>on_HS</sub>        | 3.4 ns   |  | freq                                | 1000 kHz |

|                      | t <sub>off_HS</sub>       | 2.4 ns   |  | t <sub>r_dead</sub>                 | 20 ns    |

|                      | Q <sub>FET_G_HS</sub>     | 8.9 nQ   |  | t <sub>f_dead</sub>                 | 20 ns    |

|                      | C <sub>oss_HS</sub>       | 300 pF   |  | V <sub>gs</sub>                     | 5 V      |

| Low side<br>switch   | R <sub>on_LS</sub>        | 2.1 mohm |  | Other<br>parameters<br>on the board | Value    |

|                      | Q <sub>FET_G_LS</sub>     | 33 nQ    |  |                                     |          |

|                      | Q <sub>body_diode_L</sub> | 5 nC     |  | $R_{before\_buck}$                  | 66 mohm  |

|                      | V <sub>th</sub>           | 0.7 V    |  | R <sub>after_buck</sub>             | 6 mohm   |

|                      | C <sub>oss_LS</sub>       | 1100 pF  |  | I <sub>controler_quiesce</sub>      | 30 mA    |

21

#### Conclusion

- The calculated power efficiency is validated with measurement.

- The proposed model can be used to evaluate the power loss and power efficiency of buck converter working in CCM and DCM.

# The END