# [PSIJ Sensitivity] in IBIS

Kinger Cai, Fern Nee Tan, Chi-te Chen August 2022

Hybrid IBIS Summit at IEEE Symposium on EMC+SIPI Spokane, Washington, USA August 5, 2022

### Presenter

### **Kinger Cai**, *Principal Engineer* Platform Electrical Architect, CCG, Intel Corp. Kinger.Cai@intel.com

Kinger Cai has been driving I+I strategy for Notebook platforms, and strategic PI design tool evolution in Client Computing Group. Kinger was awarded Ph. D by Shanghai Jiao Tong University in 2001, and MBA degree by W.P. Carey business school in ASU in 2008. Kinger works in signal & power integrity domains for 20+ years. Kinger holds 12 granted patents, and published 30+ papers.

- Background

- HSIO architecture: Serial & Parallel

- Status Quo, for jitter analysis

- New system jitter analysis methodology

- [PSIJ Sensitivity] in IBIS

- [PSIJ Sensitivity] application

- Next Steps

## Background

- Data speed-up => Less UI, less jitter budget

- PCle Gen3/4/5/6

- LP(G)/DDR3/4/5/6

- USB3/3.1/3.2/4, DP & THB

- Silicon Disaggregation => more complicated jitter implication

- EMIB (Embedded Multi-die Interconnect Bridge), Foveros (Die to Die Stacking), and WoW (Wafer-on-Wafer)

- Differentiated architecture

- Process evolution => lower operation voltage, less voltage margin

- 22/14/10/7/6/5/4/3nm & 20A/18A

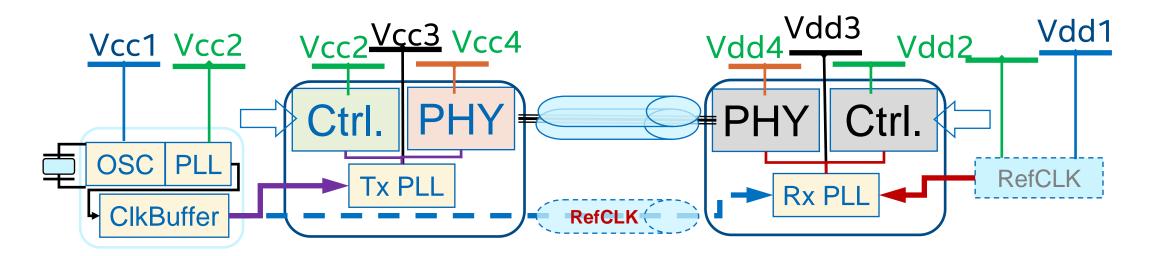

### HSIO Architecture Example: Serial or Parallel

- HSIO Tx/Rx PHY with EQ, and CDR in Rx PHY

- HSIO jitter, from Data and Clock, common or independent RefCLK

- HSIO jitter, from SI & PI, of multiple power supplies' PDNs

- HSIO jitter, of Dj and Rj, in pp or rms

Other names and brands may be claimed as the property of others. All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

## Status Quo, of Jitter Analysis

- SI & PI totally decoupled Sim, Tj=Tj<sub>-SI</sub>+Tj<sub>-PI</sub>(+Tj<sub>-PM</sub>+Tj<sub>-ctrl1</sub>+...)

- Over-design with direct superposition of the worst SI & PI cases in TD

- PSIJ heavily frequency-dependent to each circuit block cascaded in the path

- Jitter contribution from the other circuitry might not be included

- Jitter contribution significantly different upon different process technology, even for same IP

- SI-PI Co-Sim, Tj =Tj<sub>-Eye</sub>(+Tj<sub>-PM</sub>+Tj<sub>-ctrl1</sub>+...)

- Xtor model based, SI&PI co-sim,

- very time-consuming, almost impossible to include all circuitry

- Power-aware IBIS-AMI based sim

- More efficient, but less accuracy

- Jitter contribution from the other circuitry not included

- PM noise needs lab verification

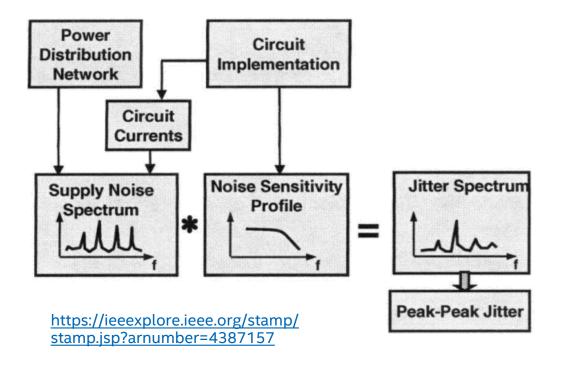

# Jitter Analysis with PSIJ Sensitivity

- Tj = Dj + Rj

- Rj refers to an intrinsic noise, upon BER

- Dj comes from SI channel and PI noise

- $Dj_{-Pl} = \sum_{i=1}^{N} IFFT[PSIJi * FFT(Vnoise_i)]$

- Dj<sub>-SI</sub> from SI simulation, assuming ideal power supplies

- System total Dj, Dj=Dj<sub>-SI</sub>+Dj<sub>-PI</sub>

Investigating the Impact of Supply Noise on the Jitter in Gigabit I/O Interfaces IEEE Topical Meeting on Electrical Performance of Electronic Packaging (EPEPS) Ralf Schmitt; Hai Lan; Chris Madden; Chuck Yuan, page 189-192, Oct. 2007

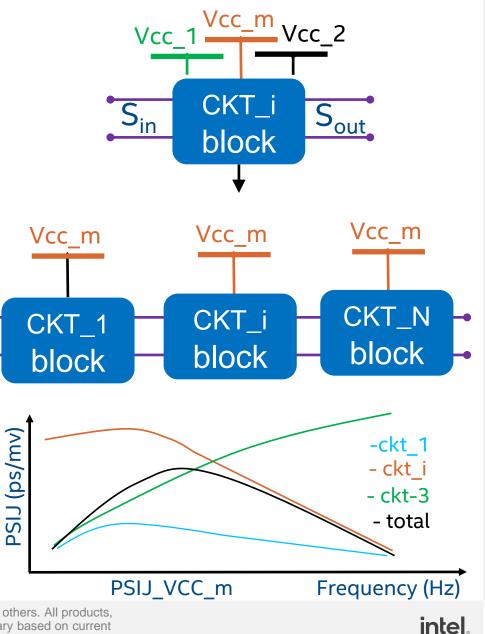

## **PSIJ** Sensitivity Derivation

- Set up VCC\_m= Vtyp+A\*sin(f),

- A=(Vmax-Vmin)/2,

- Keep all other power supplies at their own Vtyp

- Observe jitter impact, while sweeping f, to get PSIJ\_VCC\_m\_ckt\_i

- $PSIJ_VCC_m = \prod_{i=1}^{N} PSIJ_VCC_m_ckt_i$  or

- $= \sum_{i=1}^{N} PSIJ_VCC_m_ckt_i$  or

- = mix of  $\prod_{i=A}^{B} X$  and  $\sum_{j=C}^{D} Y$

- In equations, discrete {A, B, C, D} = {1, 2, ..., N}, and

- X, Y could be any combinations of  $PSIJ_VCC_m_ckt_{i/j}$

Other names and brands may be claimed as the property of others. All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

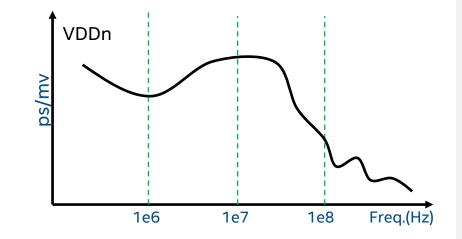

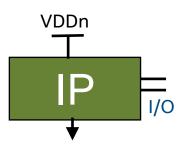

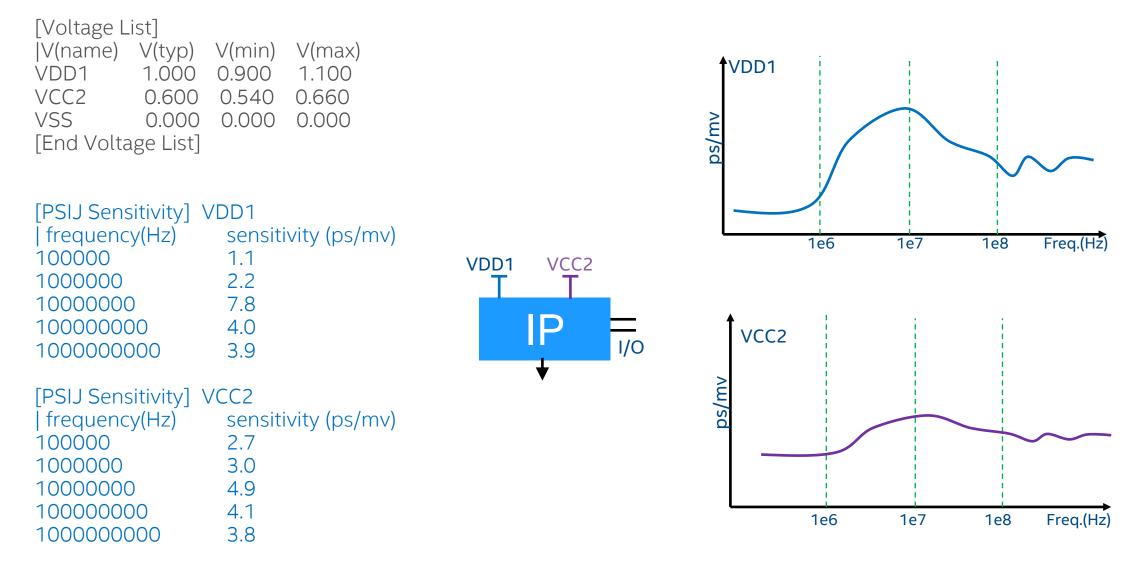

### Proposal of [PSIJ Sensitivity] in IBIS

- *Keyword:* **[PSIJ Sensitivity]** Power\_signal\_name (m)

- *Required:* Yes

- *Description:* Used to describe the power supply induced jitter sensitivity in PWL in frequency domain, for each power rail.

- Usage Rules: PSIJ Sensitivity in PWL format, for each power rail listed in [Voltage List], to evaluate the jitter impact to all the circuit blocks from its power supplies' noise respectively.

### Example:

| [PSIJ Sensitivity] VDDn |                     |

|-------------------------|---------------------|

| frequency(Hz)           | sensitivity (ps/mv) |

| 100000                  | 3.60                |

| 1000000                 | 3.10                |

| 1000000                 | 4.30                |

| 10000000                | 1.90                |

| 100000000               | 0.50                |

[Voltage List] |V(name) V(typ) V(min) V(max) VDDn 0.600 0.540 0.660 VSS 0.000 0.000 0.000 [End Voltage List]

Other names and brands may be claimed as the property of others. All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

intel. <sup>9</sup>

### Examples of [PSIJ Sensitivity] in IBIS

Other names and brands may be claimed as the property of others. All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

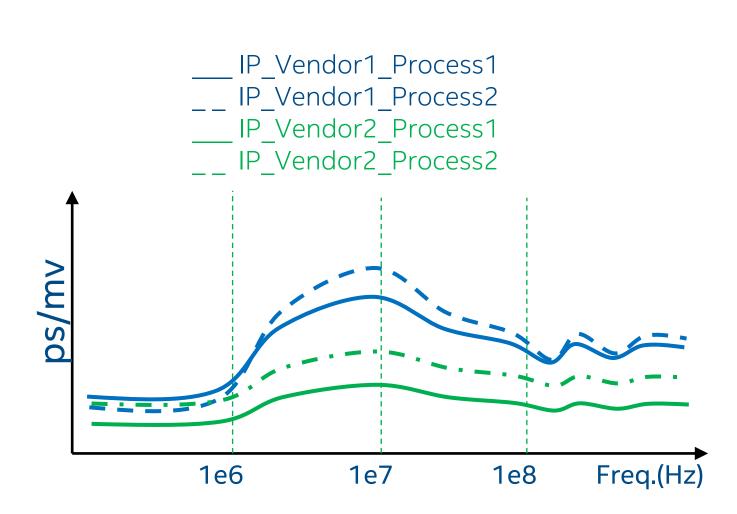

### Quick IP Selection, based upon [PSIJ Sensitivity]

- Same IP is better:

- from vendor2 than

- from vendor1

- Same IP is better:

- upon process1 than

- upon process2

- Same IP is the best

- from vendor2 and

- upon process1.

Other names and brands may be claimed as the property of others. All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

Next Steps

- Submit IBIS BIRD to include [PSIJ Sensitivity] in IBIS.

- Call for EDA vendors to support [PSIJ Sensitivity] in IBIS

- Call for chip vendors to support [PSIJ Sensitivity] in IBIS

- Call for platform designers to support [PSIJ Sensitivity] in IBIS

### Legal Disclaimer

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

Intel, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© 2022 Intel Corporation. All rights reserved.

# <section-header>

Kinger.cai@intel.com