# Add Support of Transient Analysis in SPIM, with [SPIM icct File]

SPIM = Streamlined Power Integrity Model

Kinger Cai, Chi-te Chen

July 2024

#### SPIM Status Quo & Expansion

- Supports in BIRD223.1, approved in Dec. 2023

- AC impedance, with [SPIM Touchstone File] and [SPIM Target]

- DC analysis, with [SPIM Rnetwork File] [SPIM Current] and [SPIM Voltage List]

- Add Support for Transient analysis

- Add [SPIM icct File], and its generation & application

- Add [SPIM Transient Target] for Peak-to-Peak noise Vpp, Vmin and Vmax

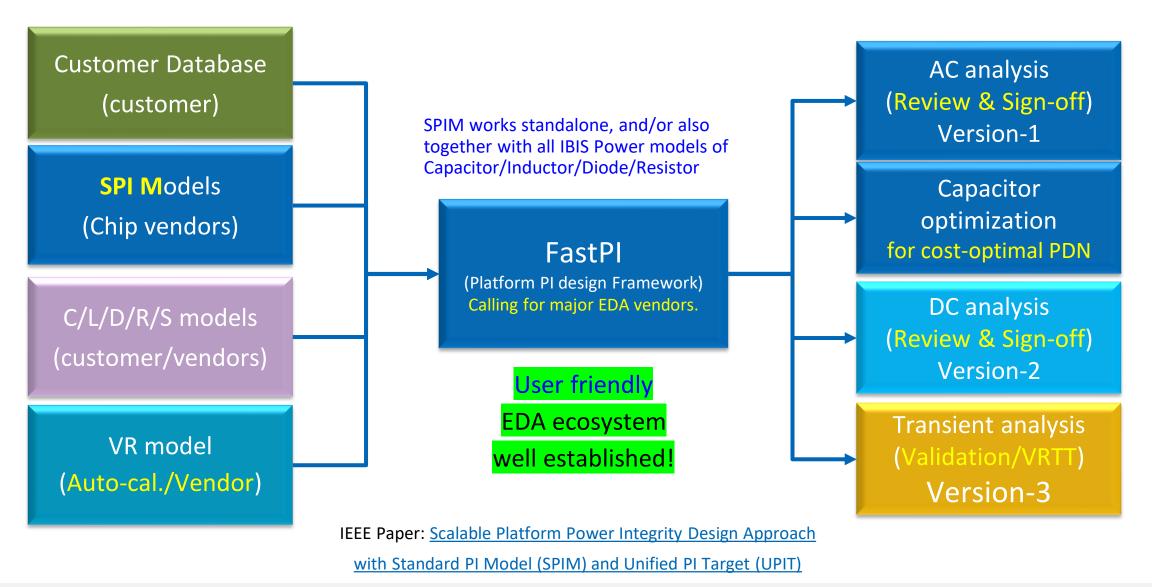

## FastPI (Platform PI Arch. with SPIM) Roadmap

Tree Structure of .spim FILE (Defined in BIRD223.1)

```

.spim FILE

-- [SPIM Touchstone File]

-- File Header Section

|-- [SPIM Stimulus]

|-- [IBIS Ver]

|-- [Comment Char]

|-- [End SPIM Stimulus]

|-- [SPIM Target]

|-- [File Name]

|-- [File Rev]

|-- [SPIM Observation Port]

|-- [Date]

|-- [End SPIM Target]

|-- [Source]

|-- [End SPIM Touchstone File]

|-- [Notes]

|-- [Disclaimer]

|-- [Copyright]

[SPIM Rnetwork File]

|-- [SPIM Current]

[Device SPIM]

|-- [Manufacturer]

|-- [End SPIM Current]

-- [Description]

|-- [SPIM Voltage List]

|-- [End SPIM Voltage List]

[SPIM Rail]

|-- [End SPIM Rnetwork File]

|-- [SPIM Pin Cluster]

Insert new

|-- [End SPIM Rail]

keywords.

|-- [End SPIM Pin Cluster]

|-- [End Device SPIM]

[SPIM Port List]

|-- [End]

|-- [End SPIM Port List]

```

## .spim FILE Tree Structure Implication & Example

```

SPIM Rnetwork Filel

-- [SPIM Current]

|-- [End SPIM Current]

-- [SPIM Voltage List]

|-- [End SPIM Voltage List]

|-- [End SPIM Rnetwork File]

[SPIM icct File]

|-- [SPIM Transient Target]

|-- [SPIM Observation Port]

|-- [End SPIM Transient Target]

|-- [End SPIM icct File]

|-- [End SPIM Rail]

|-- [End Device SPIM]

|-- [End]

```

```

Information for Transient analysis

[SPIM icct File]

Text file in two columns of time and current amplitude

File name

Time Delay

Repeat time

Intel CPU VCC1 icct.txt 0.0

[SPIM Transient Target]

[SPIM Observation Port] OB Sense

qqV

Vmin

Vmax

0.600

1.400

NA

[End SPIM Transient Target]

[End SPIM icct File]

[End SPIM Rail]

[End Device SPIM]

[End]

```

## Example .spim FILE -Supports Transient Analysis

```

Information for Transient analysis

[SPIM icct File]

File name Time Delay Repeat time

Intel CPU VCC1 icct.txt 0.0

0.0

[SPIM Transient Target]

[SPIM Observation Port] OB Sense

qqV

Vmin

Vmax

0.600

1.400

NA

[End SPIM Transient Target]

[End SPIM icct File]

```

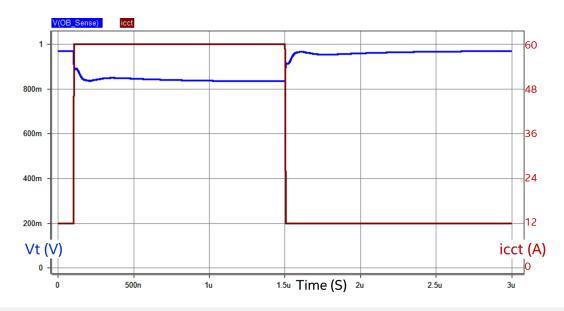

#### Intel\_CPU\_VCC1\_icct.txt

| *time (second) | Current(A) |  |

|----------------|------------|--|

| 0.00000E+00    | 2          |  |

| 100.000E-09    | 2          |  |

| 105.000E-09    | 10         |  |

| 1500.00E-09    | 10         |  |

| 1505.00E-09    | 2          |  |

| 3000.00E-09    | 2          |  |

|                |            |  |

Fig.1 icct generation

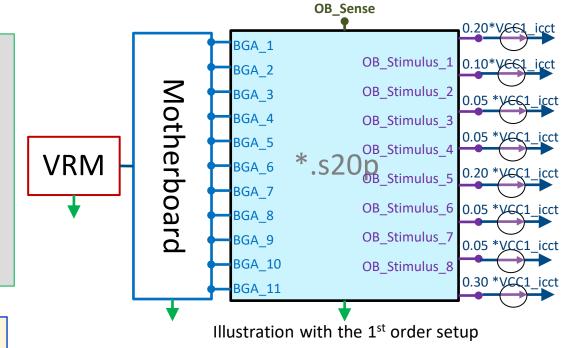

#### SPIM Transient Analysis Setup

#### Intel\_CPU\_VCC1\_icct.txt

| *time (second) | Current(A) |  |

|----------------|------------|--|

| 0.00000E+00    | 2          |  |

| 100.000E-09    | 2          |  |

| 105.000E-09    | 10         |  |

| 1500.00E-09    | 10         |  |

| 1505.00E-09    | 2          |  |

| 3000.00E-09    | 2          |  |

|                |            |  |

|                |            |  |

| [SPIM Stimulus] |           |

|-----------------|-----------|

| OB_Stimulus     | Weighting |

| OB_Stimulus_1   | 0.20      |

| OB_Stimulus_2   | 0.10      |

| OB_Stimulus_3   | 0.05      |

| OB_Stimulus_4   | 0.05      |

| OB_Stimulus_5   | 0.20      |

| OB_Stimulus_6   | 0.05      |

| OB_Stimulus_7   | 0.05      |

| OB_Stimulus_8   | 0.30      |

| [End SPIM Stimu | ulus]     |

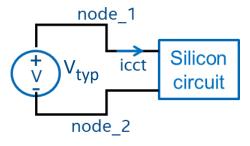

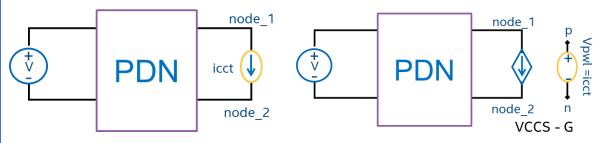

- icct profile under typical voltage directly at circuit node is shown in Fig.1.

- icct might specify time delay or repeat time, with default values of 0.

- In Power Integrity transient simulation with an actual power delivery network (PDN), the icct profile shall be connected as shown by Fig.3 through G element with the 2<sup>nd</sup> Polynomial function for accuracy, other than the 1<sup>st</sup> order connection as shown in Fig. 2 for efficient analysis.

- \* For example,

- \*.SUBCKT VCC1\_icct node1 node2 V<sub>tvn</sub>='1.0'

- \*Gpoly node1 node2 POLY(2) node1 node2 p n 0 0 0 0 '1/ $V_{tvp}$

- \*\*\*\*VCCS i12 =  $0+0*V_{12}+0*Vpn+0*V12*V12+'1/V_{typ}'*V_{12}$

Fig. 2 1st order setup

Fig.3 2<sup>nd</sup> order setup

#### **Next Steps**

- Submit IBIS BIRD of "Add Support of Transient Analysis in SPIM"

- Call for EDA vendors to support Transient Analysis in SPIM

- Call for chip vendors to support Transient Analysis in SPIM

- Call for platform designers to support Transient Analysis in SPIM

#### Legal Disclaimer

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

Intel, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© 2022 Intel Corporation. All rights reserved.

#### Presenter

**Kinger Cai**, *Principal Engineer*Platform Electrical Architect, CCG, Intel Corp.

Kinger.Cai@intel.com

Kinger leads AI PC coherent architecture strategy in mobile platforms and drives strategic platform EDA tools & algorithms evolution in Intel. Kinger obtained Ph. D from Shanghai Jiao Tong University in 2001, and achieved MBA degree from W.P. Carey business school in ASU in 2008. Kinger has focused on signal & power integrity domains for 20+ years. Kinger holds 14 granted patents, and published 30+ papers.

## THANK YOU!

Kinger.cai@intel.com