#### Verification of IBIS models

Hans Klos

Hans.Klos@Sintecs.nl

Sintecs BV

Lansinkesweg 4

7553 AE Hengelo

The Netherlands

www.sintecs.nl

DATE 2004 - IBIS summit presentation

#### Where to get IBIS models

- Download from internet

- ■Not always latest version on internet

- Contact component vendor(s)

- Create models from spice data

- Create models by measurement

www.sintecs.nl

DATE 2004 - IBIS summit presentation

#### How to verify IBIS models

- IBIS golden parser

- Visual verification

- Test IBIS model in simulator

- Compare IBIS model with measurement data

www.sintecs.nl

DATE 2004 - IBIS summit presentation

### IBIS Golden parser

#### **■ IBISCHK**

- Is a program that parses the model file to verify that the file conforms to the IBIS specification. It is free, publically available executable code developed by contractors for the IBIS Open Forum.

- The official ibischk4 checks Version 1.1, 2.1, 3.2 and 4.0 level IBIS files. (Use -ebd and -pkg flags for .ebd and .pkg files.)

www.sintecs.nl

DATE 2004 - IBIS summit presentation

5

www.sintecs.nl

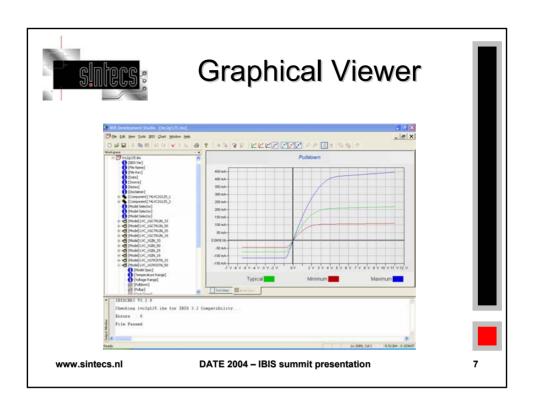

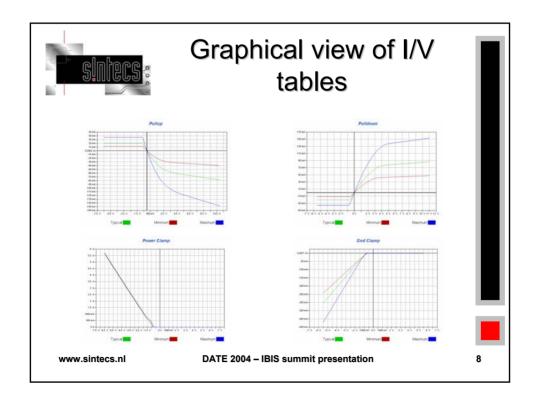

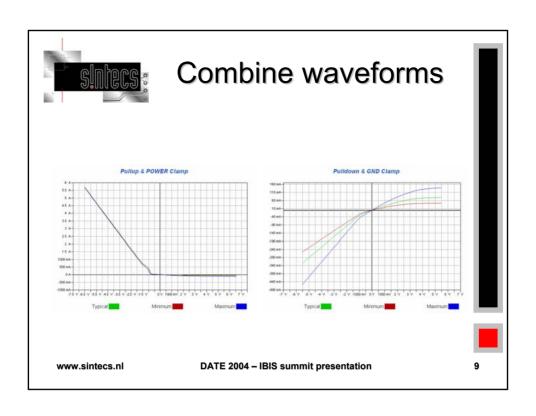

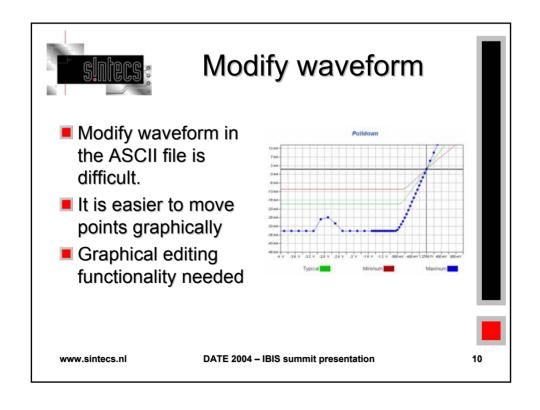

#### Visual verification

- To verify an IBIS model, a graphical view of the waveform(s) makes it easier

- In a graphical viewer of the IBIS models, the potential problems can be found easier.

- Free tools are available for visual verification of an IBIS model.

- IBIS Development Studio

- Visual IBIS editor

. .

DATE 2004 - IBIS summit presentation

#### Test IBIS model in simulator

- After graphical verification, the IBIS model must be tested in the simulator where you are going to use the IBIS model.

- Run the model with the standard test loads.

- Comparing the results against a transistor-level reference simulation using the same loads.

www.sintecs.nl

DATE 2004 - IBIS summit presentation

## Compare IBIS model with measurement data

- The last step in the modeling process is to correlate the simulation results with actual silicon measurements.

- Correlation involves measuring the I-V curves and rise/fall times of an actual IC and verifying that they fall within the maximum and minimum values used in the IBIS model.

(In addition, for ICs in a motherboard or other test setup driving a known load, compare the oscilloscope waveforms with simulation waveforms using the same load.)

www.sintecs.nl

DATE 2004 - IBIS summit presentation

### Adding additional info

- A IBIS model is the best place to define constraints needed for the SI simulator :

- S\_overshoot\_high

- S\_overshoot\_low

- D\_overshoot\_high

- D\_overshoot\_low

- D\_overshoot\_time

- Vmeas

Static overshoot high voltage

Static overshoot low voltage

Dynamic overshoot high voltage

Dynamic overshoot low voltage

Dynamic overshoot time

Measurement voltage for timing

www.sintecs.nl

DATE 2004 - IBIS summit presentation

13

#### Constraints in IBIS

- Most SI simulators uses a constraint spreadsheet for defining constraints.

- Constraints for under-/over-shoot should come from the IBIS model.

- Most IBIS models does not contain this information.

- This information can be found in the datasheet, or contact the component vendor.

www.sintecs.nl

DATE 2004 - IBIS summit presentation

# Roadmap IBIS Development Studio

- Test model in simulator (ICX / ePlanner / Hyperlynx / simulators) within IBISDS

- Enhanced features for model wizard

- XML output of IBIS model

- Other improvements suggested by IBISDS users (<u>ibisds@edality.com</u>)

- For more info, visit us at http://www.edality.com

www.sintecs.nl

DATE 2004 - IBIS summit presentation