# Impact of True Strobe Timing on DDR Channel Simulation with IBIS-AMI Models

Ken Willis, Cadence Kumar Keshavan, Cadence Ambrish Varma, Cadence IBIS Summit – DesignCon 2019 Santa Clara, California February 1, 2019

cādence®

#### Overview

- As channel simulation and IBIS-AMI modeling methods are adapted from serial link to DDR interface analysis, serial link CDR algorithms are often used for analysis

- But actual DDR interfaces use strobe signals as the timing reference for data buses

- What is the impact?

#### Agenda

- Current CDR-based method

- True strobe timing

- Comparison of results

- Summary

#### **Current CDR-Based Method**

#### Centers the eye for each individual signal

- With real strobe, this is done for entire byte lane

- Some controllers have some individual bit de-skewing

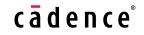

## **Current Channel Simulation Flow**

Standard (Current) channel simulation flow for serial link channels that is also used for parallel bus

- Ideal clock ticks are generated internally by the eye sampler

- Clock ticks can also be generated by AMI models and sent to the eye sampler

© 2019 Cadence Design Systems, Inc. All rights reserved.

5

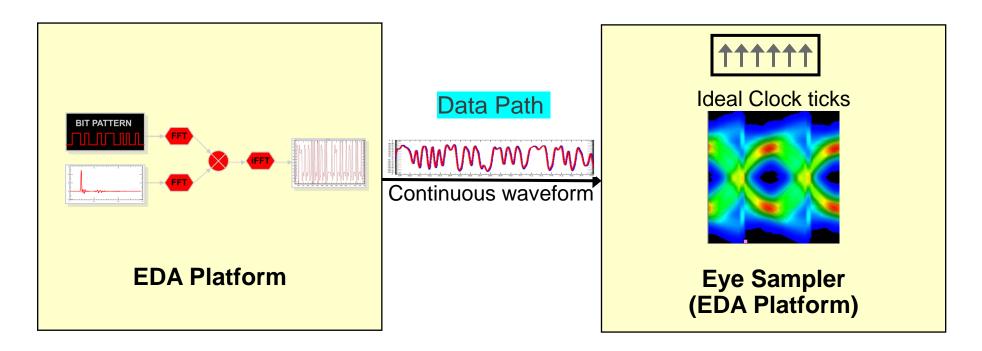

## True Strobe Timing (TST)

- Clock ticks are collected from the strobe channel instead of the data channel

- Strobe channel is only fed with 0101 data

- Clock ticks are collected in the same way as data channel

#### New Channel Simulation Flow for Source Synchronous Channel

7

cādence°

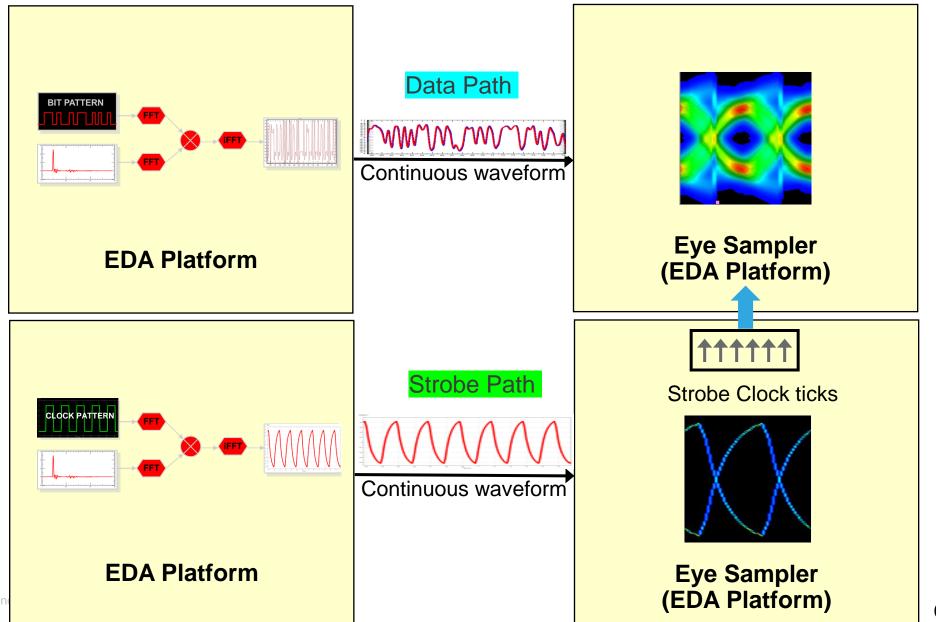

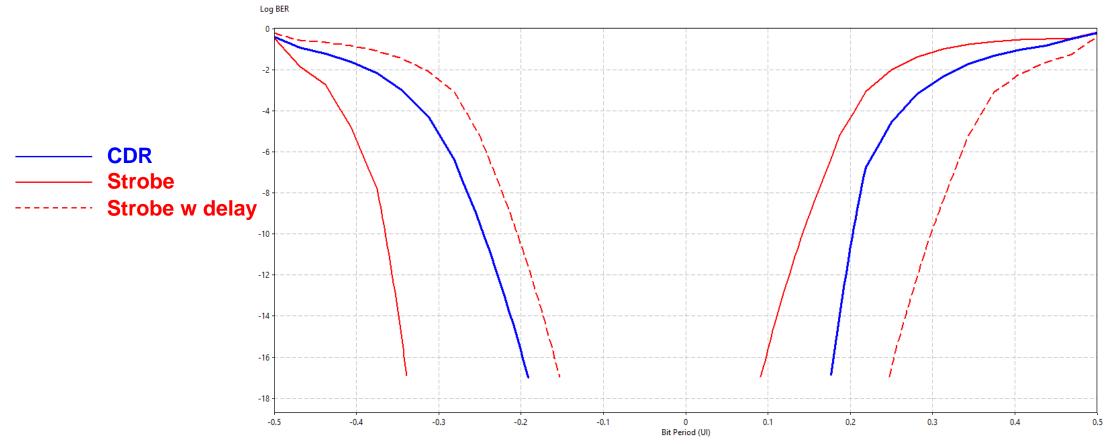

#### Comparison of Results

- CDR vs. TST

- CDR vs. TST with jitter impairments

#### • Test Setup

- 1 data line is used for simulations

- 6 Gbps

- Rx CTLE

- Rx 4 tap DFE

## CDR vs. TST

cādence°

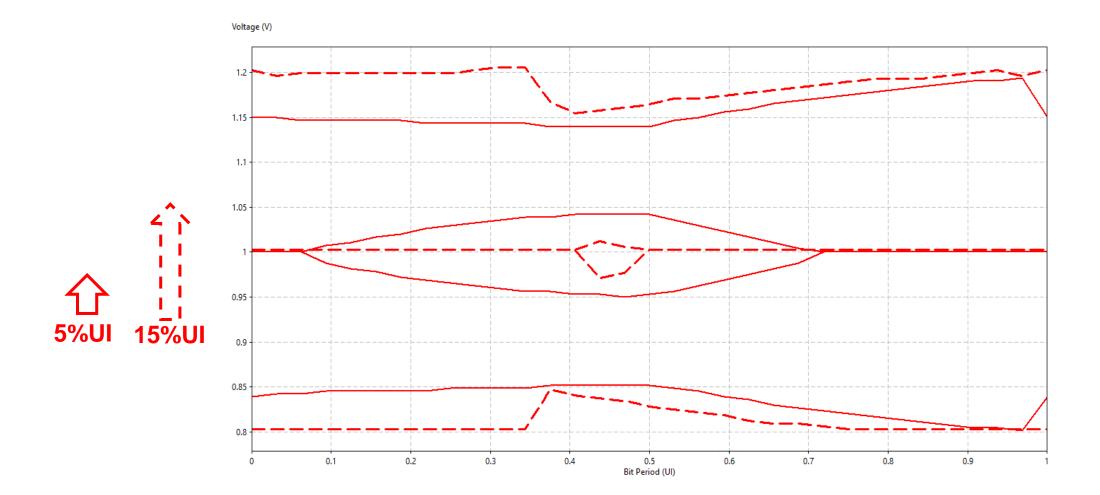

#### Strobe Results with Dj Applied at Tx

#### cādence°

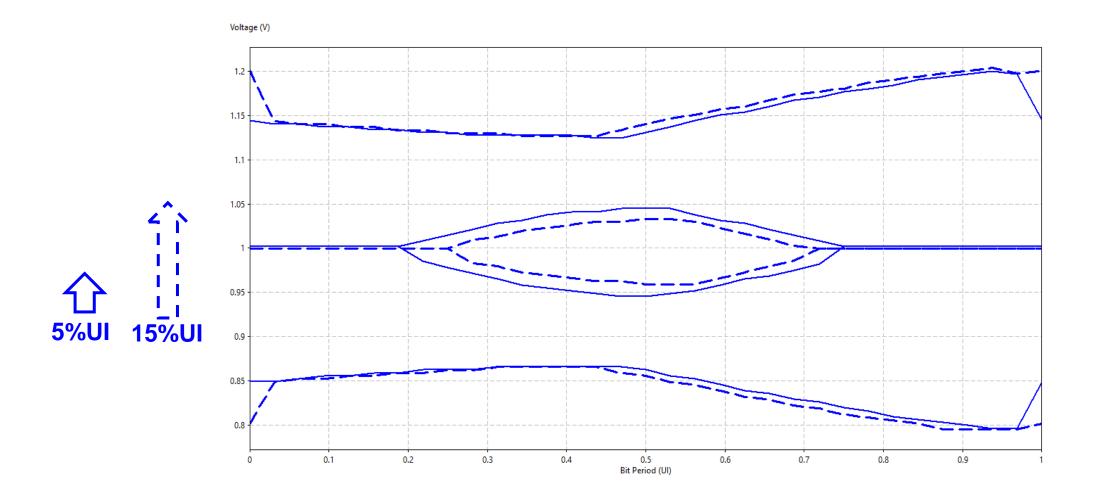

### CDR Results with Dj Applied at Tx

11

#### cādence<sup>®</sup>

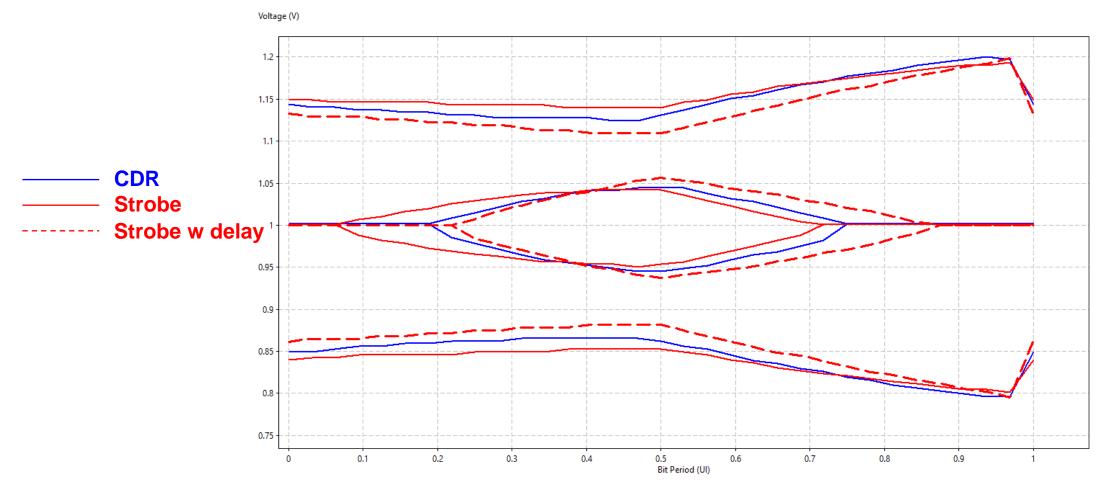

# CDR vs. TST

#### • After delaying by 0.2 UI

CDR vs. TST

#### Summary

- Using default CDR instead of actual strobe to get clock risks missing important impairments/jitter for parallel bus topology

- Analysis results show false optimism using CDR approach as compared to true strobe timing methodology

- Need to model delay accurately

# cādence®

© 2019 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.