# IBIS Based Modeling for System-Level Power Delivery

Zhiping Yang\*, Songping Wu\* Kinger Cai#, Joshua Luo^, Yingxin Sun^

\*Google Inc.; # Intel Corp.; ^ Cadence Design Systems

DesignCon IBIS Summit Santa Clara, California. February 1, 2019

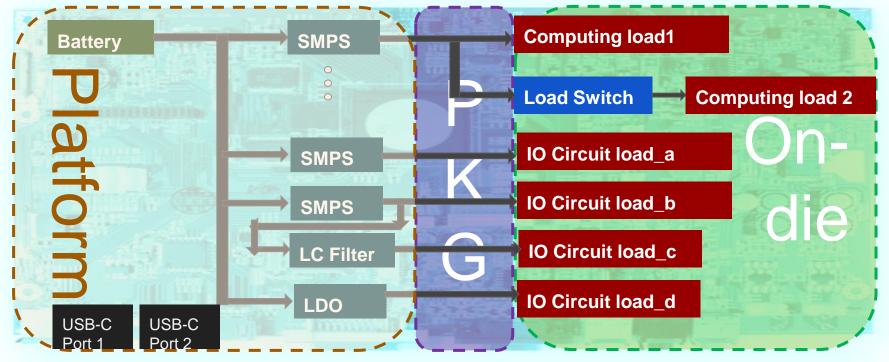

#### System Power Delivery Architect

\*SMPS=switching mode power supply

#### Sys PD Architect:

1, SMPS to computing load 3, LDO to IO circuit load

2, SMPS to IO circuit load

4, SMPS to IO circuit load\_b, and also to IO circuit load\_c through LC filter to  $IO^2$

### System-Level Power Simulation Coverage

Propose to use IBIS format models to do the following simulations:

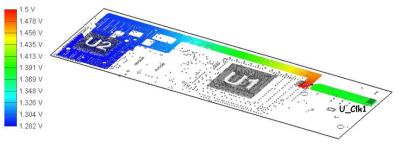

- System level DC simulations, including IR drop, DCR.

- AC simulations, i.e. PDN impedance

- Transient load response, i.e. transient power noise

- System power consumption and efficiency

- Power/thermal co-simulation

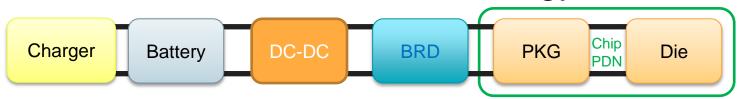

#### DC Simulation Common Methodology

- Charger & Battery not modeled. Model from DC-DC to Die IR drop.

- DC-DC model as current source

- BRD & all the passive components on board as a resistance network

- PKG resistance network

- Die as current sink/load

#### Shortcomings and Proposals

- Shortcomings:

- Have to readout and key in current load and voltage source values for all the rails manually. Easy to make a fault.

- No VRM loadline information included.

- Proposals:

- Device chip vendor to provide IBIS format power model that includes current information.

- VRM vendor to provide IBIS format model including voltage source information.

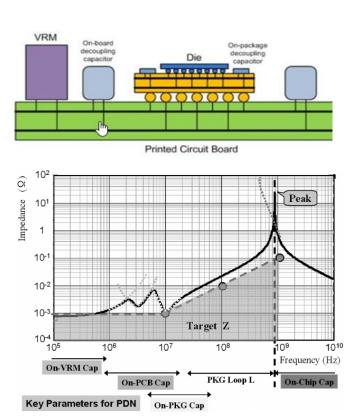

### AC Simulation Common Methodology

Die Models:

- CPM model (passive)

- Simple Rdie, Cdie netlist

- PKG PDN (level –a)

- S parameter from bump to pin/BGA

- pin awareness, for automatically merging with BRD

- Impedance target at Observation port in PKG

- On-die PDN (level –b)

- S parameter of power grid

- Impedance target at Observation port in PKG

**BRD Models:**

- Passive extraction using EM EDA tools VRM Models:

- 1st order 2-element model

- 2nd order 4-element model

#### Shortcomings and Proposals

- Shortcomings:

- Hard to get die model either in CPM or Rdie/Cdie from chip vendor

- Hard to get package model from vendors

- Proposals:

- Device chip vendor to provide IBIS format power model that can (optionally) provide die model as well as package model.

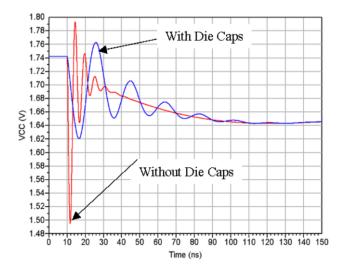

#### **Transient Simulation Common Methodology**

#### Die Models:

- CPM model (active)

- Worst case icct profile BRD Models:

- PDN including power routings, caps extraction using EM EDA tools

VRM Models:

- Simplis model

- Behavioral HSPICE model

- Transistor level model

Printed Circuit Board

#### Similarly . . .

- We propose to include current consumption and CMOS circuits netlist in the IBIS format model to simulate power consumption of each device.

- We propose to include detailed chip model in IBIS format to model switching and conduction loss of a device so as to get power/thermal cosimulation.

#### Approved IBIS BIRDs related to Power - 1

| BIRD # | Title                                                            | Status   | Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Value for this proposal                                     |

|--------|------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 28.3   | Enhancement To The<br>Package Model (.pak file)<br>Specification | Accepted | "The current package model specification describes each pin on<br>a package using lumped L/R/C parameters. Coupling between<br>pins also assumes lumped electrical parameters. However,<br>these description are inadequate when the electrical length of<br>the package elements are greater than ~1/6 of the I/O buffers'<br>rise time. This bird enhances the package description by<br>allowing package elements to be described in terms of length<br>and L, R and C per unit length; i.e. a transmission line<br>representation." | Can be used for<br>package model format.                    |

| 38     | Maximum Voltage                                                  | Rejected | "IBIS can be extended to allow a component supplier specify<br>maximum positive and negative voltages (or currents) that can<br>safely be applied to an I/O buffer".                                                                                                                                                                                                                                                                                                                                                                    | Can be extended to all power device current profile format. |

#### Approved IBIS BIRDs related to Power - 2

| BIRD # | Title                                                   | Status   | Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Value for this proposal                               |

|--------|---------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 42.3   | Modeling Current<br>Waveforms                           | Rejected | "Current into the power and ground rails are needed to give a more<br>accurate analysis for ground and power bounce analysis associated<br>with simultaneous switching".                                                                                                                                                                                                                                                                                                                      | A similar format can be used to give current profile. |

| 95.6   | Power Integrity<br>Analysis using IBIS                  | Accepted | "Power Integrity Analysis which includes Current switching profile of<br>the Core as well as Simultaneous Switching Noise (SSN) of states of a<br>buffer is to be analyzed through IBIS."                                                                                                                                                                                                                                                                                                     | Can be extended to core power rails too.              |

| 125.1  | Make IBIS-ISS<br>Available for IBIS<br>Package Modeling | Rejected | "Package modeling in IBIS has numerous serious limitations which<br>make it practically useless for simulations involving modern devices<br>and signaling technologies. However, the IBIS-ISS specification<br>defines useful and much-needed features through a standardized<br>SPICE language. These features would enhance the current package<br>modeling capabilities of IBIS significantly with minimal changes in the<br>specification and little implementation effort in EDA tools." | Can use IBIS-ISS<br>format for package<br>modeling    |

#### Approved IBIS BIRDs related to Power - 3

| BIRD # | Title                                                     | Status   | Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Value for this proposal                                                           |

|--------|-----------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 176    | Power Pin Package<br>Modeling                             | Accepted | "This BIRD enhances IBIS with interconnect modeling features to support<br>broadband, coupled package, and on-die interconnect using IBIS-ISS and<br>Touchstone data. The BIRD also adds a keyword for buffer rail mapping, to<br>link to new terminal definitions defined for buffers".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Similar interconnect<br>model idea can be<br>applied to system-level<br>modeling. |

| 189.7  | Interconnect Modeling<br>Using IBIS-ISS and<br>Touchstone | Accepted | "Under the [Package] keyword, the IBIS specification defines a set of rules on the hierarchy of the various package modeling options. It is clearly stated that when present, the package information under the [Pin] keyword will override the package information in the [Package] keyword, and if present, the information in the [Package Model] and [Define Package Model] keywords will override the information in the [Pin] and [Package] keywords. The Usage Rules of the [Pin Numbers] keyword in the [Define Package Model] keyword section do not prohibit a "partial package model", i.e., a model which only describes a subset of a Component's pins. The problem is that there are no rules under the [Pin Numbers] keyword to describe what the EDA tool should do when the keyword doesn't contain the name of a pin that is listed in the component's [Pin] keyword. In the absence of rules, model makers and EDA tool vendors may make different assumptions which may lead to incorrect simulation results. For example, when a pin name is missing under the [Pin] or [Package] keyword, while others might implement an open or short instead.". | Same pin rule can be<br>used as well.                                             |

## The END