## Concerns when applying Channel Simulation to DDR4 Interface

#### Masaki Kirinaka

mkirinaka@jp.fujitsu.com Akiko Tsukada tsukada.akiko@jp.fujitsu.com FUJITSU INTERCONNECT TECHNOLOGIES LIMITED

Asian IBIS Summit Tokyo, JAPAN November 12, 2018

## Agenda

- Background

- About Channel Simulation

- Investigate LTI system of DDR4 Signal

- Summary

## Background

## Background

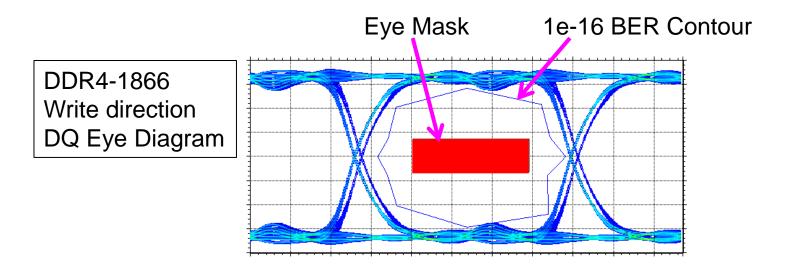

- DDR4 SDRAM JEDEC STANDARD: At BER=1e-16, the Eye Margin is necessary.

- Simulation of a great many bits is necessary to get a highly precise 1e-16 BER Contour.

- □ The conventional SPICE simulation takes time.

- □ Therefore high-speed Channel simulation using IBIS-AMI is necessary.

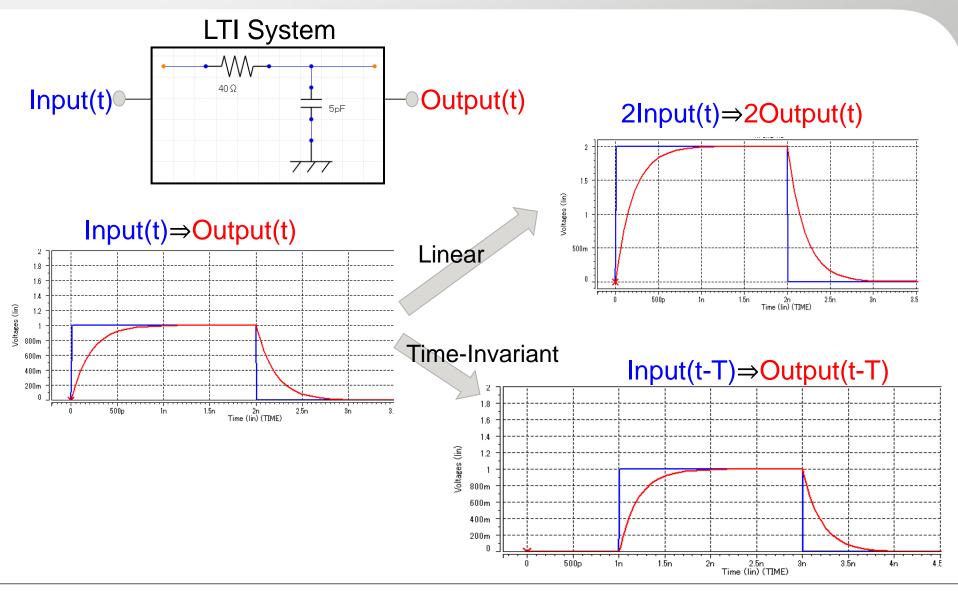

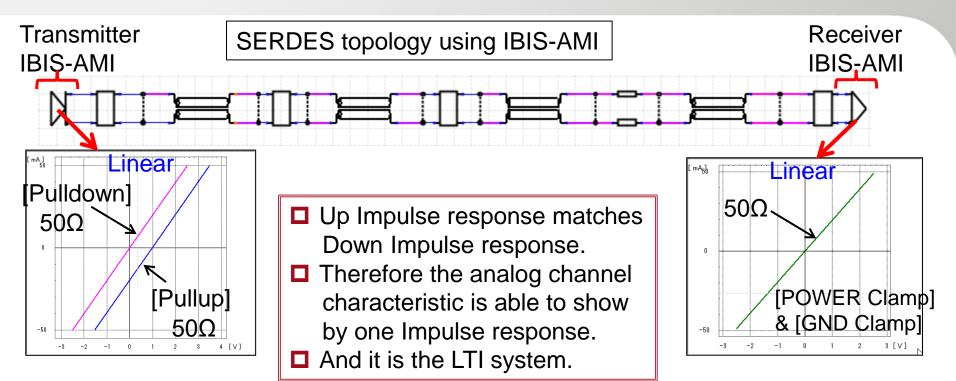

- In Channel simulation, the analog channel (include Driver, Receiver, Transmission line) must be LTI (Linear time-invariant) system.

- □ Therefore investigated whether DDR4 DQ Signal was LTI system this time.

## **About Channel Simulation**

#### **Channel Simulation Method** FUÏTSU Ideal Unit Step Signal Analog Channel Step Response [Linear Time-Invariant (LTI) system] u(t) s(t) O **Time Derivative** Impulse Response Convolution Eye Diagram h(t) ds(t)h(t)**TX Input Bit Stream**

## Linear Time-Invariant (LTI) Fujitsu

## Linear Time-Invariant (LTI)

FUÏTSU

## Is the DQ Signal of DDR4 LTI? FUJITSU

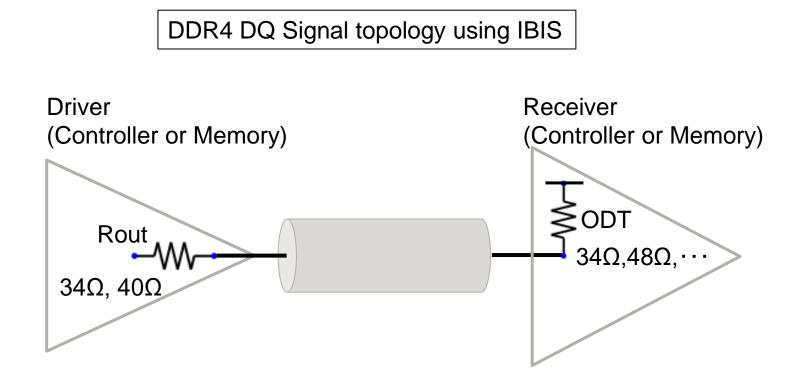

□ The resistance value of Rout and ODT is shown in the IBIS model name.

→ Is it good to treat DDR4 DQ Signal as LTI system like SERDES?

□ Investigated whether DDR4 DQ Signal was LTI system.

#### Investigate LTI system of DDR4 Signal

#### **Investigated DDR4 Signals**

| Case | Mbps | Investigated DDR4 | Signal | Result   |

|------|------|-------------------|--------|----------|

| 1    | 1866 | DDR4 Signal No.1  | Write  | Attached |

| 2    | 1000 |                   | Read   | -        |

| 3    | 2133 | DDR4 Signal No.2  | Write  | Attached |

| 4    | 2133 |                   | Read   | -        |

| 5    | 2400 | DDR4 Signal No.3  | Write  | -        |

| 6    | 2400 |                   | Read   | -        |

| 7    | 0400 | DDR4 Signal No.4  | Write  | -        |

| 8    | 2133 |                   | Read   | Attached |

- Used Max model of IBIS in the Spice simulation and the Channel simulation.

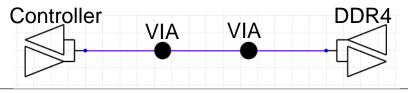

- Example of the investigated topology

#### Investigation method

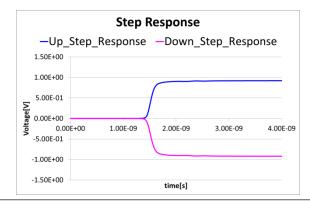

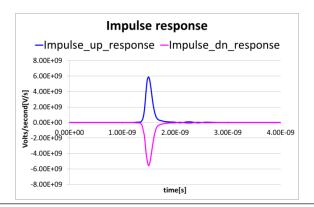

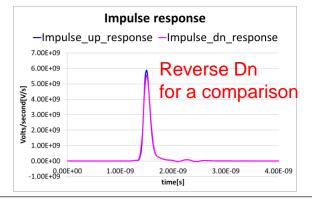

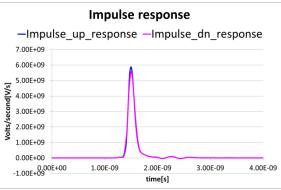

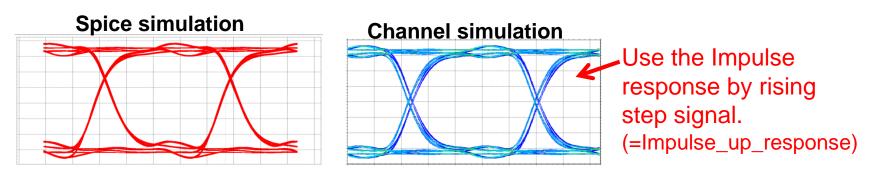

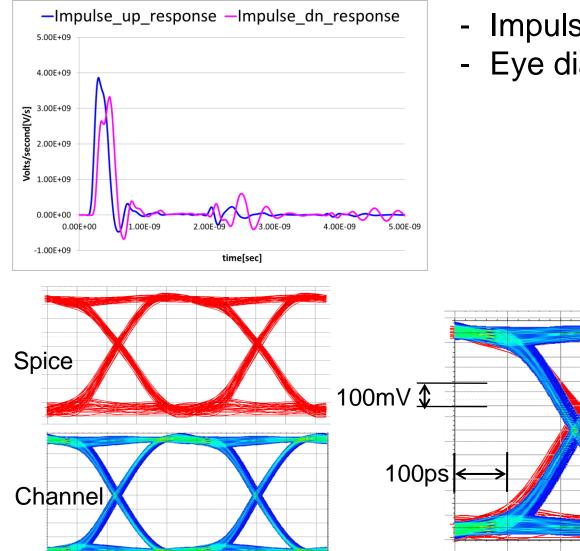

Confirm the Impulse responses of rising step signal and falling step signal.

$\rightarrow$  Are two impulse responses same?

Comparison between the Spice simulation and

the Channel simulation.

$\rightarrow$  Is the Channel simulation same as the Spice simulation?

### [Case1] DDR4 Signal No.1 Write

FUJITSU

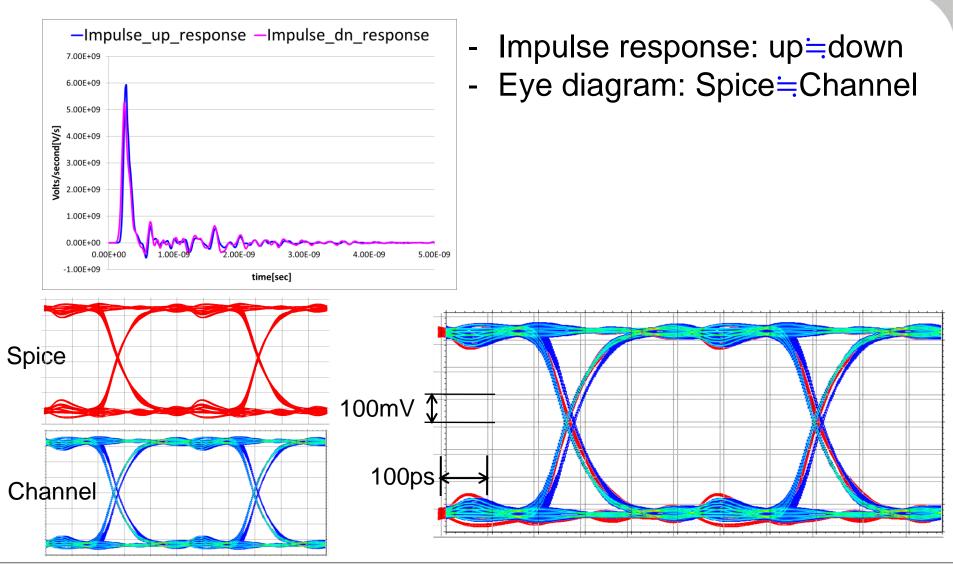

#### [Case3] DDR4 Signal No.2 Write

#### [Case3] DDR4 Signal No.2 Write

Why is it "Eye diagram: Spice Channel"? Checked IBIS.

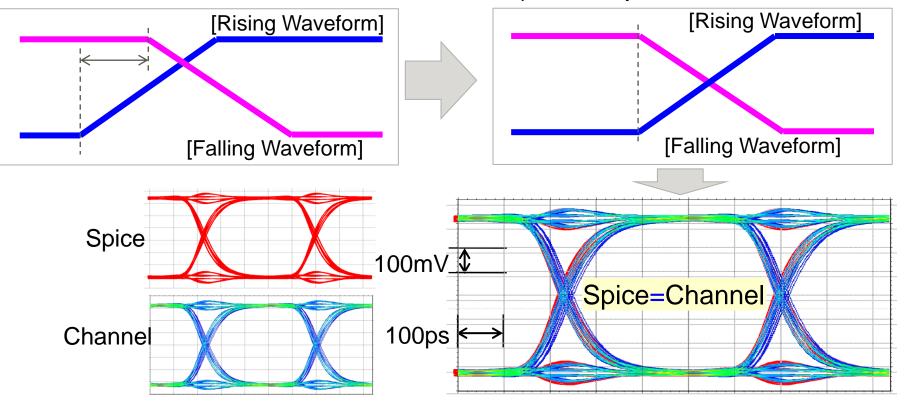

Rising and Falling Waveform of Controller (Driver) The start of the change are greatly different.

Made the start of the change the same experimentally.

The cause is difference between rise timing and fall timing of the driver.

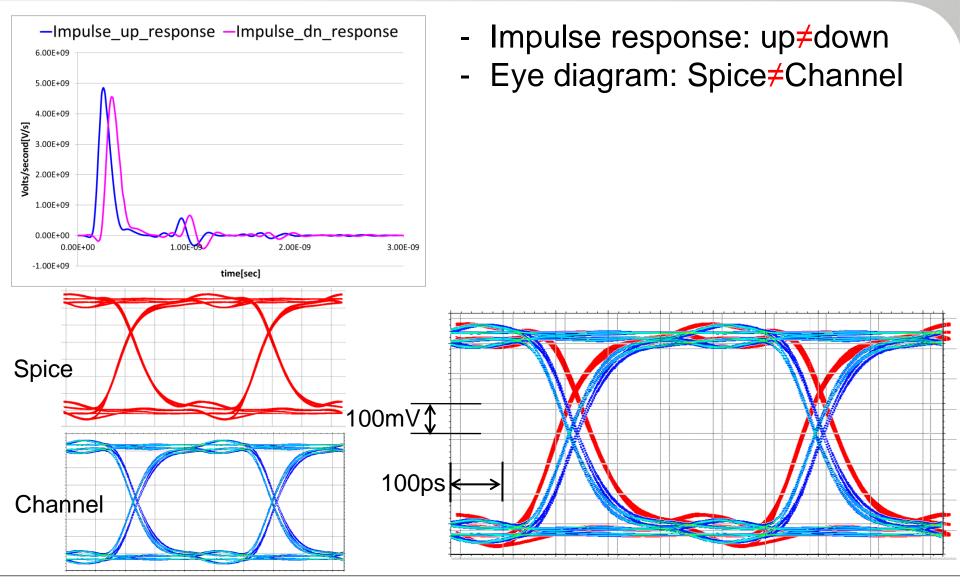

#### [Case8] DDR4 Signal No.4 Read

- Impulse response: up≠down

- Eye diagram: Spice Channel

#### [Case8] DDR4 Signal No.4 Read

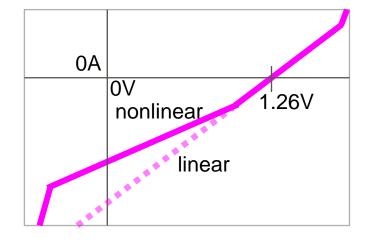

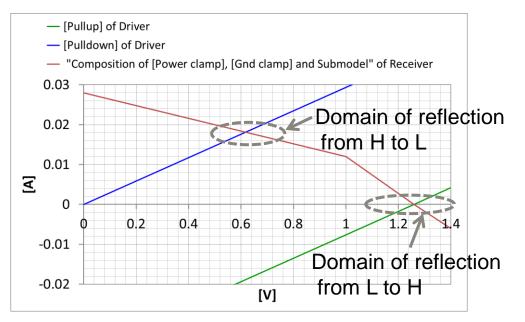

Why is it "Eye diagram: Spice Channel"? Checked IBIS.

Composition of [Power clamp], [GND clamp] and [Submodel] of the Controller (Receiver) . It is nonlinear.

Reflection from L to H (Up)  $\neq$  Reflection from H to L (Down). Therefore the Impulse responses are different in "Up" and "Down".

Used the Up Impulse response in the Channel simulation.

The cause is that the ODT of Receiver is Nonlinear. (The value of ODT is different in "Up" and "Down".)

## **Investigation Results**

| Case | Investigated DDR4 Signal |       | Impulse<br>up=down? | Eye diagram<br>Spice=Channel? |

|------|--------------------------|-------|---------------------|-------------------------------|

| 1    | DDD4 Signal No 1         | Write | close               | close                         |

| 2    | DDR4 Signal No.1         | Read  | same                | close                         |

| 3    | DDR4 Signal No.2         | Write | different           | different                     |

| 4    | DDR4 Signal No.2         | Read  | close               | close                         |

| 5    | DDD4 Signal No 2         | Write | close               | same                          |

| 6    | DDR4 Signal No.3         | Read  | close               | same                          |

| 7    | DDD4 Signal No.4         | Write | close               | close                         |

| 8    | DDR4 Signal No.4         | Read  | different           | different                     |

## Summary

## Summary

- Investigated whether DDR4 DQ Signal was LTI system.

- Most of the cases investigated were LTI system.

- However, there were two cases that were not LTI (NLTV: Non Linear Time Variant). The reasons why they are not LTI system are as follows.

- 1. Driver IBIS: There is a difference at the start time of the Rise and the Fall of Waveform.

- 2. Receiver IBIS: ODT (Composition of [Power clamp], [GND clamp] and [Submodel]) is Nonlinear.

- From the above, it is necessary to consider that there are not only LTI but also nonlinear systems (NLTV) in the DDR4 signal.

- □ Is IO of DDR5 LTI?

References

- "IBIS (I/O Buffer Information Specification) Version 6.1", IBIS Open Forum 2015 <u>http://www.ibis.org/ver6.1/</u> for IBIS 6.1

- JEDEC STANDARD DDR4 SDRAM JESD79-4A Revision of JESD79-4, September 2012 for DDR4 Standard

# FUJTSU

shaping tomorrow with you