#### WELCOME FROM MIKE LABONTE, IBIS OPEN FORUM

Ladies and Gentlemen,

As chair of the IBIS Open Forum it is my pleasure to welcome you to the 2018 Asian IBIS Summit in Taipei and to thank you for your presentations and participation. We are grateful to our sponsors Cadence Design Systems, KairosTech Innovation (SPISim), and Synopsys for making this event possible.

Since 1993 IBIS has provided the digital electronics industry with specifications to make signal, timing, and power integrity analyses much easier and faster. With the introduction of IBIS-AMI in 2008, the IBIS community generated new energy for high speed electronic design. IBIS is now known by engineers worldwide and is a required technology for many applications.

Support for IBIS in Asia has been strong, and the IBIS Open Forum looks forward to continued innovation and contributions from technology companies in Asia. Thank you!

Mike LaBonte

SiSoft

Chair, IBIS Open Forum

Muhal R Lint

#### WELCOME FROM MIKE LABONTE, IBIS OPEN FORUM

女士們先生們,

作為 IBIS 開放論壇的主席,我很高興地歡迎您參加 2018 年在台北舉辦的亞洲 IBIS 峰會,感謝您的介紹和參與。我們非常感謝我們的讚助商 Cadence Design Systems, KairosTech Innovation(SPISim)和 Synopsys,以使這一事件成為可能。

自1993年以來,IBIS為數字電子行業提供了使信號,時序和電源完整性分析更容易和更快速的規範。隨著IBIS-AMI在2008年的推出,IBIS社區為高速電子設計創造了新的能量。IBIS現在已被世界各地的工程師所了解,是許多應用所需的技術。

IBIS 在亞洲的支持一直很強, IBIS 開放論壇期待著亞洲技術公司的不斷創新和貢獻。

谢谢!

Mike LaBonte (迈克 拉邦地)

Markal R La Sont

SiSoft 公司

主席, IBIS 开放论坛

#### AGENDA AND ORDER OF THE PRESENTATIONS

# (The actual agenda might be modified)

|       | IBIS SUMMIT MEETING AGENDA                                                                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9:00  | SIGN IN - Vendor Tables Open at 8:30                                                                                                                             |

| 9:30  | <pre>WELCOME - Mike LaBonte (Chair, IBIS Open Forum)     (SiSoft, USA)</pre>                                                                                     |

| 9:45  | IBIS Update                                                                                                                                                      |

| 10:05 | A Practical Methodology for SerDes Design                                                                                                                        |

| 10:35 | BREAK (Refreshments and Vendor Tables)                                                                                                                           |

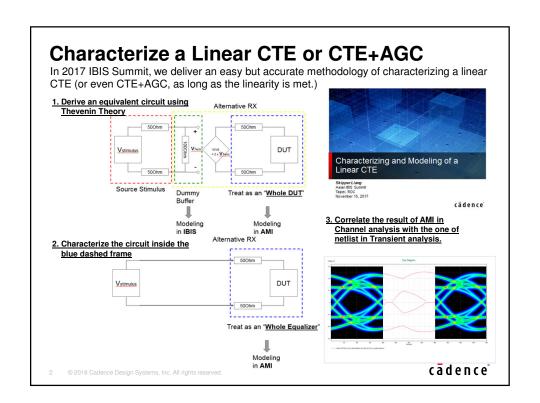

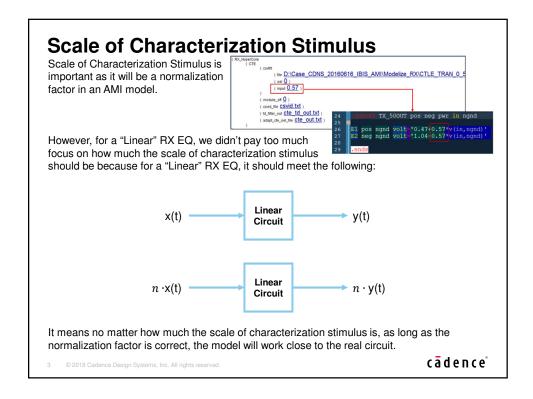

| 10:55 | Characterizing and Modeling of a Clamped Non-Linear CTE/AGC 21<br>Skipper Liang (Cadence Design Systems, ROC)                                                    |

| 11:50 | FREE BUFFET LUNCH (Hosted by Sponsors) - Vendor Tables                                                                                                           |

| 13:20 | Model Correlation for IBIS-AMI                                                                                                                                   |

| 14:10 | BREAK (Refreshments and Vendor Tables)                                                                                                                           |

| 14:30 | Study of DDR Asymmetric Rt/Ft in Existing IBIS-AMI Flow 52 Wei-hsing Huang#, Wei-kai Shih## (SPISim, #USA, ##Japan) [Presented by Wei-hsing Huang (SPISim, USA)] |

| 15:00 | DISCUSSION                                                                                                                                                       |

| 15:20 | CONCLUDING ITEMS                                                                                                                                                 |

| 15:30 | END OF IBIS SUMMIT MEETING                                                                                                                                       |

|       |                                                                                                                                                                  |

# **IBIS Update**

http://www.ibis.org/

Mike LaBonte SiSoft Chair, IBIS Open Forum

2018 Asian IBIS Summit Taipei, ROC November 16, 2018

IBIS Update

25 IBIS Members alialia **NNSYS** ⊕BROADCOM cādence cisco CST **Ericsson IBM** infineon (intel) MIXIM Mentor Micron SYNOPSYS XILINX" ZUKEN **Number of Members by Year** IBIS Update

#### Organization

# IBIS Officers 2018-2019

Chair: Mike LaBonte, SiSoft

Vice-Chair: Lance Wang, IO Methodology Inc.

Secretary: Randy Wolff, Micron Technology

Treasurer: Bob Ross, Teraspeed Labs

Librarian: Anders Ekholm, Ericsson

Postmaster: Curtis Clark, ANSYS

Webmaster: Mike LaBonte, SiSoft

IBIS Update

3

#### Organization

# **IBIS Meetings**

- Weekly teleconferences

- Quality Task Group (Tuesdays)

- Advanced Technology Modeling Task Group (Tuesdays)

- Interconnect Task Group (Wednesdays)

- Editorial Task Group (some Fridays)

- IBIS Open Forum teleconference every 3 weeks

- 480 meetings so far

- IBIS Summit meetings: DesignCon, IEEE SPI, EDICON USA, EPEPS, Shanghai, Taipei, Tokyo

IBIS Update

4

Organization

# **SAE ITC**

- SAE Industry Technologies Consortia is the parent organization of the IBIS Open Forum

- IBIS is assisted by SAE employees José Godoy, Phyllis Gross, Dorothy Lloyd

- SAE ITC provides financial, legal, and other services

- http://www.sae-itc.org/

IBIS Update

5

#### Organization

# Task Groups

- Interconnect Task Group

- Chair: Michael Mirmak

- <a href="http://ibis.org/interconn-wip/">http://ibis.org/interconn-wip/</a>

- Develop on-die/package/module/connector interconnect modeling BIRDs

- Advanced Technology Modeling Task Group

- Chair: Arpad Muranyi

- http://ibis.org/atm\_wip/

- Develop most other technical BIRDs

- Quality Task Group

- Chair: Mike LaBonte

- http://ibis.org/quality\_wip/

- Oversee IBISCHK parser testing and development

- Editorial Task Group

- Chair: Michael Mirmak

- http://ibis.org/editorial\_wip/

- Produce IBIS Specification documents

BIRD = Buffer Issue Resolution Document

IBIS Update

6

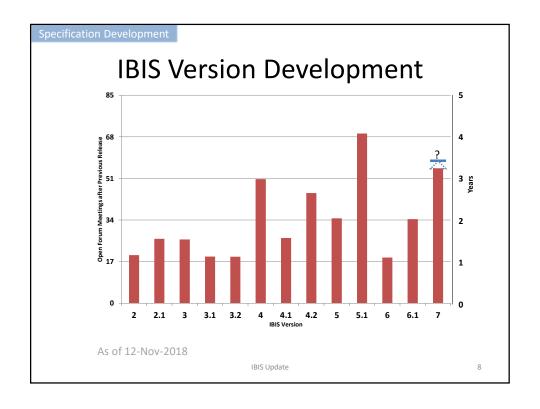

#### **IBIS Milestones** I/O Buffer Information Specification Other Work 1993-1994 IBIS 1.0-2.1: 1995: ANSI/EIA-656 - Behavioral buffer model (fast simulation) - IBIS 2.1 Component pin map (easy EDA import) 1999: ANSI/EIA-656-A 1997-1999 IBIS 3.0-3.2: - Package models - IBIS 3.2 Electrical Board Description (EBD) 2001: IEC 62014-1 - Dynamic buffers - IBIS 3.2 2002-2006 IBIS 4.0-4.2: 2003: ICM 1.0 - Receiver models - AMS languages Interconnect Model Specification 2007-2012 IBIS 5.0-5.1: 2006: ANSI/EIA-656-B - IBIS-AMI SerDes models - IBIS 4.2 Power aware 2013-2015 IBIS 6.0-6.1: 2009: **Touchstone 2.0**\* PAM4 multi-level signaling 2011: IBIS-ISS 1.0 - Power delivery package models Interconnect SPICE Subcircuit 2019? IBIS 7.0 Current specification development

#### Specification Development

# Possible IBIS 7.0 Timeline

| Meeting Date | Milestone                                                |

|--------------|----------------------------------------------------------|

| 4/21/2017    | Vote to establish 7.0 as the next IBIS version passes.   |

|              | BIRD review and acceptance (30 meetings)                 |

| 7/20/2018    | 7.0 BIRD set accepted.                                   |

| •••          | Editorial task group drafts IBIS 7.0                     |

| 12/21/2018   | Editorial announces IBIS 7.0 ready. Review period begins |

| 1/11/2019    |                                                          |

| 2/8/2019     | Vote to ratify 7.0 scheduled for next meeting            |

| 3/1/2019     | IBIS 7.0 ratified                                        |

#### Specification Developmen

# BIRDs Included in IBIS 7.0

| BIRD  | Title                                                         |

|-------|---------------------------------------------------------------|

| 147.6 | Back-channel Support                                          |

| 165   | Parameter Passing Improvements for [External Circuit]s        |

| 179   | New IBIS-AMI Reserved Parameter Special_Param_Names           |

| 180   | Require Unique Pin Names in [Pin]                             |

| 182   | POWER and GND [Pin] signal_name as [Pin Mapping] bus_label    |

| 183   | [Model Data] Matrix Subparameter Terminology Correction       |

| 184.2 | Model_name and Signal_name Restriction for POWER and GND Pins |

| 185.2 | Section 3 Reserved Word Guideline Update                      |

| 186.4 | File Naming Rules                                             |

| 187.3 | Format and Usage Out Clarifications                           |

| 188.1 | Expanded Rx Noise Support for AMI                             |

| 189.6 | Interconnect Modeling Using IBIS-ISS and Touchstone           |

| 191.2 | Clarifying Locations for Si_location and Timing_location      |

| 192.1 | Clarification of List Default Rules                           |

| 193   | Figure 29 corrections                                         |

| 194   | Revised AMI Ts4file Analog Buffer Models                      |

| 196.1 | Prohibit Periods at the End of File Names                     |

IBIS Update

10

#### Specification Development

# BIRDs Excluded from IBIS 7.0

| BIRD  | Title                                                  |

|-------|--------------------------------------------------------|

| 166.2 | Resolving problems with Redriver Init Flow             |

| 181.1 | I-V Table Clarifications                               |

| 190   | Clarification for Redriver Flow                        |

| 195.1 | Enabling [Rgnd] and [Rpower] Keywords for Input Models |

Green = Approved BIRD

IBIS Update

11

# [Thank You]

IBIS Open Forum:

Web: <a href="http://www.ibis.org">http://www.ibis.org</a>

Email: <a href="mailto:ibis-info@freelists.org">ibis-info@freelists.org</a>

We welcome participation by all IBIS model makers, EDA tool vendors, IBIS model users, and interested parties.

IBIS Update

12

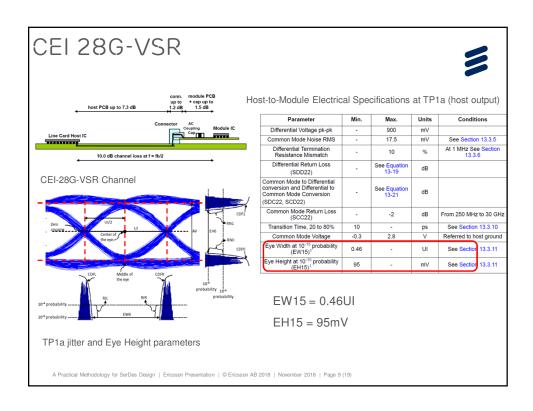

# A PRACTICAL METHODOLOGY FOR SERDES DESIGN

Asian IBIS Summit, Taipei, Taiwan, November 16, 2018 Authors:

Amy Zhang, Guohua Wang, David Zhang, Zilwan Mahmod, Anders Ekholm

# **AGENDA**

- > Challenges in Traditional Simulation

- > The DOE/RSM Solution

- > CEI 28G-VSR IF Design with DOE

- Question and Suggestion for IBIS-AMI

A Practical Methodology for SerDes Design | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 2 (19)

#### SERDES & CHANNEL SerDes Receiver > Transceiver Equalization **Transmitter** --)[----------Channel BGA Via BGA Via Via impedance Trans Line Trans Line Trace impedance Conn PTH Conn PTH > Trace loss Connector Connector Connector characteristics Conn PTH Stripline Conn PTH A Practical Methodology for SerDes Design | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 3 (19)

# MISSION IMPOSSIBLE

- > Equalization settings

- FFE

- > Precursor 10 taps

- > Postcursor 10 taps

- CTLE

- > Off; Fixed; Adapt

- DFE

- > Off; Fixed; Adapt

- Via impedance

- 3 corners (TC/WC/BC)

- > Trace impedance

- 3 corners (TC/WC/BC)

- Connector characteristics

- 3 corners (TC/WC/BC)

- Trace loss

- 3 corners (TC/WC/BC)

Assuming 10min for each simulation case:

Running bits: 1\*10<sup>6</sup>

· Sampling per bit: 64

· Block size: 1024

Total time consumption of simulation:

10\*10\*10\*3^6

= 729000 minutes

= 506.25days

A Practical Methodology for SerDes Design | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 4 (19)

# THE DOE/RSM SOLUTION

- The Ideal:

- What if we had an equation where you put in the system conditions and out came system performance?

- Approximating the Ideal:

- Statistically sample the parameter space

- Design of Experiment (DOE)

- Use your knowledge of the system under analysis to apply an appropriate model to the data

- > Response Surface Model (RSM)

- Validate model

- Utilize model to optimize and explore

A Practical Methodology for SerDes Design | Ericsson Presentation | @ Ericsson AB 2018 | November 2018 | Page 7 (19)

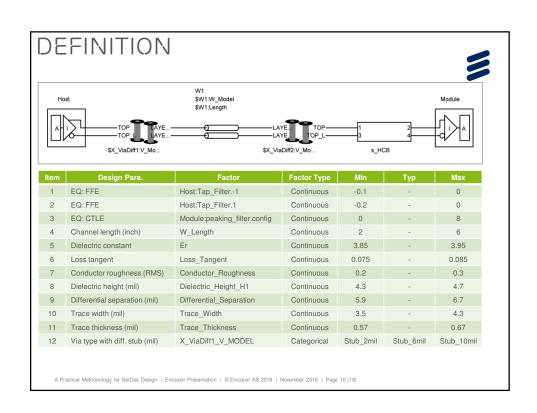

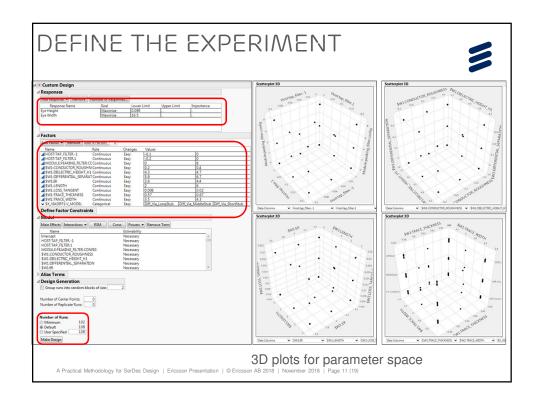

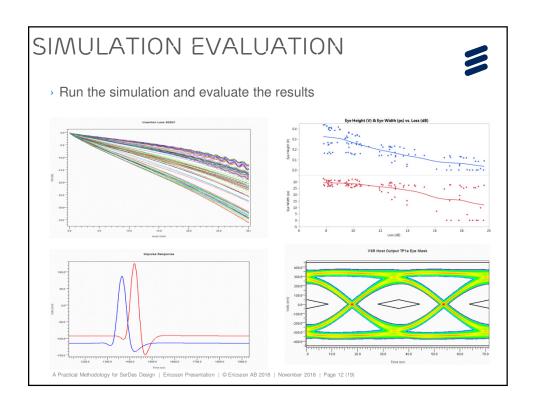

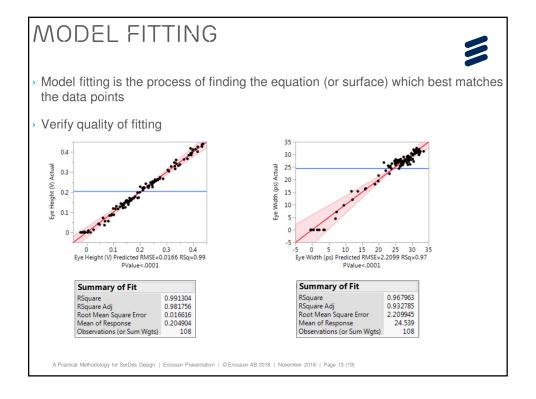

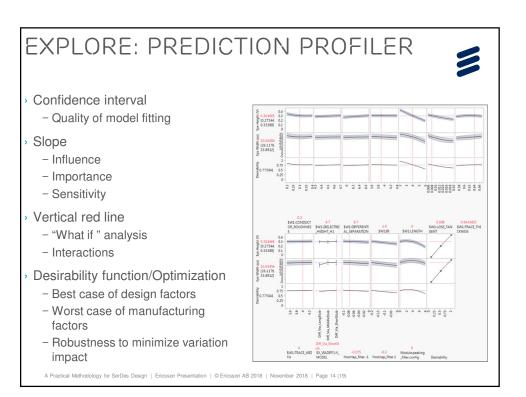

#### DESIGN OF EXPERIMENT PROCESS Definition - Link topology - Parameter space Define the experiments Define the - Define model Experiment - Create cases Simulation and evaluation - Simulate all cases - Quantify performance of all cases Model fitting - Response surface model **Model Fitting** - Least squares fit Explore - Virtual "what if" analysis Statistical - Optimize Explore Tool - Defects per million (DPM) analysis A Practical Methodology for SerDes Design | Ericsson Presentation | @ Ericsson AB 2018 | November 2018 | Page 8 (19)

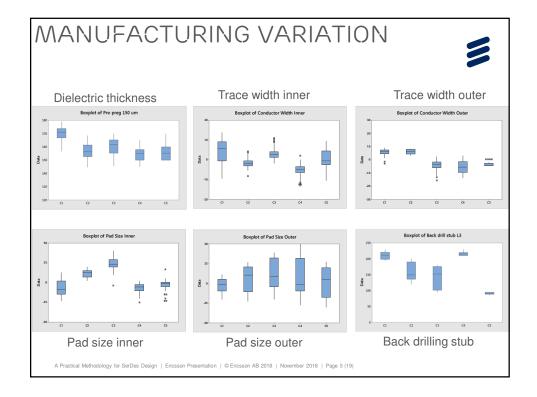

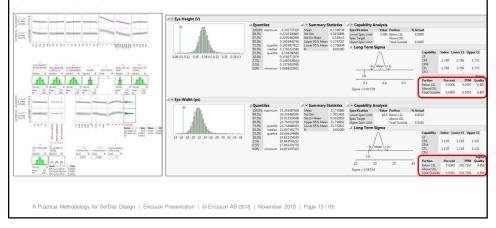

# **EXPLORE: DPM ANALYSIS**

- > Use the Equation Simulator to evaluate the response equation at millions of conditions.

- Assign a sampling distribution to each factor, i.e. trace length, manufacturing variation etc.

- Millions of system configurations can be evaluated in seconds to obtain realistic predicted yield plots.

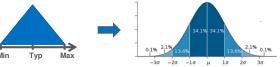

# QUESTION FOR IBIS-AMI

- > IBIS-AMI currently and traditionally uses a *Typ, Min, Max* parameter definition.

- This is based on a Best/Worst case scenario analysis. E.g. 100% confidence.

- Best/Worst case analysis has served us well during the years and still does in some cases, however more and more cases will not reach design closure using Best/Worst case analysis.

- When it does not reach design closure how will we know how many of our produced units will fail ???

A Practical Methodology for SerDes Design | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 16 (19)

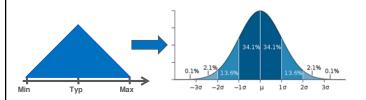

# SUGGESTION FOR IBIS-AMI

- If we add an option to IBIS-AMI to support distribution data for parameters as an average/mean and a variation/sigma.

- If we feel we can not assume a standard distribution we could even add support for other distributions.

- These parameters could be used in DOE analysis scenarios and could help us predict confidence intervals for our products as well as DPM (Defect Per million) predictions.

A Practical Methodology for SerDes Design | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 17 (19)

#### CONCLUSION

- Our design work is moving beyond Best Case, Worst Case analysis.

- We need to start working on an infrastructure both in modeling and tool support for statistical analysis.

- We need to ensure that we can get the correct information from IC and PCB vendors on parameter distributions.

- SI/PI statistical analysis is the next step to ensure our product quality.

A Practical Methodology for SerDes Design | Ericsson Presentation | @ Ericsson AB 2018 | November 2018 | Page 18 (19)

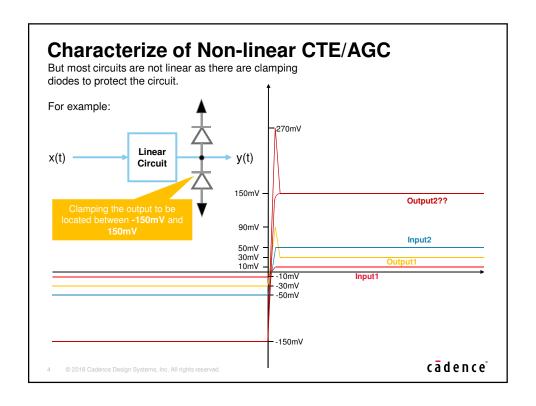

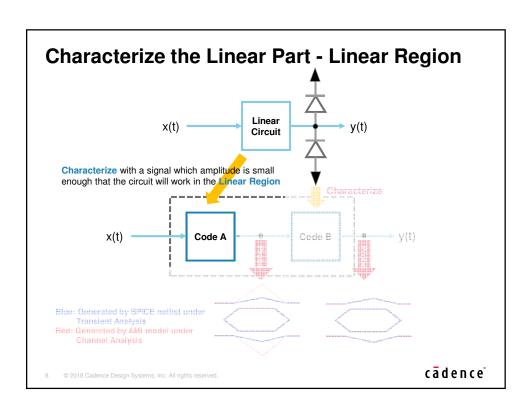

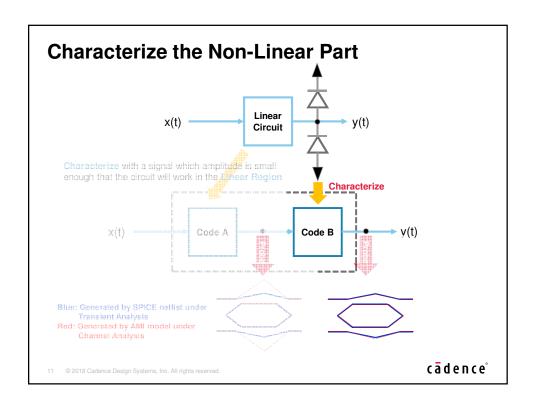

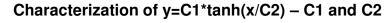

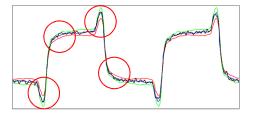

#### Characterize of Non-linear CTE/AGC

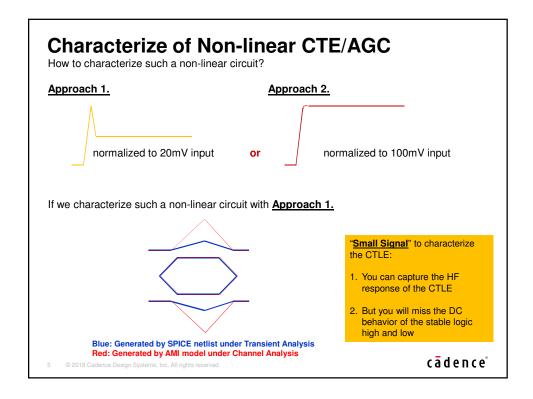

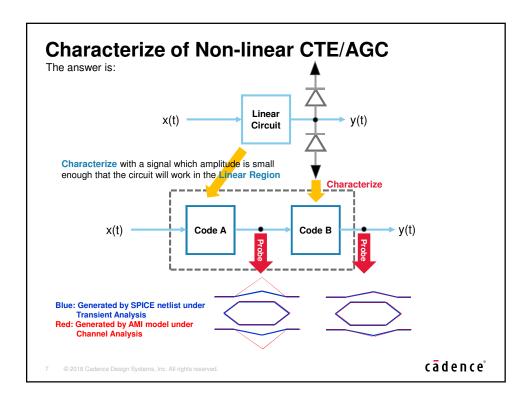

If we characterize such a non-linear circuit with Approach 2.

Blue: Generated by SPICE netlist under Transient Analysis Red: Generated by AMI model under Channel Analysis "Large Signal" to characterize the CTLE:

- You can capture the correct DC behavior of the stable logic high and low of the CTLE

- 2. But you will miss the HF response

For <u>Approach 1</u>, since the characterization can successfully capture the circuit's response at High Frequency range but miss the DC behavior, the model's simulation result can be well-correlated with SPICE transient analysis' result while a <u>Lossy Channel</u> is applied, which decays much more at High Frequency range.

For <u>Approach 2</u>, since the characterization can successfully capture the circuit's DC behavior but miss the response at High Frequency range, the model's simulation result can be well-correlated with SPICE transient analysis' result while a <u>Lossless Channel</u> is applied, which decays much less at High Frequency range.

How to have a model which can accommodate all kinds of channels?

6 © 2018 Cadence Design Systems, Inc. All rights reserve

cādence°

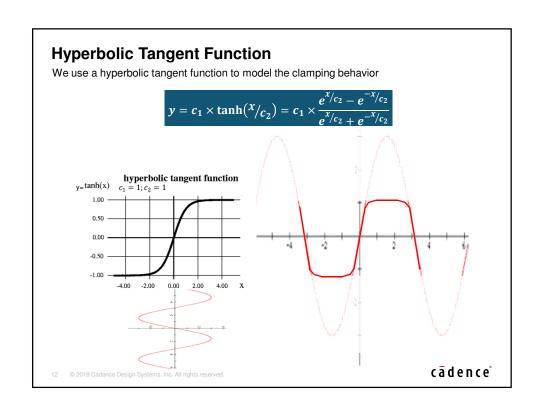

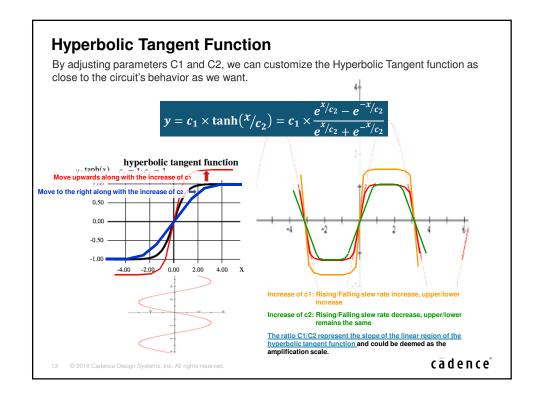

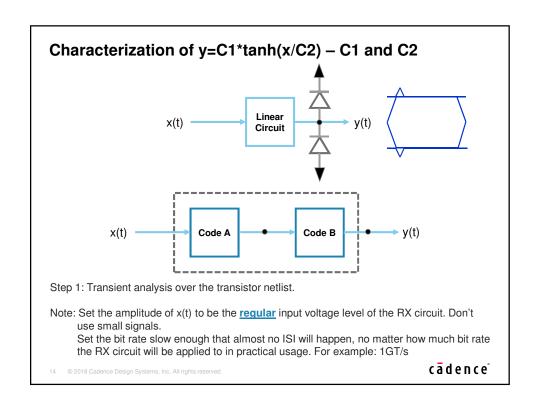

#### Characterization of y=C1\*tanh(x/C2) - C1 and C2

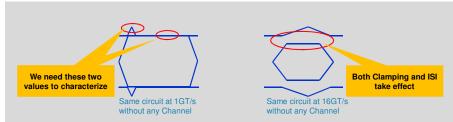

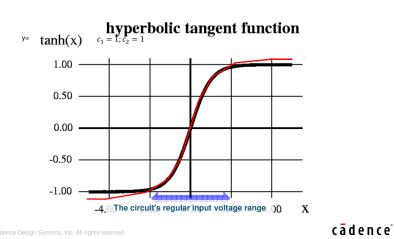

The reason to set the bit rate slow enough, no matter how much bit rate the RX circuit will be applied is:

- 1. We need the outer and inner contour of the eye which can tell us how much the clamping takes effect and only the clamping takes effect.

- An eye folded from a slow transition waveform can guarantee the amplitude of the outer and inner contour of the eye is only affected by the clamping but free from ISI.

- 3. Even without any Channel applied, it's impossible to get rid of ISI effect once the circuit is operated under a fast transmission rate

15 © 2018 Cadence Design Systems, Inc. All rights reserved

cādence°

Step 2: Start from the value of the outer contour of the eye generated by folding the waveform of transient analysis over the transistor netlist -> Take the value  $V_1$  to replace the  $\mathcal{C}_1$  and  $\mathcal{C}_2$  in the hyperbolic tangent function, that is,

$$V_{out}(t) = V_1 \tanh(\frac{V_{in}(t)}{V_1})$$

16 © 2018 Cadence Design Systems, Inc. All rights reserved

cādence°

#### Characterization of y=C1\*tanh(x/C2) - C1 and C2

Step 3: Overlap the two eye diagrams or record the value of the inner contours of these two eye diagrams.

If the eye diagram of the model under channel analysis has higher inner contour than the eye diagram of the transistor netlist under transient analysis -> Increase  $C_2$  with increment = 0.25 until the two eyes' inner contours meet each other.

$$V_{out}(t) = V_1 \tanh \left( \frac{V_{in}(t)}{V_1} \right)$$

If the eye diagram of the model under channel analysis has lower inner contour than the eye diagram of the transistor netlist under transient analysis -> Decrease  $C_2$  with increment = 0.25 until the two eyes' inner contours meet each other.

$$V_{out}(t) = V_1 \tanh \left( \frac{V_{in}(t)}{V_1} \right)$$

For example, if the comparison looks like the following, you should Increase  $C_2$

Blue: Generated by SPICE netlist under Transient Analysis Red: Generated by AMI model under

Channel Analysis

cādence

17 © 2018 Cadence Design Systems, Inc. All rights reserved

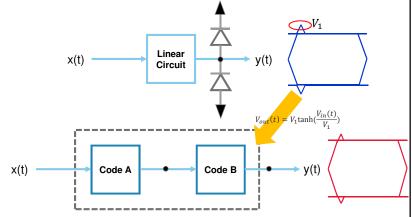

#### Characterization of y=C1\*tanh(x/C2) – C1 and C2 The reason to cause "the model under channel analysis has higher inner contour than the eye diagram of the transistor netlist under transient analysis" is: hyperbolic tangent function y=tanh(x) $c_1 = 1; c_2 = 1$ 1.00 -0.50 -2.00 0.00 4.00 Black: The characteristics of the transistor Blue: Generated by SPICE netlist under Transient Analysis netlist Red: Generated by AMI model under Channel Analysis Red: The characteristics of the model while applying $V_1$ to be $\mathcal{C}_1$ and $\mathcal{C}_2$ of the hyperbolic tangent function cā dence

#### Characterization of y=C1\*tanh(x/C2) - C1 and C2

Step 4: Overlap the two eye diagram or record the value of the outer contour of these two eye diagram.

If the eye diagram of the model under channel analysis has higher outer contour than the eye diagram of the transistor netlist under transient analysis -> Decrease  $C_1$  with increment = 0.25 until the two eyes' outer contour meet each other.

$$V_{out}(t) = V_1 \tanh\left(\frac{V_{in}(t)}{V_2}\right)$$

If the eye diagram of the model under channel analysis has lower outer contour than the eye diagram of the transistor netlist under transient analysis -> Increase  $C_1$  with increment = 0.25 until the two eyes' outer contour meet each other.

$$V_{out}(t) = V_1 \tanh\left(\frac{V_{in}(t)}{V_2}\right)$$

In our previous example, after adjusting  $C_2$ , if the comparison looks like the following, you should **Increase**  $C_1$

Blue: Generated by SPICE netlist under Transient Analysis Red: Generated by AMI model under

cādence°

Channel Analysis

19 © 2018 Cadence Design Systems, Inc. All rights reserved.

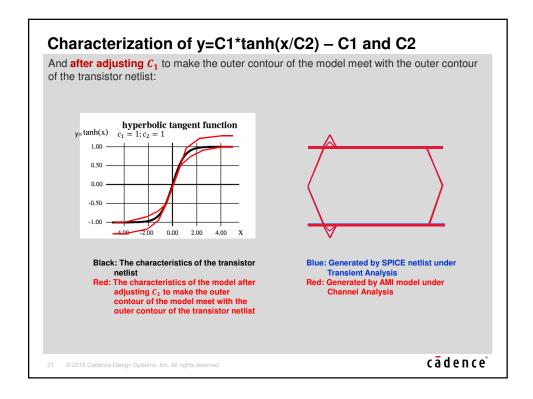

#### Characterization of y=C1\*tanh(x/C2) – C1 and C2 The reason to cause "the model under channel analysis has Lower outer contour than the eye diagram of the transistor netlist under transient analysis" after adjusting $C_2$ is: hyperbolic tangent function $y = \tanh(x)$ $c_1 = 1; c_2 = 1$ 1.00 -0.50 -2.00 0.00 4.00 Black: The characteristics of the transistor Blue: Generated by SPICE netlist under Transient Analysis netlist Red: Generated by AMI model under Channel Analysis Red: The characteristics of the model after adjusting $\mathcal{C}_2$ to make the inner contour of the model meet with the inner contour of the transistor netlist cādence

#### Characterization of y=C1\*tanh(x/C2) – C1 and C2

Step 5: Go back to Step 3 & Step 4 and keep iterating until you reach a satisfied result.

At the end when you reach a satisfied result, it doesn't imply that we have a hyperbolic tangent function which perfectly overlaps with the circuits characteristics but means that in the circuit's regular input voltage range, we have a hyperbolic tangent function which gets as close to the circuit's characteristics as we wish.

#### AMI\_GetWave()

Does a Hyperbolic Tangent Function have a corresponding frequency response?

Ans: <u>Almost impossible</u> because one of the criteria for a function to be Fourier transformable is

$$\int_{-\infty}^{\infty} |f(x)| dx < \infty$$

(Absolutely Integrable)

And obviously, Hyperbolic Tangent function fails this criteria. However, just like we can mathematically deduce the Fourier Transform of a unit step function  $(F\{u(t)\} = \frac{1}{j\omega} + \pi\delta(\omega))$ , we can also mathematically have Hyperbolic Tangent function Fourier Transformed as:

$$F\{\tanh(t)\} = j\sqrt{\frac{\pi}{2}} \cdot \operatorname{csch}\left(\frac{\pi\omega}{2}\right)$$

But what does a Hyperbolic Cosecant function look like?

23 © 2018 Cadence Design Systems, Inc. All rights reserved

cādence°

#### AMI\_GetWave()

=> What's the value at DC and LF range?

The most intuitive way to model a Hyperbolic Tangent function is to implement it in <u>AMI\_GetWave()</u>

cādence°

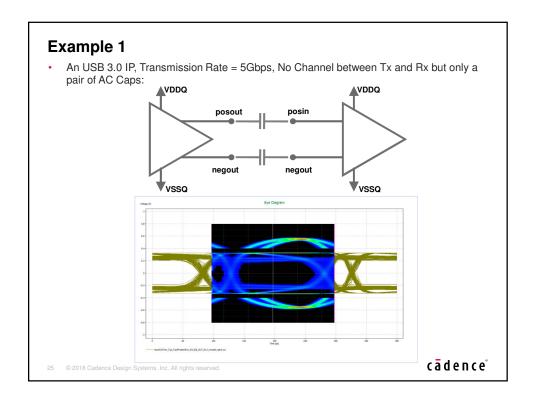

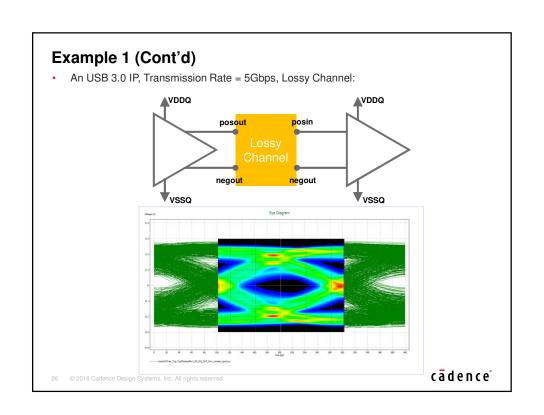

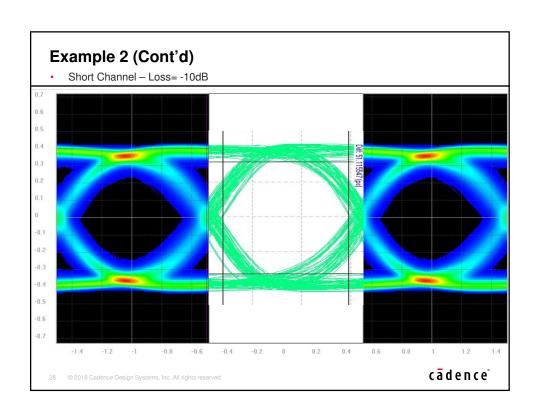

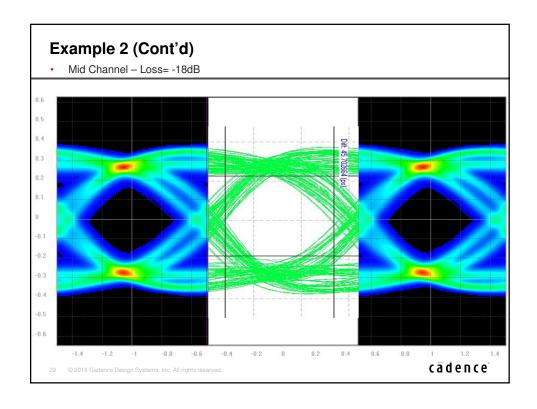

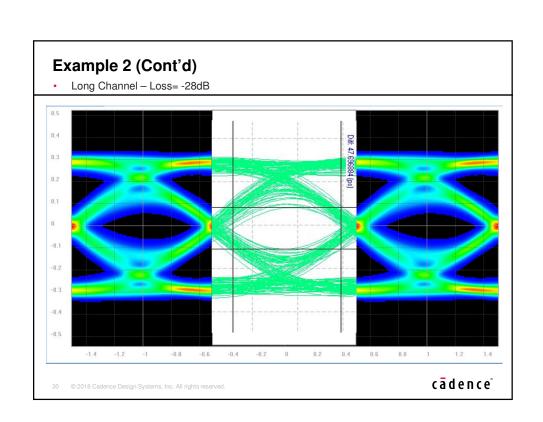

# Example 2 • A PCIe Gen 4.0 IP, Transmission Rate = 16Gbps, M31 published on CDNLive Taiwan 2018 Rough Block Diagram of RX EQ: CTE (w clamping) Probe here 27 © 2018 Cadence Design Systems, Inc. All rights reserved.

#### Conclusion

- Clamping diodes or circuits with similar behaviors are deemed as protection means and so common to be in most designs which makes most designs to be Non-Linear.

- We suggest Hyperbolic Tangent Function to be the optimal choice to describe such nonlinearity of circuits.

- We suggest a methodology with which model engineer can approach a nonlinear clamping behavior ultimately.

- Hyperbolic Tangent Function is hard to be implemented in AMI\_Init() due to its nature but can be easily and intuitively implemented in AMI\_GetWave(), for this we even suggest a simplified code.

- According to the description above, this implementation will limit the so-compiled AMI model to work properly in a "Time Domain Analysis" channel simulator but fail to behave as we desire in a "Statistical" channel simulator.

- Correlations against SPICE transient analysis are provided and it proves models generated by the methodology we proposed here can accommodate all kinds of channels.

31 © 2018 Cadence Design Systems, Inc. All rights reserved.

cādence°

See you on IBIS Summit 2019

© 2018 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and Spectre are registered trademarks and Sigrity, SystemSI, and T2B are trademarks of Cadence Design Systems, Inc. in the United States and other countries. All rights reserved. All other trademarks are the property of their respective owners.

## MODEL CORRELATION FOR IBIS-AMI

Asian IBIS Summit, Taipei, Taiwan, November 16, 2018 Authors:

Wenyan Xie, Guohua Wang, David Zhang, Anders Ekholm

### **AGENDA**

- > Why IBIS-AMI correlation

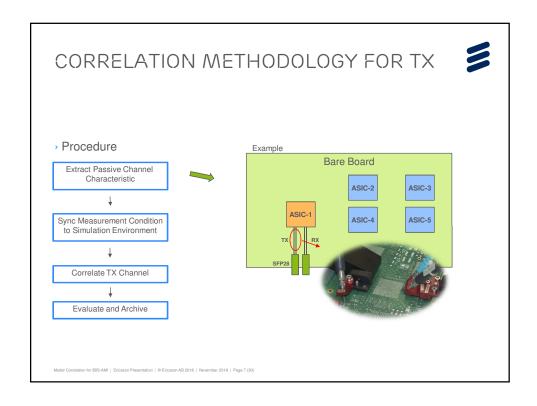

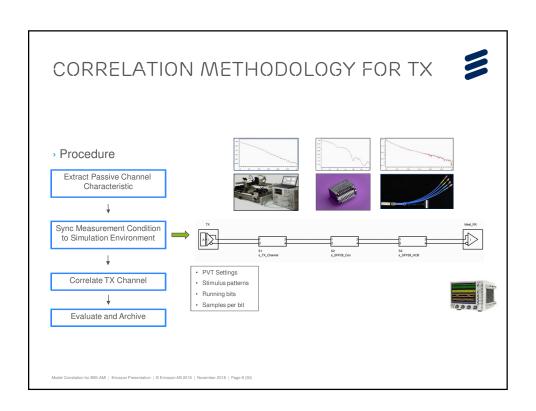

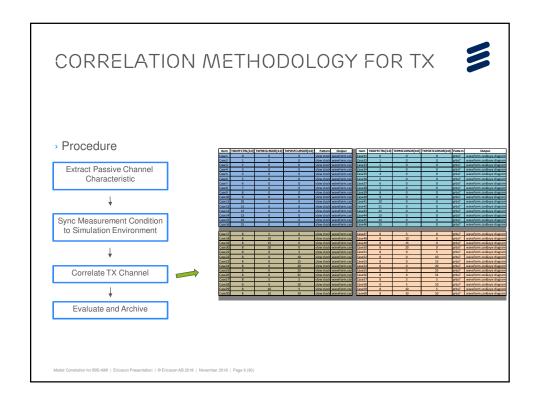

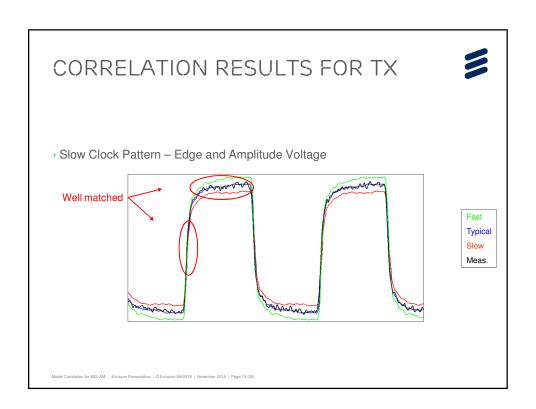

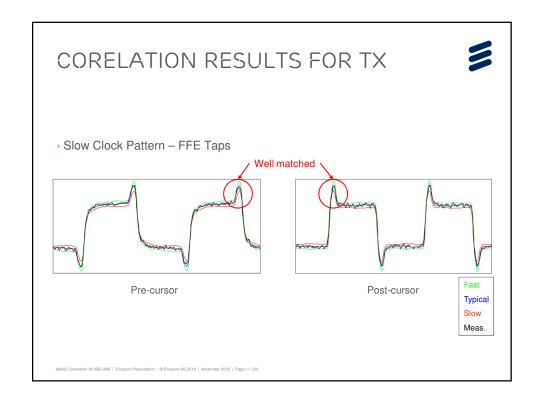

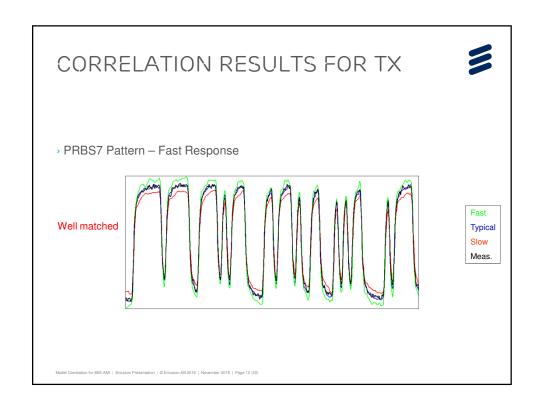

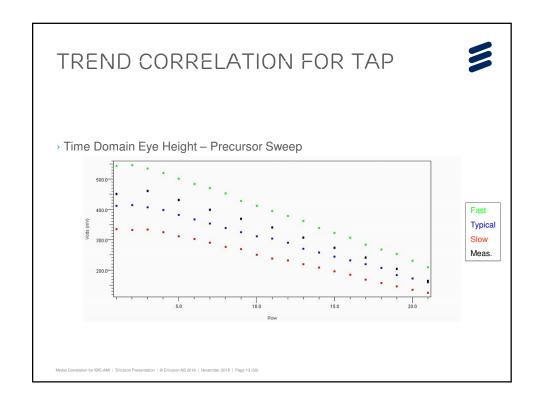

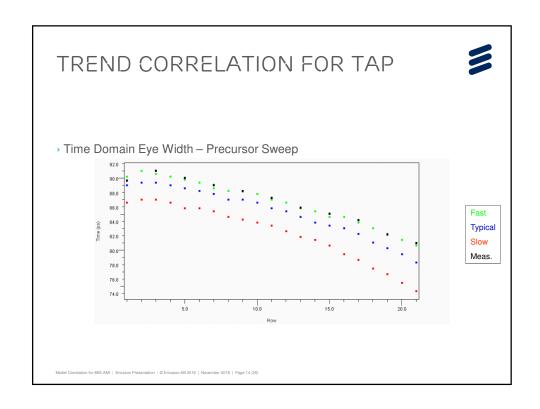

- Correlation methodology for TX

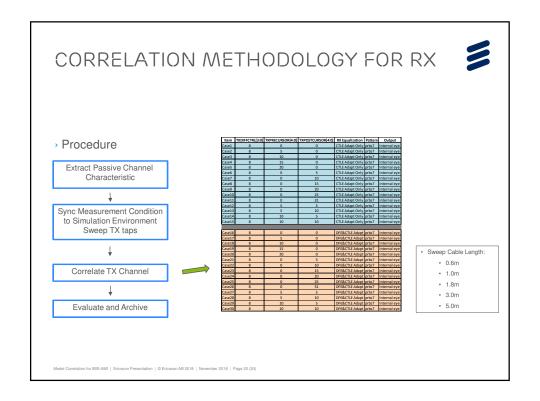

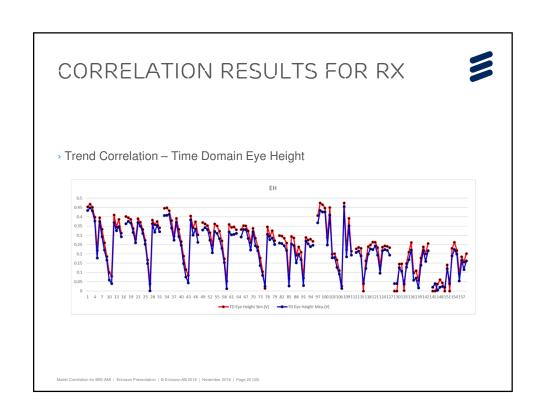

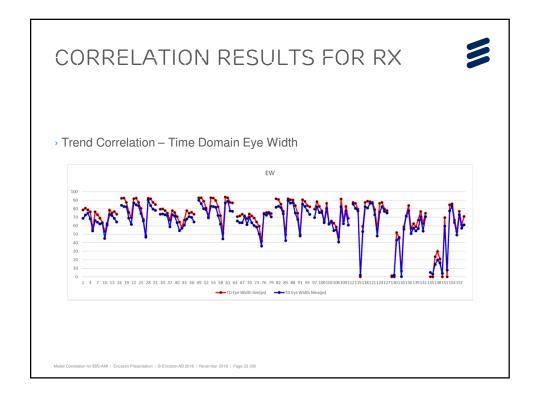

- Correlation methodology for RX

- Correlation criteria

- Question and suggestion

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 2 (30

### **AGENDA**

- > Why IBIS-AMI correlation

- Correlation methodology for TX

- Correlation methodology for RX

- Correlation criteria

- Question and suggestion

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 3 (30

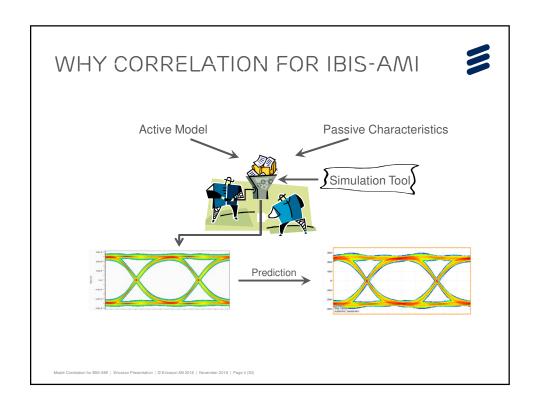

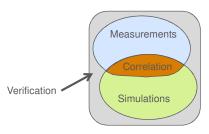

### WHY CORRELATION FOR IBIS-AMI

Correlation not only can verify simulation model's accuracy, but also can increase the verification coverage once model is matched to real tests. With the correlation, the simulation results can be the part of verification to cover some cases that measurement can not touch.

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 5 (3)

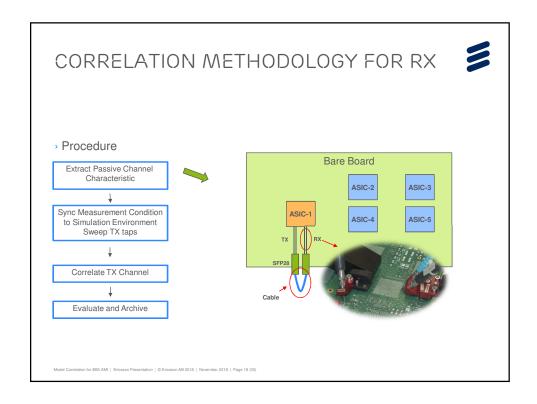

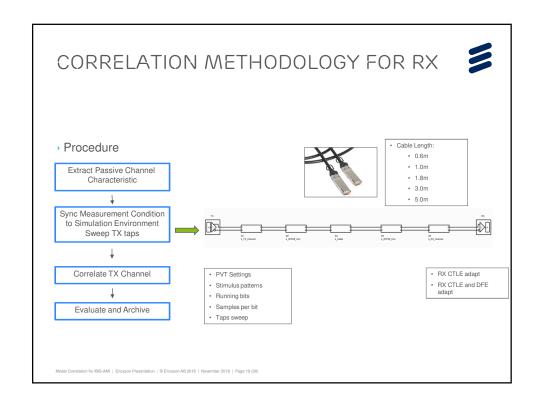

### **AGENDA**

- > Why IBIS-AMI correlation

- Correlation methodology for TX

- > Correlation methodology for RX

- › Correlation criteria

- Question and suggestion

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 6 (30

### **AGENDA**

- > Why IBIS-AMI correlation

- > Correlation methodology for TX

- > Correlation methodology for RX

- › Correlation criteria

- > Question and suggestion for

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 17 (3

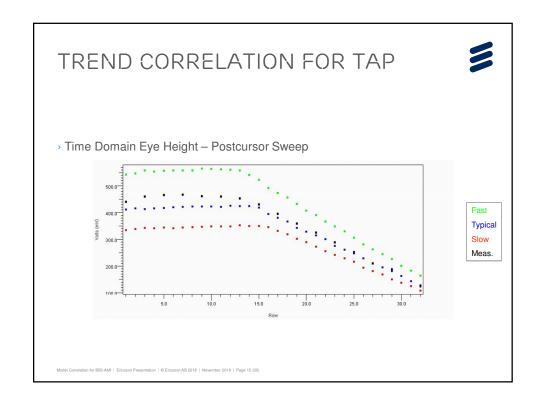

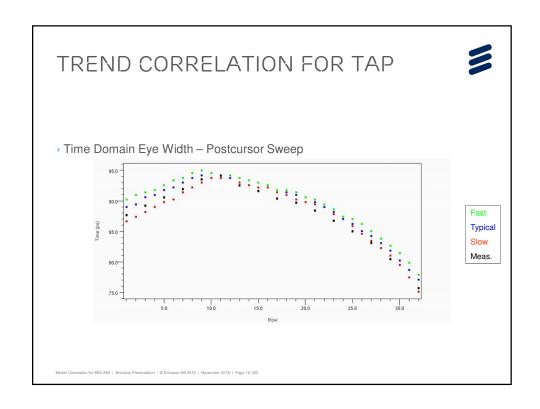

## CORRELATION WITH INTERNAL EYE Based on the accurate TX model, now scan internal eye with different tap settings of TX model THE PROPERTY OF THE PROPERTY OF

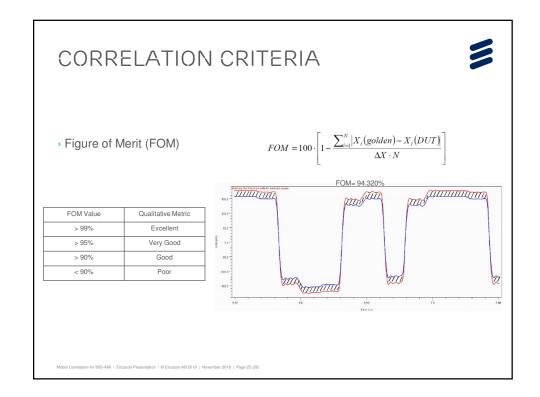

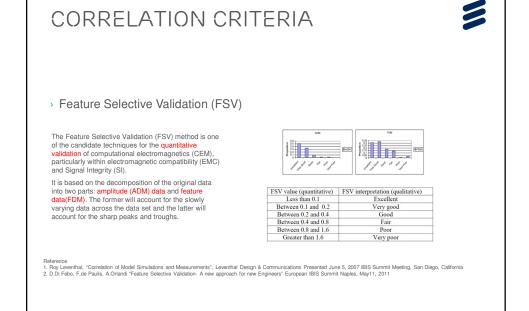

### **CORRELATION CRITERIA**

- More metrics to correlate

- Besides 5 metrics "high level, low level, rise time, fall time, and duty cycle", more metrics are necessary: slew rate, cursor pillars..and the metrics should have different weight in final

Reference

1. David Banas, "IBIS-to-Spice Correlation a story of 5 metrics", Presented June 5, 2007 IBIS Summit San Diego, California

### **AGENDA**

- > Why IBIS-AMI correlation

- Correlation methodology for TX

- Correlation methodology for RX

- Correlation criteria

- Question and suggestion

### QUESTION AND SUGGESTION

> In the paper, Measurement is on Typical corner. No Fast and Slow corners measurement data. So,

Can we trust the Fast and Slow corners simulation data, even though Typical correlates very well?

How much do the corners of AMI model match the real silicon's behavior? 99.99%...? It is a statistical problem.

> We need to introduce the statistical distribution for Fast/Typical/Slow corners of

> We need more metrics for correlation evaluation. Some are proposed in this paper.

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 29 (3)

Model Correlation for IBIS-AMI | Ericsson Presentation | © Ericsson AB 2018 | November 2018 | Page 30 (30)

## Study of DDR Asymmetric Rt/Ft in Existing IBIS-AMI Flow

Asian IBIS Summit Taipei, Taiwan November 16th, 2018

Wei-hsing Huang, SPISim Wei-hsing.Huang@spisim.com Wei-kai Shih, SPISim Wei-kai.Shih@spisim.com

### Agenda:

- Motivation

- Background

- Asymmetric Rt/Ft

- AMI Init

- AMI\_GetWave

- Summary

- Q&A

2

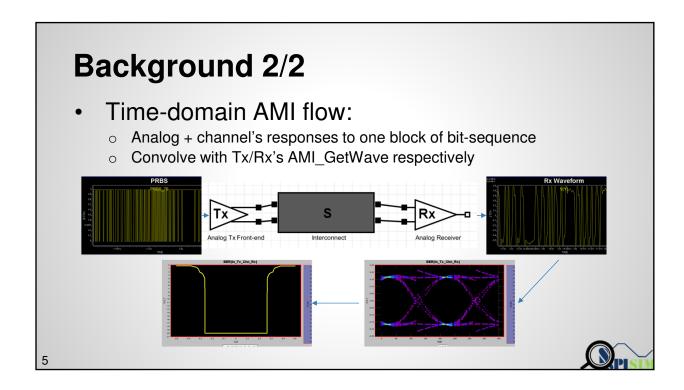

### **Motivation**

- IBIS-AMI analysis flows:

- o Statistical: use impulse response and AMI\_Init

- Time-domain: use convolution and mainly AMI\_GetWave

- Existing applications focused on SERDES

- Differential, centered around V = 0.0

- Symmetric rise-time (Rt) /fall-time (Ft)

- How DDR may work in existing AMI flow?

- o Single-ended e.g. DQ

- Asymmetric Rt/Ft

3

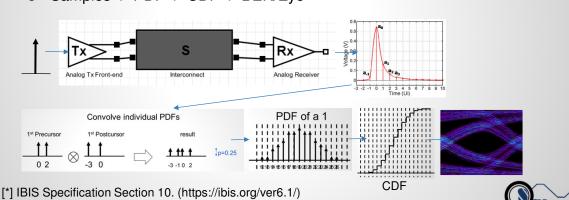

### **Background 1/2**

- Statistical AMI flow: [\*]

- Impulse Response for analog + channel (Linear Time Invariant, LTI)

- Samples -> PDF -> CDF -> BER/Eye

Page 53 of 59

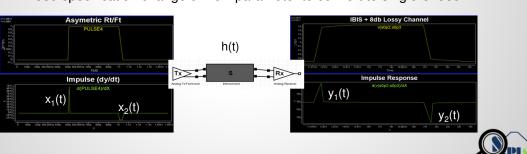

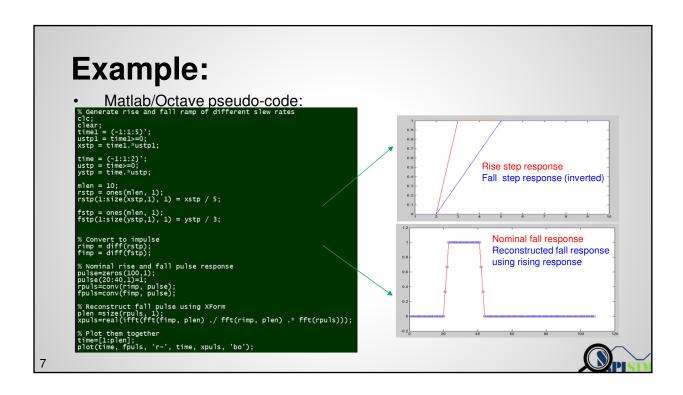

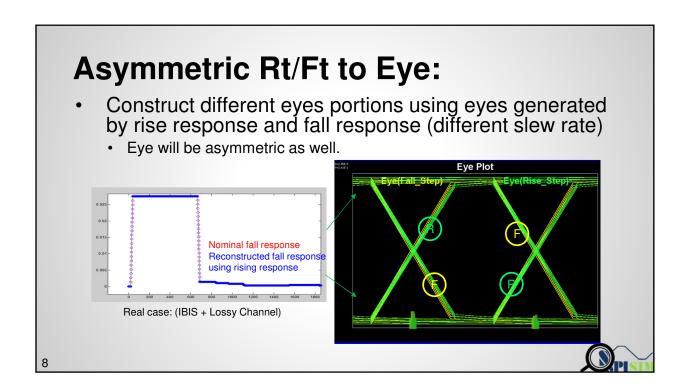

### **Asymmetric Rt/Ft to Impulse:**

- Linear transform between Rt/Ft:

- o Rise:  $y_1(t) = x_1(t) * h(t)$

- Fall:  $y_2(t) = x_2(t) * h(t)$

- o Fall:  $x_2(t) = x_1(t) * X form(t) \Rightarrow y_2(t) = y_1(t) * X form(t)$

- o Simulator knows  $y_1$ &  $y_2$  , thus Xform(t). It can then reconstruct either  $y_1$  or  $y_2$  from  $y_2$  or  $y_1$  used in AMI\_Init

- DC info disappeared during differentiation (to get impulse response). Has gap!

Need specification change or new parameter to convert to single-ended.

### ISI Eye Construction with a Tree Structure

| 3 | 2 | 1 | Cursor<br>(0) | -1 |

|---|---|---|---------------|----|

| 0 | 0 |   |               |    |

| 1 | 0 | 0 | 1             | 0  |

| 0 | 4 |   |               |    |

| 1 | , |   |               |    |

| 0 | 0 | 1 |               |    |

| 1 | 0 |   |               | 1  |

| 0 | 4 |   |               |    |

| 1 | , |   |               |    |

Let  $V_n(ab)$  be the contribution of ISI from the *n*thpre-cursor edge when the nth pre-cursor=a and (n-1)th pre-cursor=b, i.e. the nth pre-cursor edge is an *a*  $\rightarrow b$  transition

When 2nd pre-cursor logic value = 0, cursor logic value =1, all possible values for the accumulated ISI from 2nd and 1st pre-cursors can be put into a row vector :  $[V_2(00) + V_1(01), V_2(01) + V_1(11)]$ . There are two elements in the vector due to two possible values of the 1st pre-cursor

Extending to the 3<sup>rd</sup> pre-cursor: When 3<sup>rd</sup> pre-cursor =0, there are 4 possible accumulated ISI

$[V_3(00) + V_2(00) + V_1(01), V_3(00) + V_2(01) + V_1(11)]$  and  $[V_3(01) + V_2(10) + V_1(01), V_3(01) + V_2(11) + V_1(11)]$

### **Recursive Algorithm for ISI Eye Construction**

| n | n-1 | 1 n-2    | Cursor (0) |  |

|---|-----|----------|------------|--|

| 0 | 0   | xxxxxxxx | 1          |  |

| 1 |     |          |            |  |

| 0 | 1   |          |            |  |

| 1 |     |          |            |  |

$W_n(ab)$ : row vector consisting all possible values of the accumulated ISI from the *n*th pre—cursor to cursor when logic value of the *n*th pre—cursor is *a* and logic value at cursor is b

$W_1(01) = [V_1(01)]$  $W_1(11) = [V_1(11)]$  $W_2(01) = [V_2(00) + V_1(01), V_2(01) + V_1(11)]$  $W_2(11) = [V_2(10) + V_1(01), V_2(11) + V_1(11)]$

$W_n(01) = [V_n(00) + W_{n-1}(01), V_n(01) + W_{n-1}(11)]$  $W_n(11) = [V_n(10) + W_{n-1}(01), V_n(01) + W_{n-1}(11)]$

10

## **PDF Computation for ISI Eye**

| Waveform value | PDF of the waveform value                                                                                            | Notes |

|----------------|----------------------------------------------------------------------------------------------------------------------|-------|

| $V_n(ab)$      | $P_{V_n(ab)}(V) = \delta(V - V_n(ab))$                                                                               |       |

| $W_1(01)$      | $P_{W_1(01)} = P_{V_1(01)} \ P_{W_1(11)} = P_{V_1(11)}$                                                              |       |

| $W_n(01)$      | $P_{W_n(01)} = \frac{1}{2} P_{W_{n-1}(01)} \otimes P_{V_n(00)}(V) + \frac{1}{2} P_{W_{n-1}(11)} \otimes P_{V_n(01)}$ |       |

| $W_n(11)$      | $P_{W_n(11)} = \frac{1}{2} P_{W_{n-1}(01)} \otimes P_{V_n(10)}(V) + \frac{1}{2} P_{W_{n-1}(11)} \otimes P_{V_n(11)}$ |       |

|                |                                                                                                                      |       |

This is a Dirac delta when there is no jitter (ISI takes discrete value without jitter) With jitter the Dirac delta will spread out into a continuous distribution. But the recursive relation remains same

11

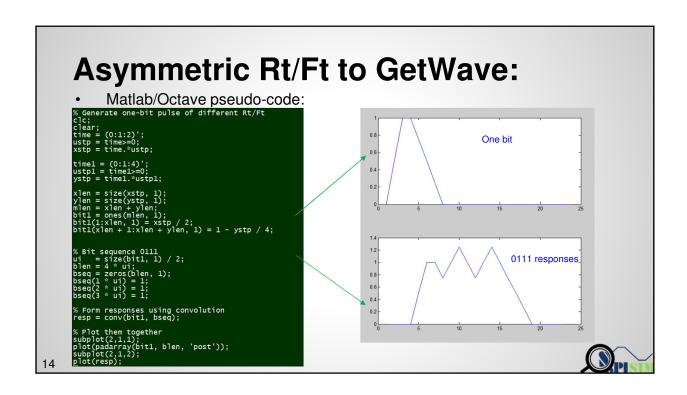

### **Asymmetric Rt/Ft to GetWave:**

- · Result will be OK if:

- Bit-sequence waveform at Rx is simulated result from bit-sequence input at Tx

- This may not be the case mostly as it takes longer to run.

- · Result will have errors if:

- Final waveform at Rx is from one bit simulated Rx response convolved with bit-sequence impulse at  $\mathsf{Tx}$

12

# Asymmetric Rt/Ft to GetWave: Bit 011 using convolution with symmetric Rt/Ft Glitch will happen for asymmetric Rt/Ft The symmetric Rt/Ft The symmetric Rt/Ft The symmetric Rt/Ft

### **Summary:**

- Existing IBIS-AMI flow:

- o Can be used for driver with asymmetric Rt/Ft.

- o Asymmetric effects can be handled within EDA tools/Simulator.

- o Assuming AMI model does not behave differently to rise/fall responses.

### Statistical flow:

- o Linear transform between rise/fall can be applied to model's response.

- Use rise and fall response to construct eye.

- Tree/sequence based superposition will eliminate these glitches.

### Time-domain flow:

- Convolution using one bit pulse will have errors.

- Using step reponse based superposition may avoid such errors.

15

Page 59 of 59