# WELCOME FROM RANDY WOLFF, IBIS OPEN FORUM

# Ladies and Gentlemen,

As chair of the IBIS Open Forum it is my pleasure to welcome you to the 2019 Asian IBIS Summit in Taipei and to thank you for your presentations and participation. We are grateful to our sponsors ANSYS, Cadence Design Systems, and Synopsys for making this event possible.

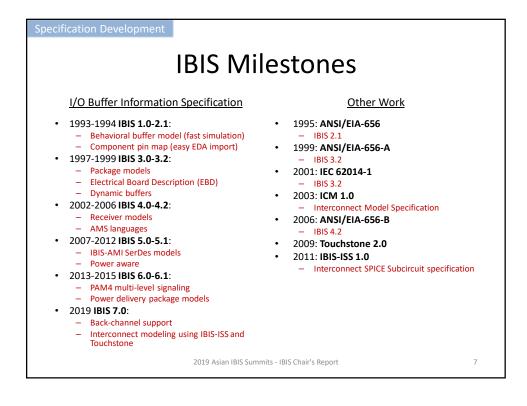

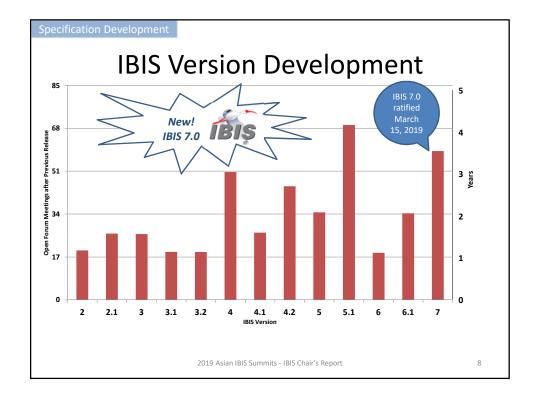

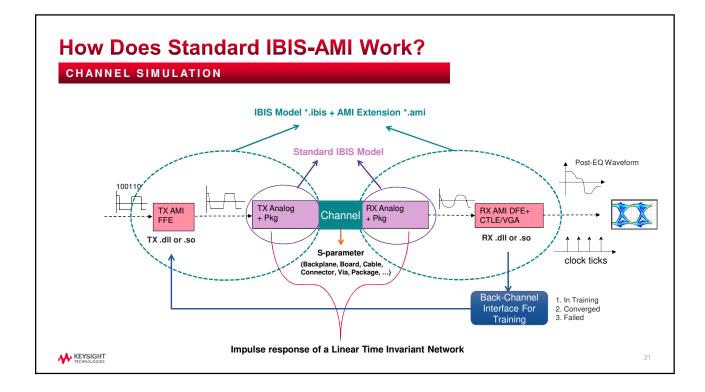

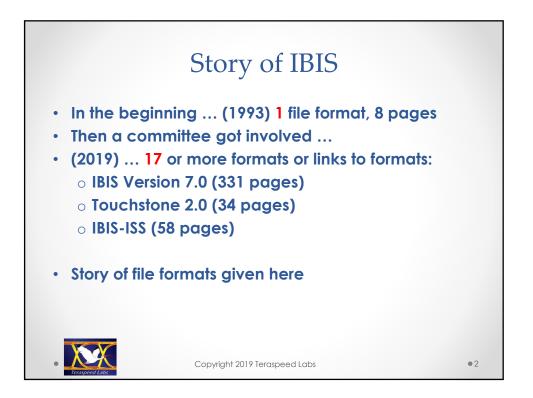

Since 1993 IBIS has provided the digital electronics industry with specifications to make signal, timing, and power integrity analyses much easier and faster. With the introduction of IBIS-AMI in 2008, the IBIS community generated new energy for high speed electronic design. IBIS is now known by engineers worldwide and is a required technology for many applications. IBIS Version 7.0 was released in 2019, adding enhancements for IBIS-AMI and supporting advanced interconnect modeling.

Support for IBIS in Asia has been strong, and the IBIS Open Forum looks forward to continued innovation and contributions from technology companies in Asia. Thank you!

Jun U. W.M

Randy Wolff Micron Technology Chair, IBIS Open Forum

# WELCOME FROM RANDY WOLFF, IBIS OPEN FORUM

女士們先生們,

作為 IBIS 開放論壇的主席,我很高興地歡迎您參加 2018 年在台北舉辦的亞洲 IBIS 峰會,感謝您的介紹和參與。我們非常感謝我們的讚助商 ANSYS, Cadence Design Systems,和 Synopsys,以使這一事件成為可能。

自 1993 年以來, IBIS 為數字電子行業提供了使信號, 時序和電源完整性分 析更容易和更快速的規範。隨著 IBIS-AMI 在 2008 年的推出, IBIS 社區為高 速電子設計創造了新的能量。 IBIS 現在已被世界各地的工程師所了解, 是許 多應用所需的技術。2019 年, 新的 IBIS 7.0 版本包含了更多的 IBIS-AMI 模 型和互联接口模型的定义及提升。

IBIS 在亞洲的支持一直很強, IBIS 開放論壇期待著亞洲技術公司的不斷創新和貢獻。

谢谢!

Purt U. W.M

Randy Wolff (**兰迪·沃尔夫**) Micron Technology 公司 主席, IBIS 开放论坛

# AGENDA AND ORDER OF THE PRESENTATIONS

# (The actual agenda might be modified)

|       | IBIS SUMMIT MEETING AGENDA                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 9:00  | SIGN IN<br>- Vendor Tables Open at 8:30                                                                                     |

| 9:30  | WELCOME<br>- Randy Wolff (Chair, IBIS Open Forum)<br>(Micron Technology, USA)                                               |

| 9:45  | IBIS Chair's Report                                                                                                         |

| 10:05 | <pre>Introducing IBIS Version 7.0</pre>                                                                                     |

| 10:30 | BREAK (Refreshments and Vendor Tables)                                                                                      |

| 10:50 | How to Obtain Buffer Impedance from IBIS                                                                                    |

| 11:20 | <pre>IBIS-AMI &amp; COM Co-design for 25G Serdes</pre>                                                                      |

| 12:00 | FREE BUFFET LUNCH (Hosted by Sponsors)<br>- Vendor Tables                                                                   |

| 13:30 | Innovations in DDR Memory Simulation                                                                                        |

| 14:10 | Channel Simulation Over DDR4/5 and Above                                                                                    |

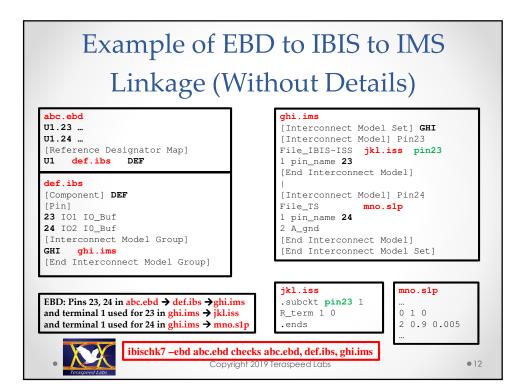

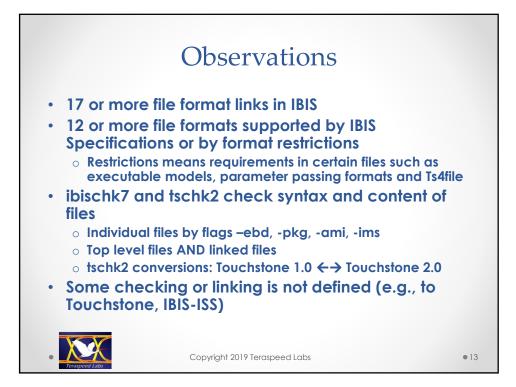

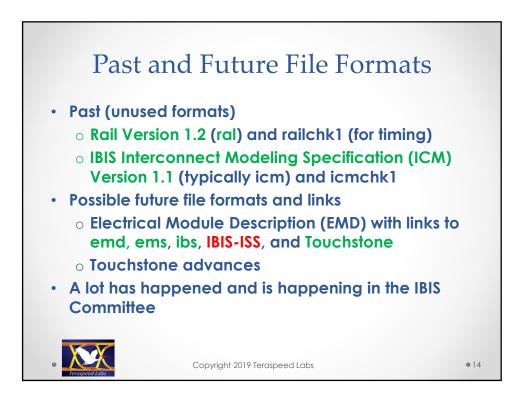

| 14:40 | <b>IBIS File Format Links 68</b> Bob Ross (Teraspeed Labs, USA)         [Presented by Randy Wolff (Micron Technology, USA)] |

| 15:10 | CONCLUDING ITEMS                                                                                                            |

15:15 END OF IBIS SUMMIT

- 15:15 **BREAK** (Refreshments and Vendor Tables)

- 15:35 VENDOR PRESENTATIONS, MODERATOR

Lance Wang (Vice-chair, IBIS Open Forum)

(Zuken, USA)

- 16:50 END OF VENDOR PRESENTATONS

\_\_\_\_\_

| Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Task Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| <ul> <li>Interconnect Task Group         <ul> <li>Chair: Michael Mirmak, Intel</li> <li><u>http://ibis.org/interconn_wip/</u></li> <li>Develop on-die/package/module/connector interconnect modeling BIRDs</li> </ul> </li> <li>Advanced Technology Modeling Task Group         <ul> <li>Chair: Arpad Muranyi, Mentor, A Siemens Business</li> <li><u>http://ibis.org/atm_wip/</u></li> <li>Develop most other technical BIRDs</li> </ul> </li> <li>Quality Task Group         <ul> <li>Chair: Mike LaBonte, SiSoft (MathWorks)</li> <li><u>http://ibis.org/quality_wip/</u></li> <li>Oversee IBISCHK parser testing and development</li> </ul> </li> <li>Editorial Task Group         <ul> <li>Chair: Michael Mirmak, Intel</li> <li><u>http://ibis.org/editorial_wip/</u></li> <li>Produce IBIS Specification documents</li> </ul> </li> </ul> |   |

| BIRD = Buffer Issue Resolution Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| 2019 Asian IBIS Summits - IBIS Chair's Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6 |

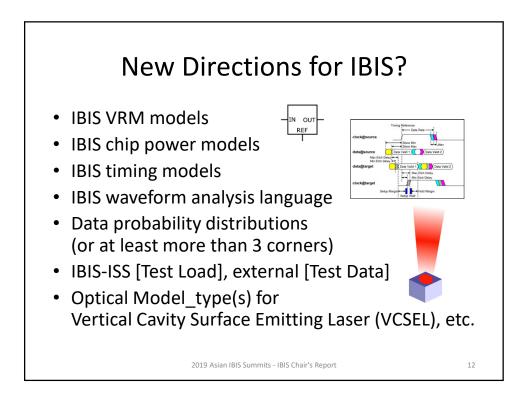

- Include optical links in analyses

- Analyze channel operating margin (COM), forward error correction (FEC), etc.

- Comply with any other new requirements posed by JEDEC, etc.

- What other data might IBIS formats convey?

2019 Asian IBIS Summits - IBIS Chair's Report

11

| BIRD Template Link on the BIRD |

|--------------------------------|

| Webpage                        |

| ID#   | Issue Title                                                                  | Requester                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Date<br>Submitted                                                                            | Date<br>Accepted      | Supportin<br>Version |

|-------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|----------------------|

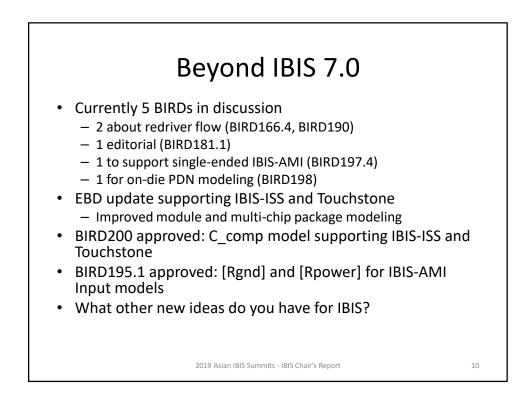

| 200   | C_comp Model Using IBIS-ISS or<br>Touchstone                                 | Randy Wolff, Micron Technology, Inc. Walter Katz, Signal Integrity Software, Inc.                                                                                                                                                                                                                                                                                                                                                                                          | July 9, 2019                                                                                 | September 27,<br>2019 |                      |

| 199   | Fix Rx_Receiver_Sensitivity<br>Inconsistencies                               | Arpad Muranyi, Mentor a Siemens Business                                                                                                                                                                                                                                                                                                                                                                                                                                   | March 19, 2019                                                                               | June 7, 2019          |                      |

| 198   | Keyword additions for On Die PDN<br>(Power Distribution Network)<br>Modeling | Kazuki Murata; Ricoh Co., Ltd.; Mnyoko Goto; Ricoh Co., Ltd.; Kazuyuki Sakata; Renesas<br>Electronis: Corporation; Kazunori Yamada; Renesas Electronics Corporation; Kouji Ichikawa;<br>Denso Corporation; Atsubali Tomishima; Toshuba Electronic: Devices & Storage Corporation;<br>Takashi Hasegawa; Sony LSI Design Inc; Koichi Seko, Panasonic Industrial Devices Systems<br>and Technology Co., Ltd.; Toshuk Kanamote, Hirosaki Linversiyi Megumi Ono; Socionext Inc. | March 11, 2019                                                                               |                       |                      |

| 197.4 | New AMI Reserved Parameters<br>DC_Offset and NRZ_Threshold                   | Walter Katz, SiSoft, Ambrish Varma, Cadence Design Systems, Randy Wolff, Micron<br>Technology, Justin Butterfield, Micron Technology, Fangyi Rao, Keysight Technologies                                                                                                                                                                                                                                                                                                    | November 27, 2018,<br>December 4, 2018, January<br>15, 2019, June 25, 2019,<br>July 23, 2019 |                       |                      |

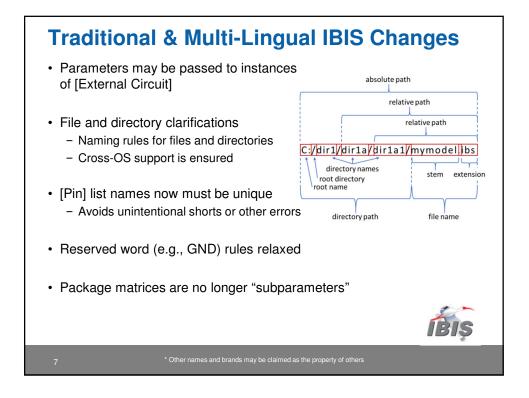

| 196.1 | Prohibit Periods at the End of File<br>Names                                 | Arpad Muranyi, Mentor Graphics, A Siemens Business                                                                                                                                                                                                                                                                                                                                                                                                                         | September 25, 2018,<br>October 12, 2018                                                      | October 12, 2018      | 7.0                  |

| 195.1 | Enabling [Rgnd] and [Rpower]<br>Keywords for Input Models                    | Michael Mirmak, Intel Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                | June 19, 2018, June 29, 2018                                                                 | August 31, 2018       |                      |

|       |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |                       |                      |

|       |                                                                              | 2019 Asian IBIS Summits - IBIS Chair's Report                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              | 1                     | 15                   |

| Number | Issue Title                                                   | Date<br>First Submitted | Date<br>Approved | Days One |

|--------|---------------------------------------------------------------|-------------------------|------------------|----------|

| 196.1  | Prohibit Periods at the End of File Names                     | 25-Sep-18               | 12-Oct-18        |          |

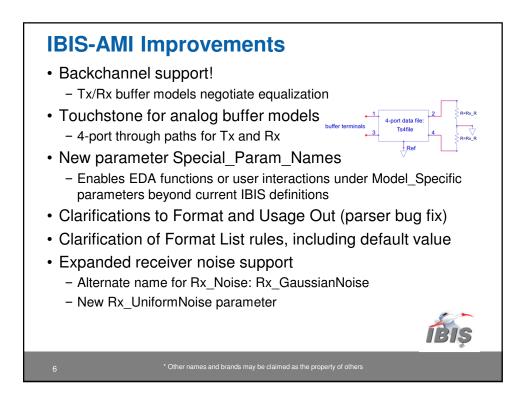

| 194    | Revised AMI Ts4file Analog Buffer Models                      | 2-May-18                | 29-Jun-18        | 58       |

| 193    | Figure 29 corrections                                         | 10-Jan-18               | 23-Mar-18        | 72       |

| 192.1  | Clarification of List Default Rules                           | 22-Aug-17               | 15-Sep-17        | 24       |

| 191.2  | Clarifying Locations for Si location and Timing location      | 28-Jun-17               | 15-Sep-17        | 79       |

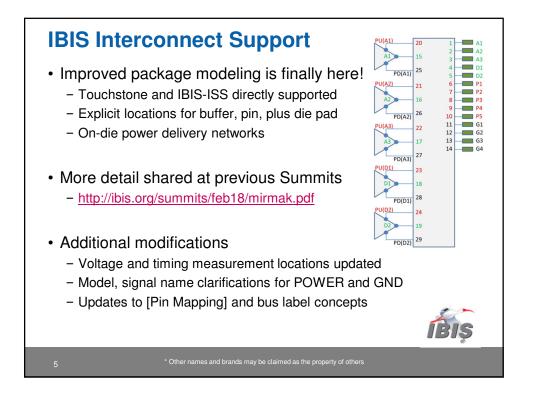

| 189.7  | Interconnect Modeling Using IBIS-ISS and Touchstone           | 27-Jan-17               | 29-Jun-18        | 518      |

| 188.1  | Expanded Rx Noise Support for AMI                             | 13-Dec-16               | 17-Feb-17        | 66       |

| 187.3  | Format and Usage Out Clarifications                           | 13-Dec-16               | 21-Apr-17        | 129      |

| 186.4  | File Naming Rules                                             | 29-Nov-16               | 14-Jul-17        | 227      |

| 185.2  | Section 3 Reserved Word Guideline Update                      | 13-Sep-16               | 6-Jan-17         | 115      |

| 184.2  | Model name and Signal name Restriction for POWER and GND Pins | 1-Sep-16                | 6-Jan-17         | 127      |

| 183    | [Model Data] Matrix Subparameter Terminology Correction       | 30-Aug-16               | 14-Oct-16        | 45       |

| 182    | POWER and GND [Pin] signal name as [Pin Mapping] bus label    | 30-Aug-16               | 14-Oct-16        | 45       |

| 180    | Require Unique Pin Names in [Pin]                             | 17-Feb-16               | 14-Oct-16        | 240      |

| 179    | New IBIS-AMI Reserved Parameter Special Param Names           | 13-Oct-15               | 18-Dec-15        | 66       |

| 165.1  | Parameter Passing Improvements for [External Circuit]s        | 9-Jan-14                | 15-Dec-17        | 1436     |

| 158.7  | AMI Ts4file Analog Buffer Models                              | 20-Feb-13               | 27-Oct-17        | 1710     |

| 147.6  | Back-channel Support                                          | 18-Oct-11               | 10-Mar-17        | 1970     |

|        |                                                               |                         | í                | Ric      |

# **IBIS 7.0 Timeline**

| Date       | Milestone                                             |

|------------|-------------------------------------------------------|

| 4/21/2017  | Vote to establish 7.0 as the next IBIS version passes |

|            | BIRD review and acceptance (30 meetings)              |

| 7/20/2018  | 7.0 BIRD set accepted                                 |

|            | Editorial task group drafts IBIS 7.0                  |

| 12/10/2019 | Editorial announces IBIS 7.0 Draft 1 ready Review     |

| 12/19/2018 | period begins 12/21/2018 at Open Forum                |

|            | Work begins to address comments                       |

| 1/18/2019  | Editorial announces IBIS 7.0 Draft 2 ready            |

| 1/25/2019  | Editorial announces IBIS 7.0 Draft 3 ready            |

| 2/22/2019  | Vote to ratify 7.0 scheduled for next meeting         |

| 3/15/2019  | IBIS 7.0 ratified                                     |

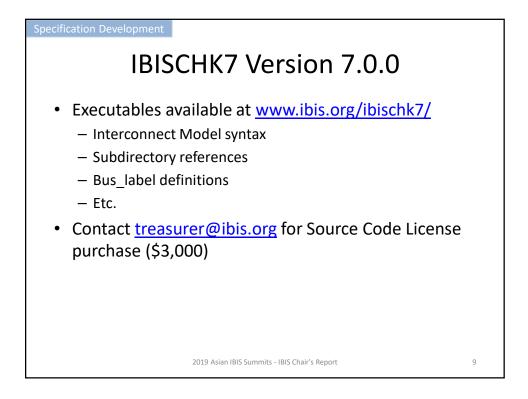

| 10/8/2019  | IBISCHK7 Version 7.0.0 parser source code released    |

|            | Ĺ                                                     |

# <section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

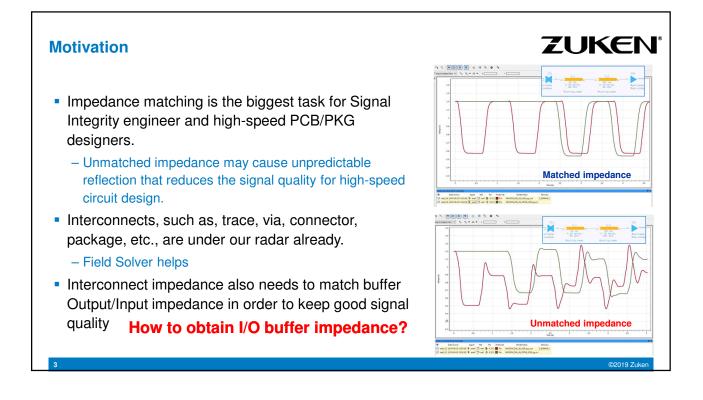

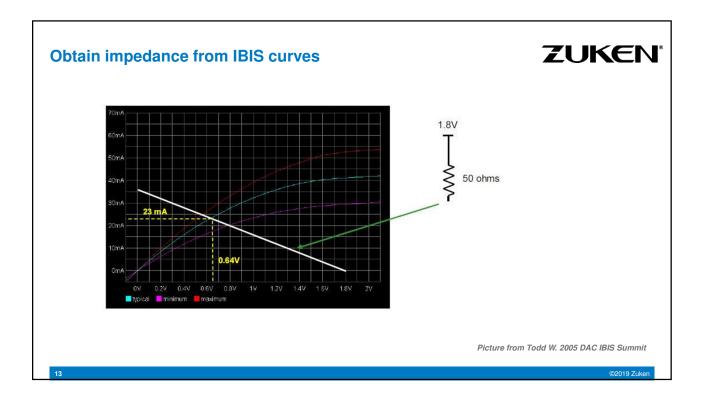

# Impedance Concept

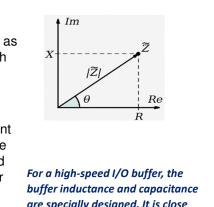

- where the magnitude |Z| represents the ratio of the voltage difference amplitude to the current amplitude, while the argument arg(Z) (commonly given the symbol  $\theta$  gives the phase difference between voltage and current). *j* is the imaginary unit and is used instead of *i* in this context to avoid confusion with the symbol for electric current.

- In Cartesian form, impedance is defined as Z = R + jX

- where the real part of impedance is the resistance R and the imaginary part is the reactance X.

ZUKEN

buffer inductance and capacitance are specially designed. It is close to minimum for the reactance X. So, in this case, the resistance R is the main factor for impedance matching.

|                                                                                                                                                                                                                                            |                                                                                                | 3.1 Extracting I-V Data from Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                            |                                                                                                | The first step to extracting the required I-V tables is understanding the buffer's operation. Analyze the buffer<br>schematic production of the step of the buffer's schematic must alway be the production of a paylocable high<br>tables and the step of           |

|                                                                                                                                                                                                                                            | ODELING COOKBOOK                                                                               | 3.1.1 Simulation Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ,                                                                                                                                                                                                                                          | For IBIS Version 4.0<br>Prepared By:<br>The IBIS Open Forum                                    | A typical I-V table simulation setup for an output or IO buffer is shown in Figure 3.1 below. For this example,<br>the buffer being analyzed is a standard 3-tatle buffer with a single push-qual output stage. The buffer uses<br>electrostatic discharge posteriotic modes in additos to its parasitist driver disedes. The buffer's clamp supplies<br>are assumed identical to its driver supply (Vce breinafter).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| А                                                                                                                                                                                                                                          | pproved September 15, 2005                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Serier Edder:<br>Mchefel Mennk, Intd Corporation<br>Combusor:<br>John Anglo, Montor Graphics Corpo-<br>lan Dodd, Montor Graphics Corpora-<br>Soyol Ruo, Caco System<br>Angla Manaros, Italia Corporation<br>Bob Bon, Coranged Comuning Geo | 08                                                                                             | Page 12 IBIS Modeling C:<br>Institute The second seco             |

| From an original by Stephen Peters pa                                                                                                                                                                                                      | iblished 1997                                                                                  | All measurements are made at the output node (md) as shown above. Remove all package land (R. pin, L. pin)<br>and C. pin) paralises. However, any series resistances present between the paul and the pultup/puldoen<br>transitions should be included (these are not hown in Figure 3.1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Copyright © 2005 Government EI                                                                                                                                                                                                             | ectronics and Information Technology Association and The IBIS C<br>Forum. All Rights Reserved. | The stoph buffic is connected to an independent voltage source. The buffic's impution is the decired<br>compartance (inv. high, off) is voltamed, the storing a DC as "startist" multi-visc the decired<br>compartance (inv. high, off) is voltamed, the storing a DC as "startist" multi-visc has detected<br>by perform a "startistic and analysis". The voltage store is this case should be loss more plants in during the<br>operator and startistic and analysis. The voltage store is the start buffict is and predicted by the<br>operator to due to due startistic and analysis. The voltage store is the start buffict be instrumed from the tradit is<br>operator to due due store and the startistic the starts. The control multi-visc the start the start texture<br>and the start texture and texture and the start texture and the start texture and texture |

| IBIS Open Forum                                                                                                                                                                                                                            | IBIS Modeling Cookbook P                                                                       | e 1 current flow into the die pad is positive), as is the voltage at the node with respect to a reference, then the<br>resulting   T and V-T data is combined into a single IV table. Note that tarassient fluction analysis may be a single IV table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

3

3

# IBIS-AMI & COM Co-design for 25G Serdes

# Asian IBIS Summit Taipei, ROC November 4, 2019

Nan Hou, Amy Zhang, Guohua Wang, David Zhang, Anders Ekholm

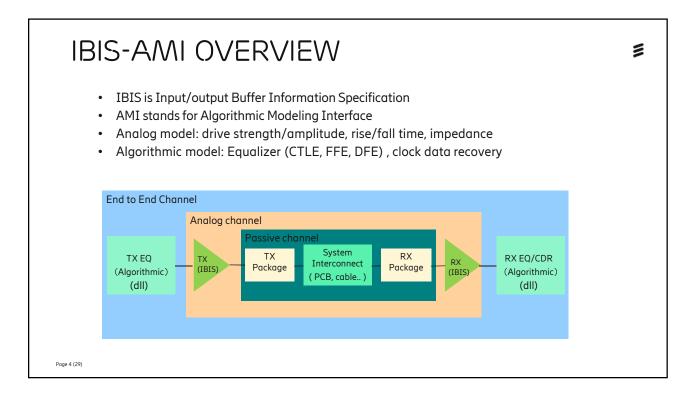

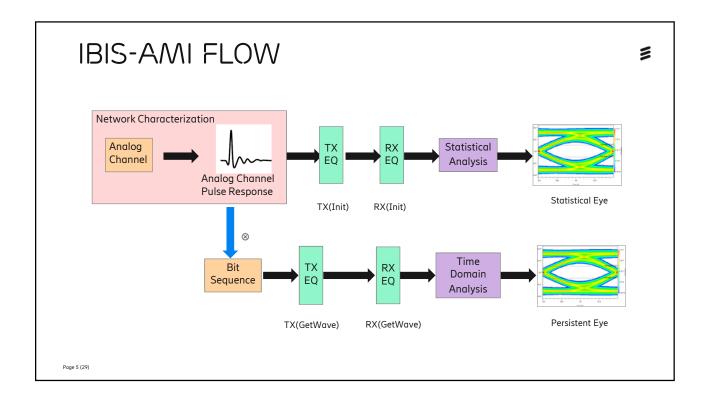

# AGENDA

- Traditional IBIS-AMI

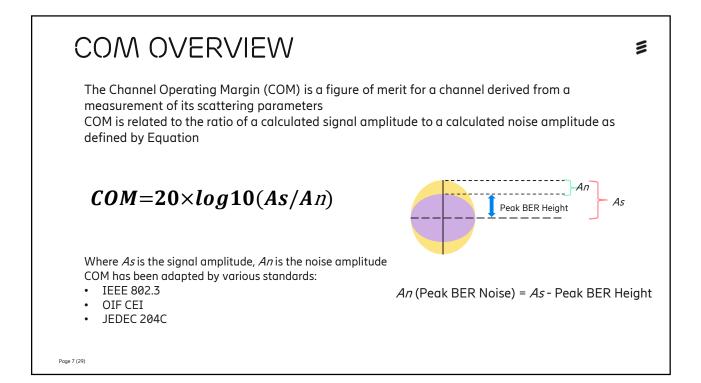

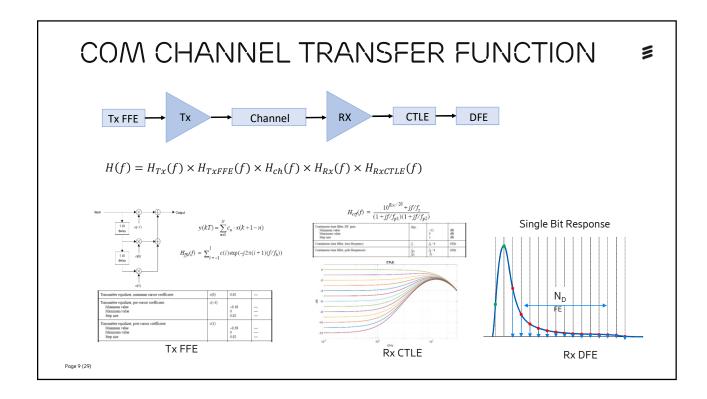

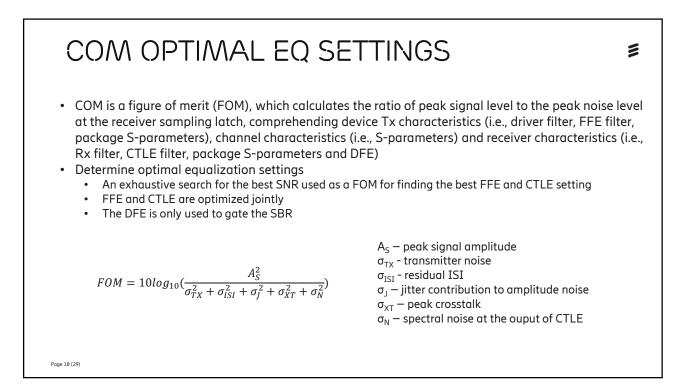

- COM Overview

- IBIS-AMI Co-design with COM for 25G

- Two example channels

- Co-simulation Conclusion

- Next Steps

| Page 2 (29) |

|-------------|

|-------------|

3

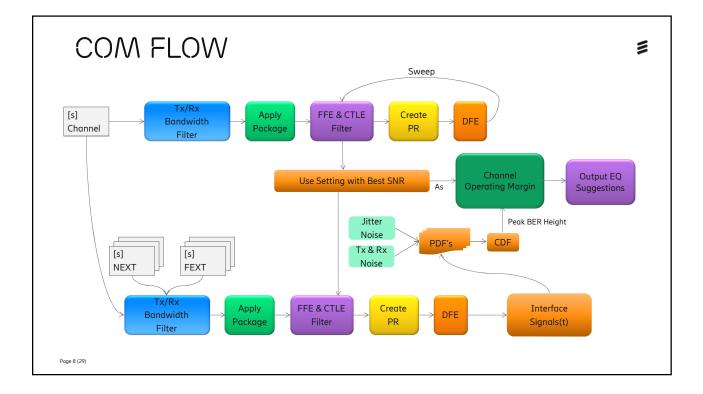

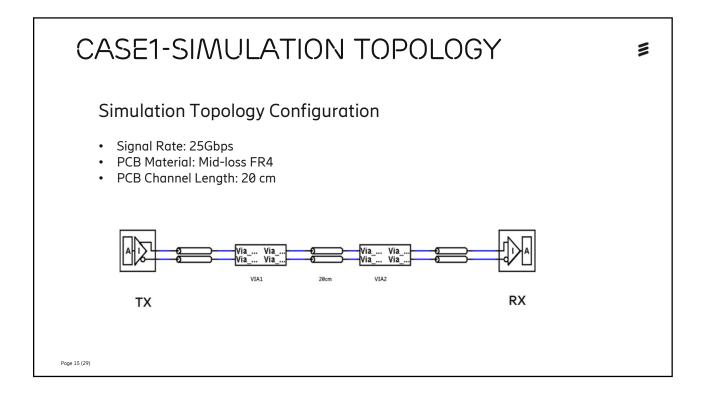

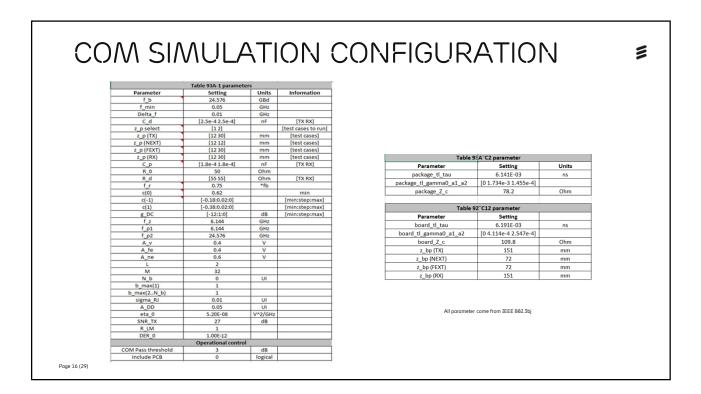

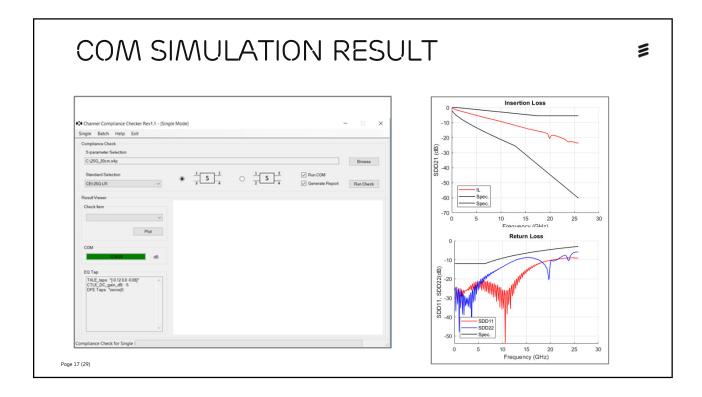

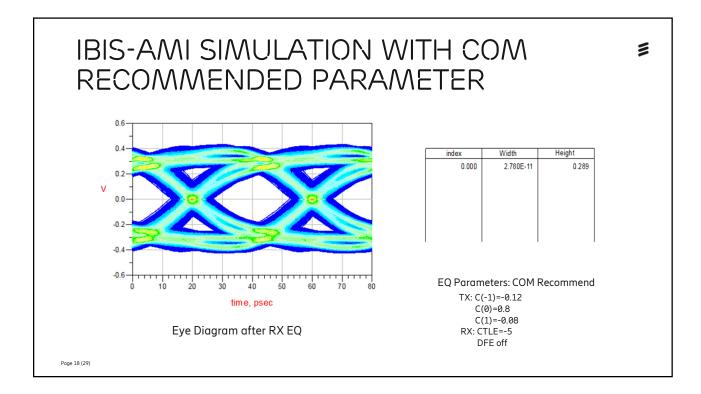

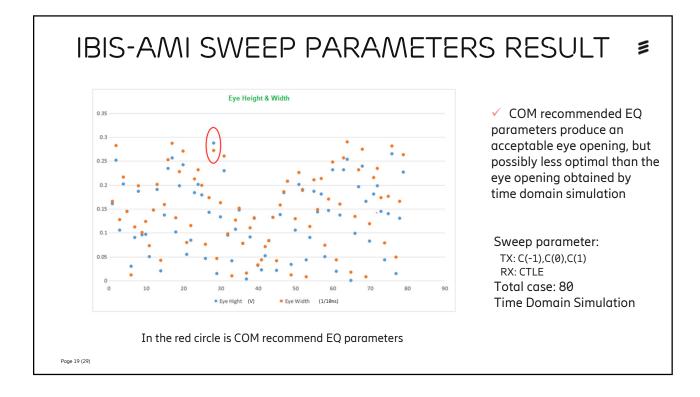

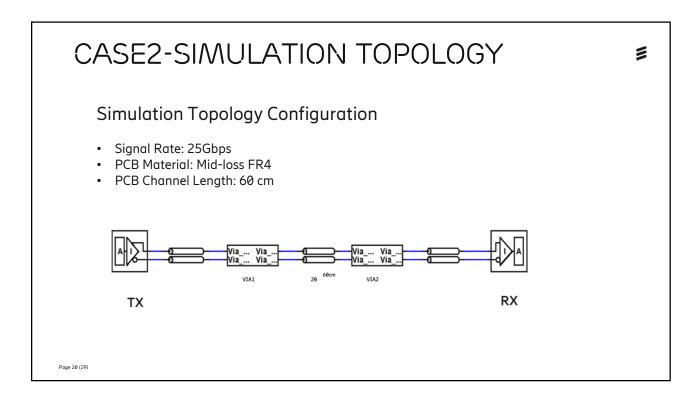

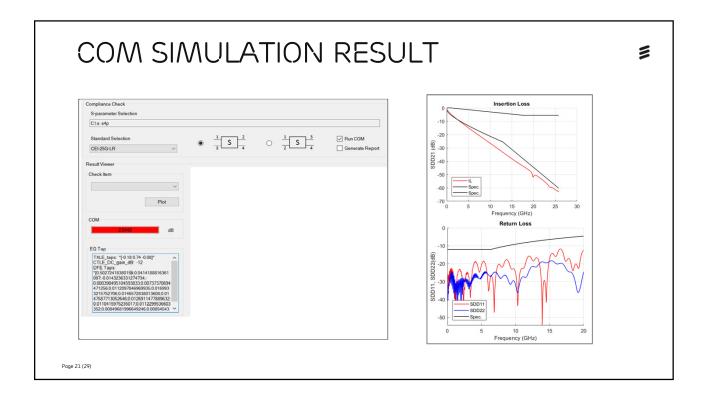

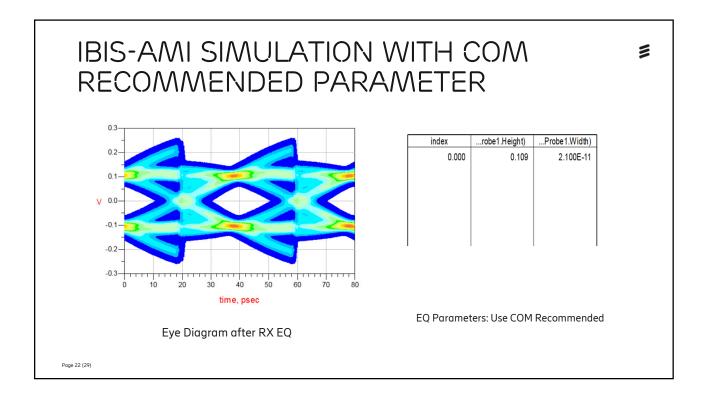

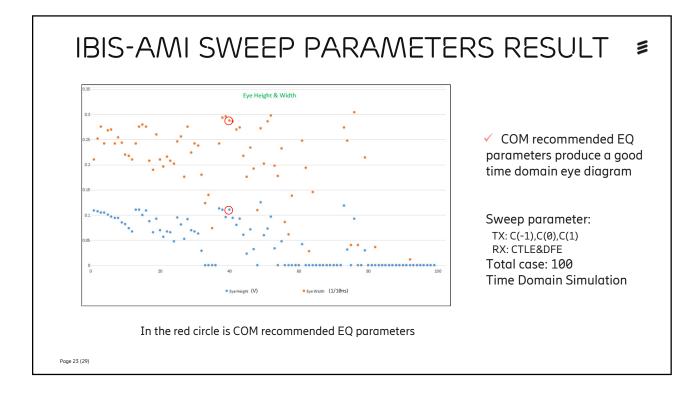

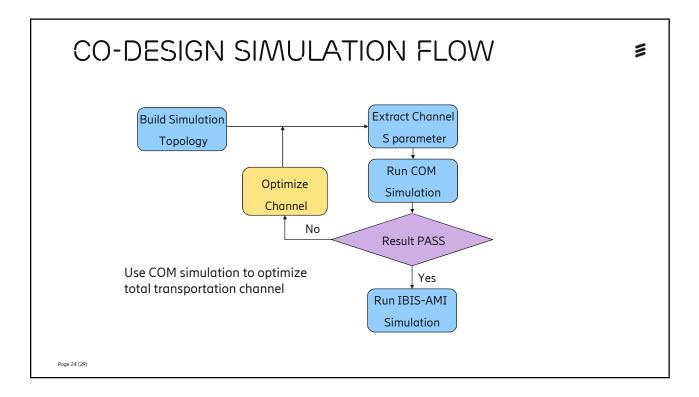

# 25G CO-SIMULATION PROCESS

- Extraction of passive S parameter model of the simulation channel

- Use S parameter to do COM simulation

- IBIS simulation using COM recommended EQ parameter

- IBIS simulation to sweep EQ parameter

- Comparing the eye diagram in time domain

# Page 13 (29)

# AGENDA Traditional IBIS-AMI COM Overview IBIS-AMI Co-design with COM for 25G Two example channels Co-simulation Conclusion Next Steps

## Page 14 (29)

## CO-SIMULATION CONCLUSION

1

- COM enables passive channel evaluation of high-speed signals at early design phase

- COM recommended EQ parameters are suitable for same channel in time domain simulation

- COM simulation is faster, making them more suitable for the post-layout phase of large designs to sweep EQ parameters

Page 26 (29)

## NEXT STEPS Model crosstalk in actual link Co-simulation for 56G PAM-4 Accuracy of IBIS-AMI model Correlation of Co-simulation with measurement

Page 28 (29)

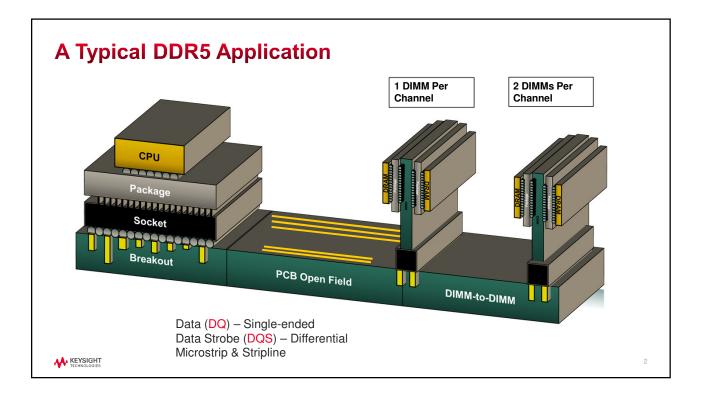

| Signal MT/s  | Generation | Characteristics                                                                                         | Specification                          | Introduction |

|--------------|------------|---------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|

| 4200 - 8000+ |            |                                                                                                         |                                        |              |

|              | DDR5+      | <ul><li>"Hyper Speed"</li><li>Eye collapses</li><li>Impulse response</li><li>BER Rj/Dj, Rn/Dn</li></ul> | Tap Value                              | 2019         |

| 1600 – 4200  | DDR4       | "Serial Speed"         • Eye Diagrams         • Rx Masks         • Bit error rates                      | Rx Mask<br>Veret CAgen mill            | 2014         |

| 200 – 1600   | DDR/2/3    | "High Speed Digital-<br>• Transmission lines<br>• Ts / Th, Skew                                         |                                        | <br>_ 2002   |

| 33 – 133     | SDRAM      | "Low Speed"<br>• Fanout<br>• Capacitance                                                                | V: • • Veut<br>c <u><u><u></u></u></u> | 1961         |

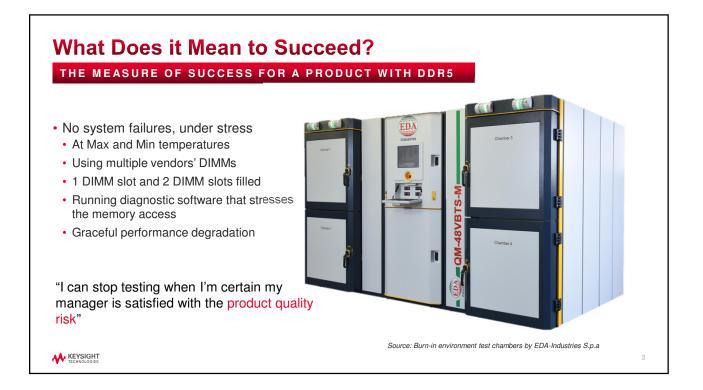

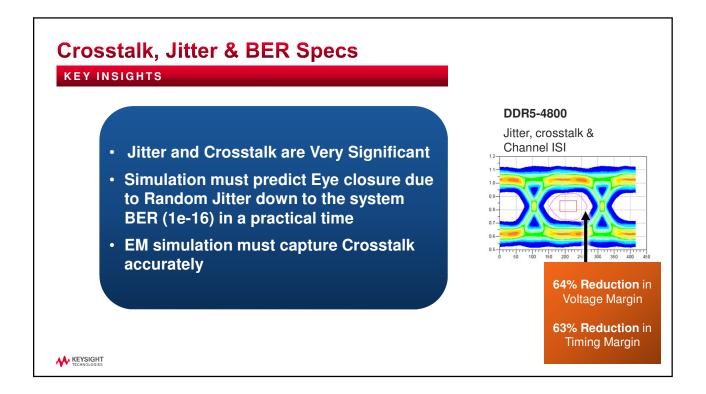

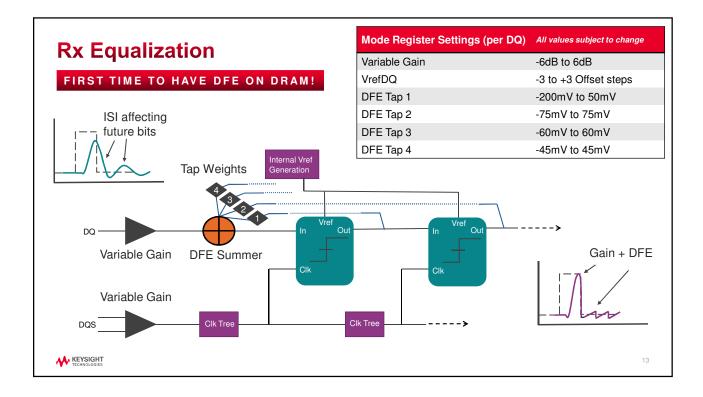

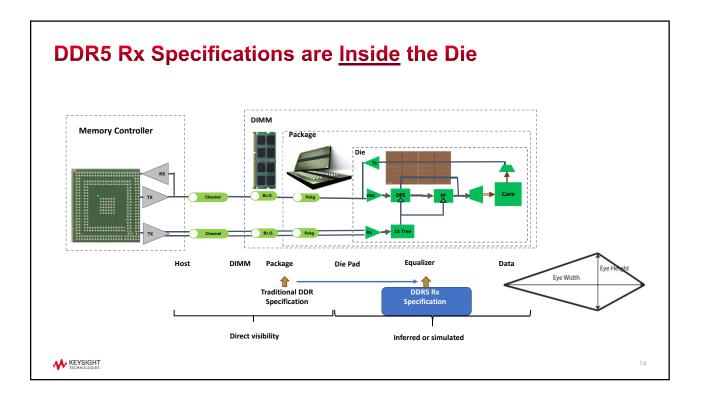

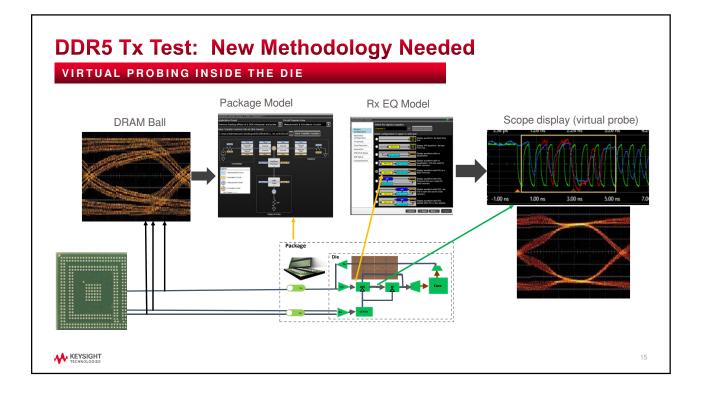

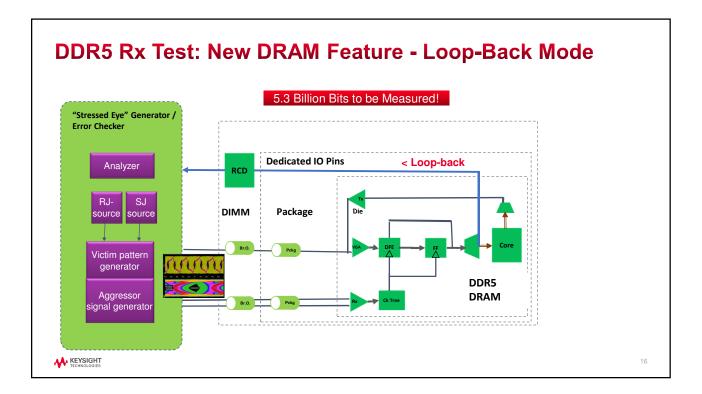

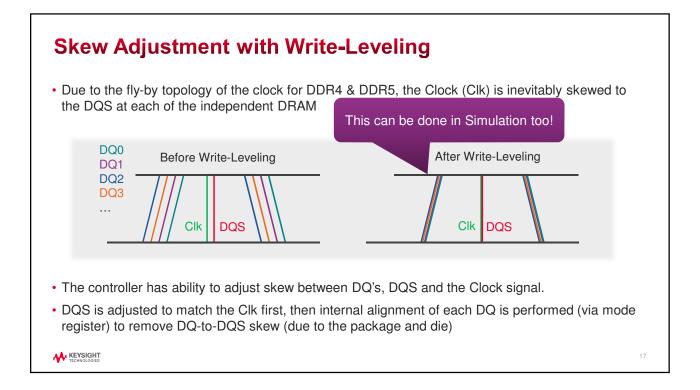

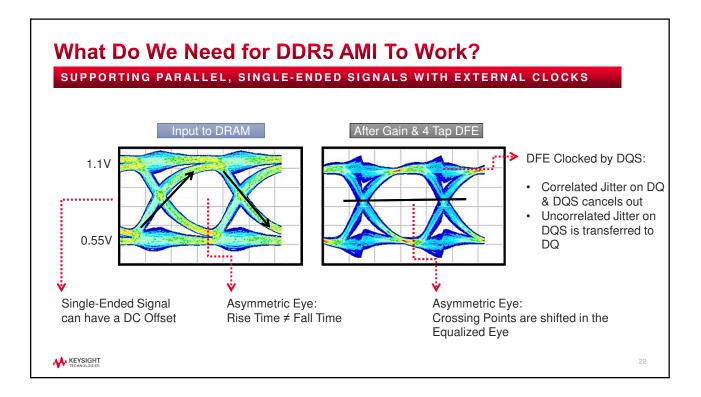

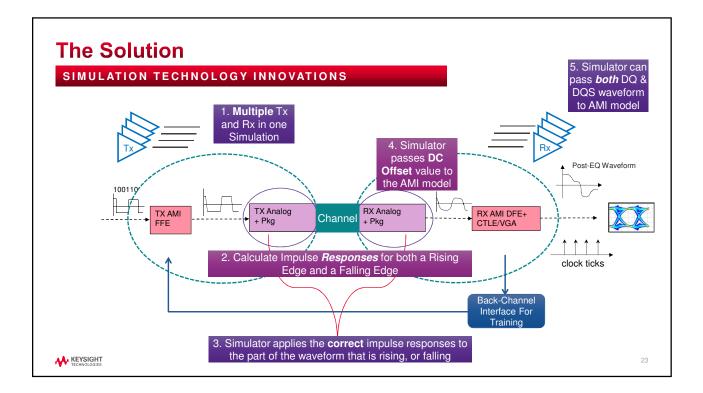

### **Change, Challenges and Solutions**

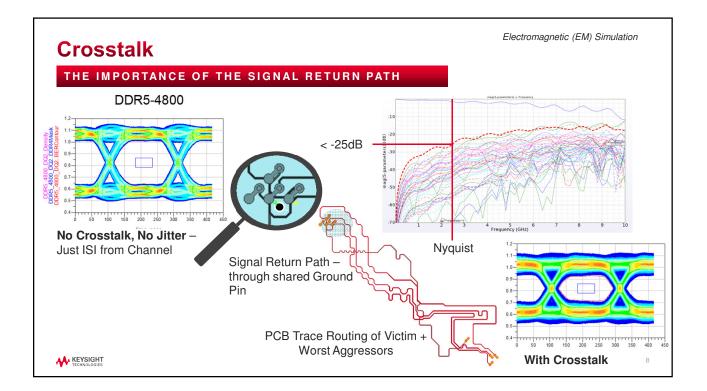

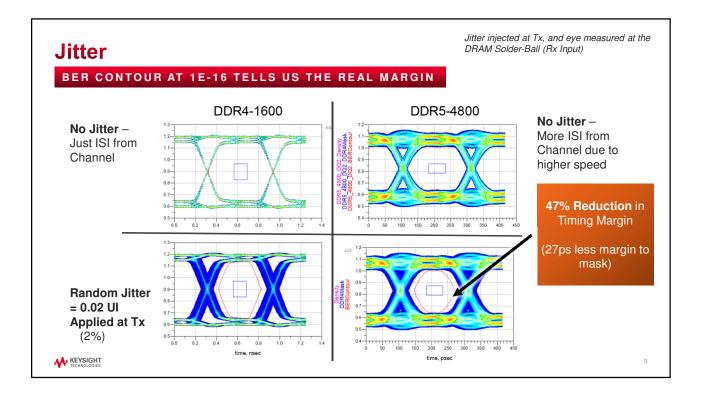

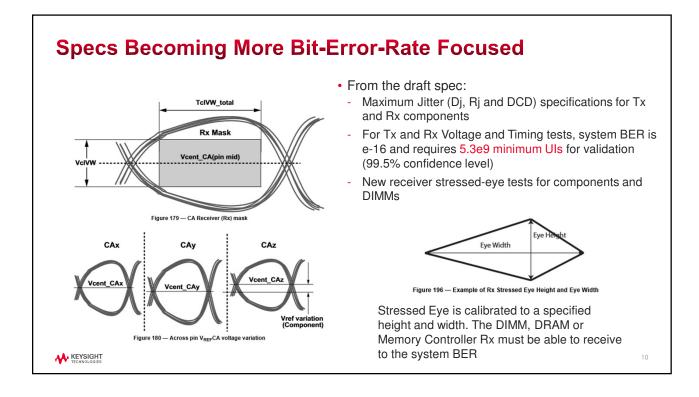

- 1. Crosstalk, Jitter and Bit-Error-Rate (BER) Specs

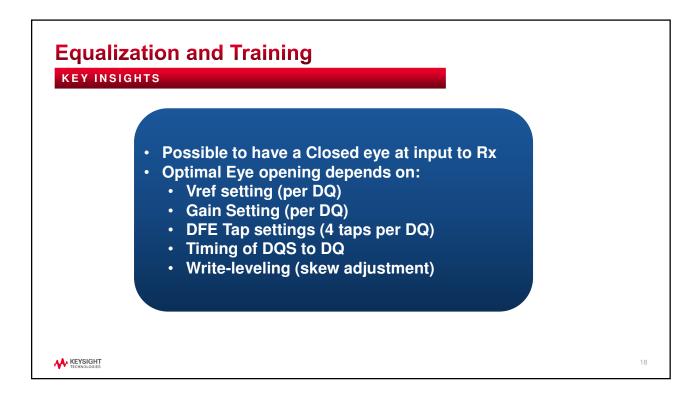

- 2. Closed eyes need equalization and training

- 3. Innovations in Simulation and Modeling of DDR5 & LPDDR5 systems

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

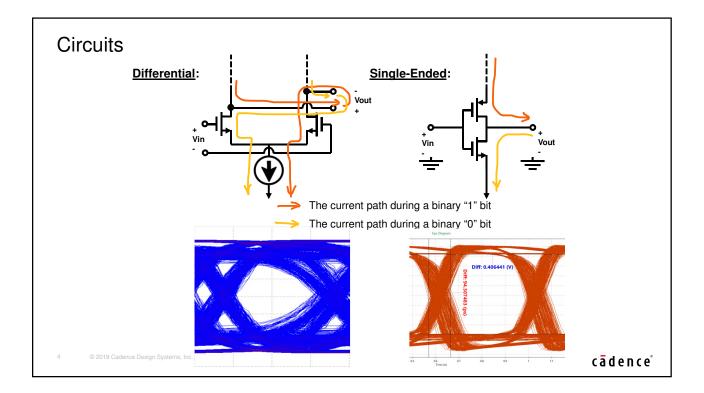

### Two Concerns:

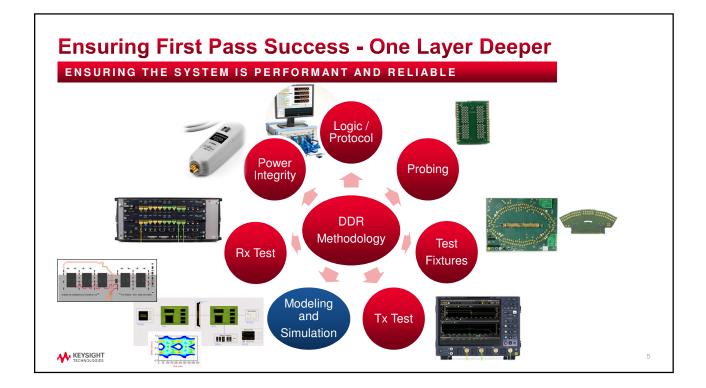

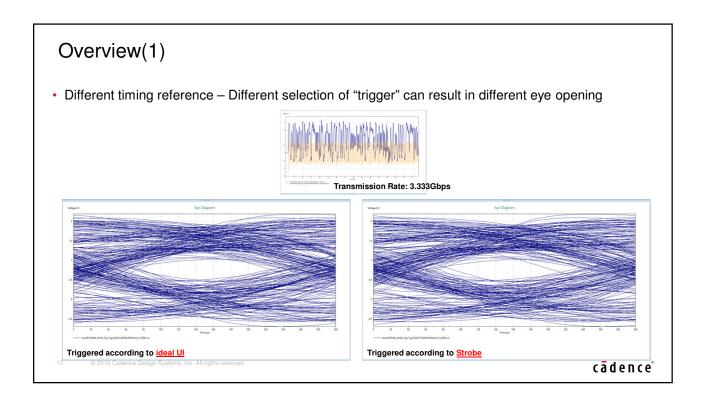

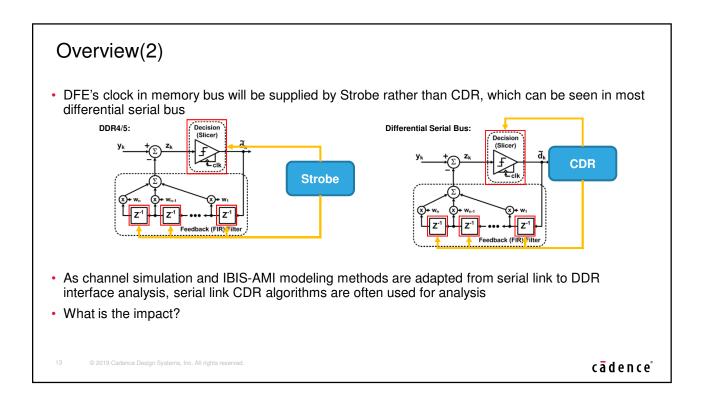

- As the transmission rate of memory bus goes beyond 5Gbps, besides the wellknown timing and overshoot/undershoot analysis, it requires BER prediction analysis and channel analysis

- Two additional concerns we need to face while using channel engine to deal with memory bus:

- Asymmetric rising/falling edges

Different from differential serial buses, single-ended memory buses will have non-symmetrical rising and falling edges due to the inherent difference between these two kinds of circuits

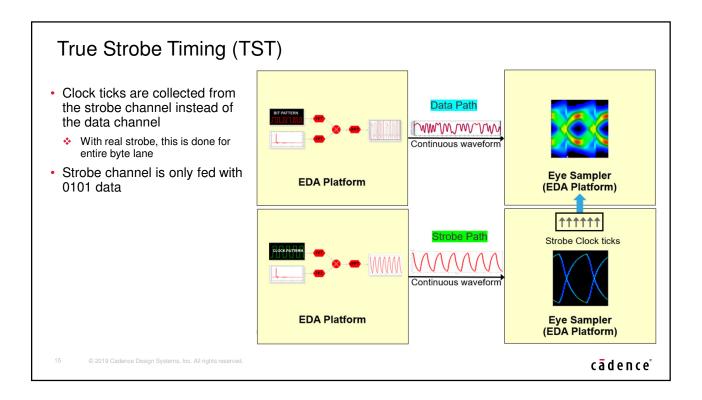

- Strobes as timing reference

While the sampling clock ticks in serial bus are recovered from the signal itself by CDR, the sampling clocks or the timing references in memory bus will be the strobes rather than any recoveries

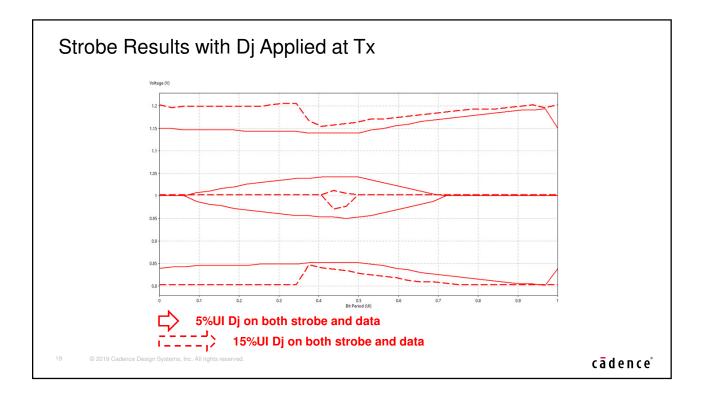

2 © 2019 Cadence Design Systems, Inc. All rights reserved.

cādence°

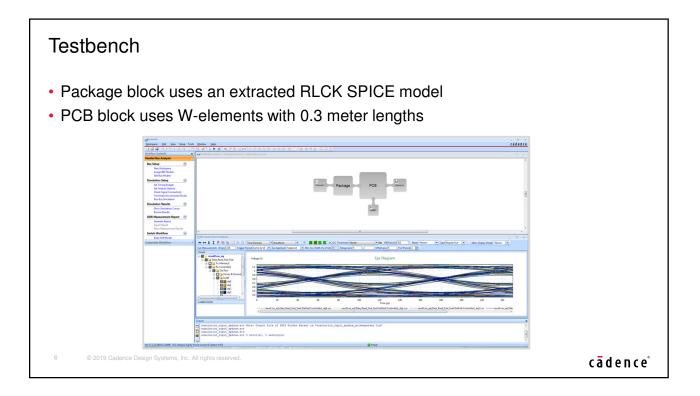

### Overview

- As channel simulation and IBIS-AMI modeling methods are adapted from serial link to DDR interface analysis, we encounter IBIS I/O models with asymmetric rising and falling edges

- This is different from the highly symmetric drivers we typically encounter with serial link analysis

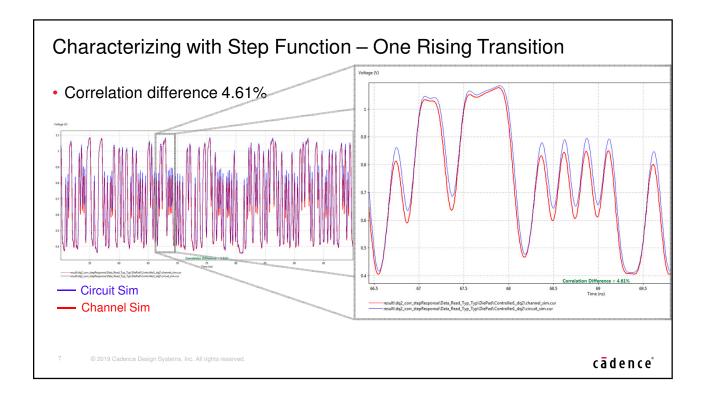

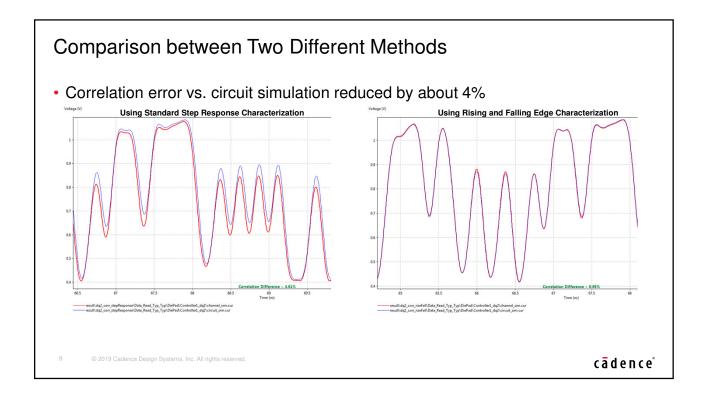

- Traditional single-step response methods for impulse response generation may not reproduce circuit simulation results accurately enough

- These slides show how an EDA tool can handle this (without changes to the IBIS specification)

- All cases use Micron's y11a.ibs file for 8Gbps DDR5

### 5 © 2019 Cadence Design Systems, Inc. All rights reserved.

cādence°

### Summary • The **DQ\_34\_3600** I/O model has some asymmetry in its rising and falling edges Standard SerDes step response characterization did not do a great job in capturing this behavior, as seen in the circuit / channel sim correlation • Characterization methods using rising and falling edges captured this behavior very well for channel simulation \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* [Ramp] R load = 50 typ min max dV/dt r 3.7990E-01/6.4024E-11 3.4860E-01/8.7846E-11 4.0938E-01/4.9359E-11 dV/dt f 4.4605E-01/5.4840E-11 4.2048E-01/7.6564E-11 4.6793E-01/4.2557E-11 cādence

### Summary

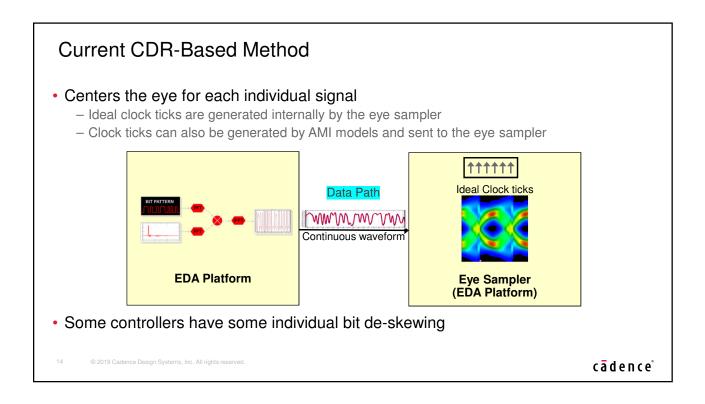

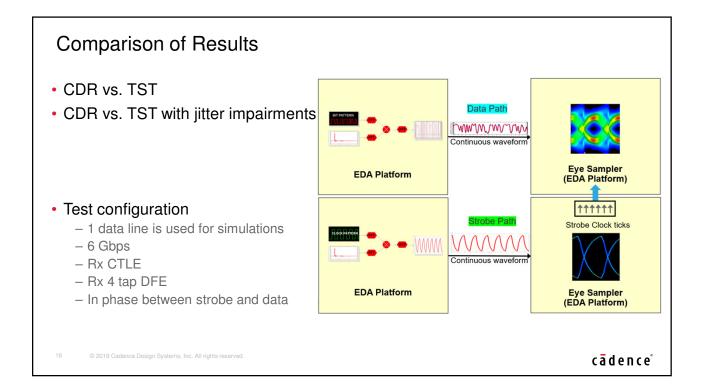

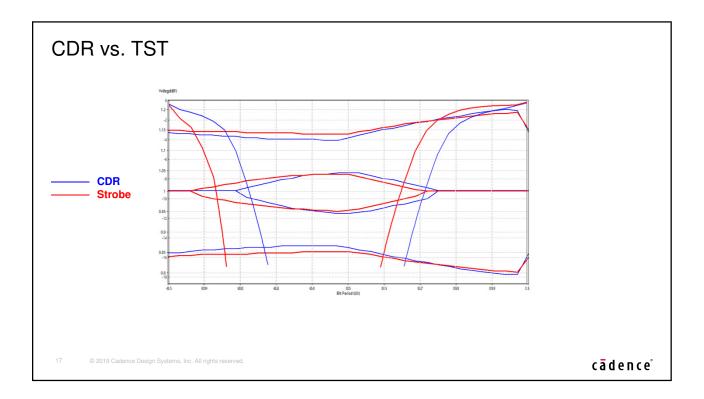

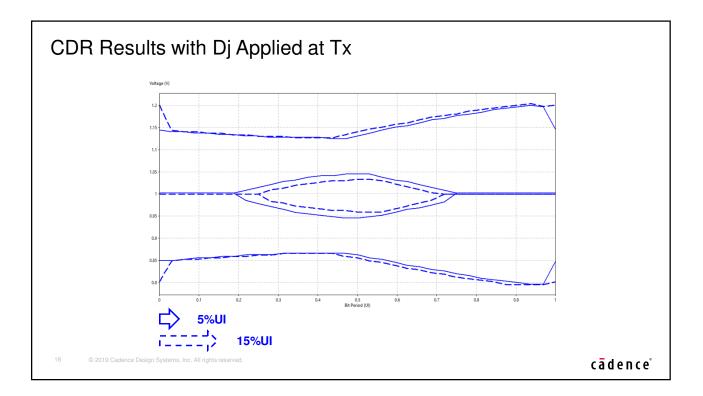

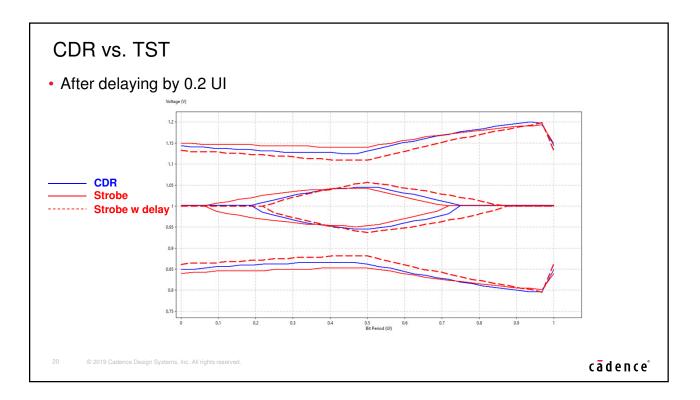

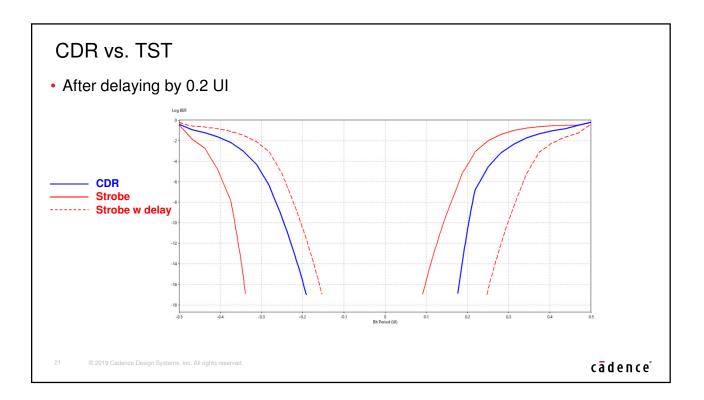

- Using default CDR instead of actual strobe to get clock risks will miss important impairments/jitter for parallel bus topology

- Analysis results show false optimism using CDR approach as compared to true strobe timing methodology

- Need to model delay accurately

22 © 2019 Cadence Design Systems, Inc. All rights reserved.

cādence°

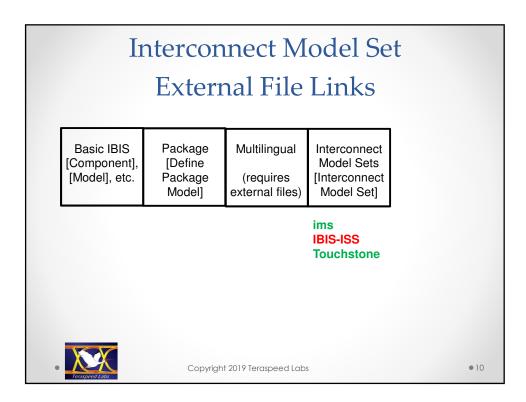

|   |                                             | -                                       | onal Ext<br>age File                         |                                                           |    |

|---|---------------------------------------------|-----------------------------------------|----------------------------------------------|-----------------------------------------------------------|----|

|   | Basic IBIS<br>[Component],<br>[Model], etc. | Package<br>[Define<br>Package<br>Model] | Multilingual<br>(requires<br>external files) | Interconnect<br>Model Sets<br>[Interconnect<br>Model Set] |    |

|   |                                             | pkg                                     |                                              |                                                           |    |

|   |                                             |                                         |                                              |                                                           |    |

| • | Teraspeed Labs                              | Copyrigh                                | † 2019 Teraspeed Labs                        | 5                                                         | •8 |

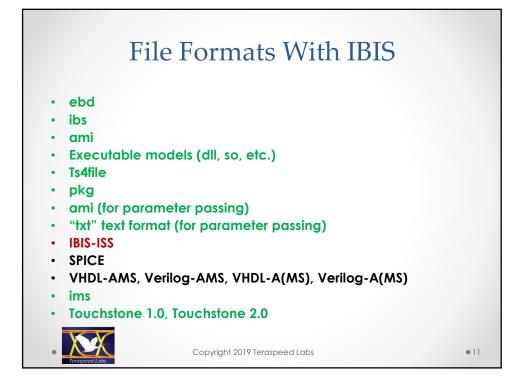

|   | Multi                                                                                                                                                                                                              | lingual                                 | Extern                                       | al File                                                   | Links |  |  |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------|-----------------------------------------------------------|-------|--|--|--|--|

|   | Basic IBIS<br>[Component],<br>[Model], etc.                                                                                                                                                                        | Package<br>[Define<br>Package<br>Model] | Multilingual<br>(requires<br>external files) | Interconnect<br>Model Sets<br>[Interconnect<br>Model Set] |       |  |  |  |  |

|   | ami (for passing parameters)<br>"txt" (text file for passing parameters)<br>IBIS-ISS (can call Touchstone and other file<br>SPICE (Berkeley Version 3F5)<br>VHDL-AMS<br>Verilog-AMS<br>VHDL-A(MS)<br>Verilog-A(MS) |                                         |                                              |                                                           |       |  |  |  |  |

| ۰ | Copyright 2019 Teraspeed Labs                                                                                                                                                                                      |                                         |                                              |                                                           |       |  |  |  |  |