### ZUKEN®

### How to obtain buffer impedance from IBIS

Lance Wang (lance.wang@ibis.org) SOZO Center, Zuken Inc. 2019 IBIS Asian Summit – Taipei November 4th, 2019, Taiwan, R.O.C.

©2019 Zuken

### **Motivation**

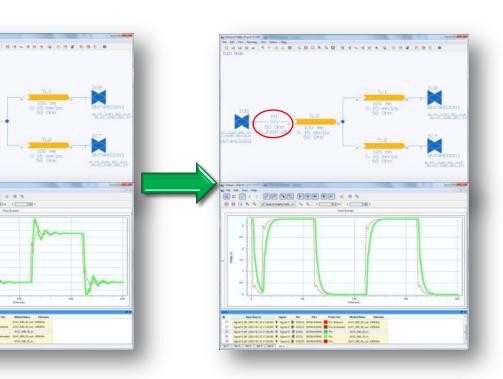

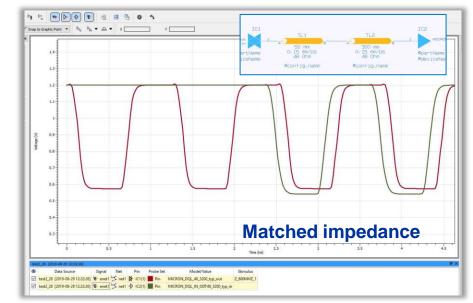

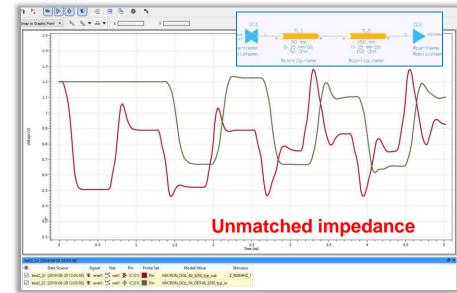

- Impedance matching is the biggest task for Signal Integrity engineer and high-speed PCB/PKG designers.

- Unmatched impedance may cause unpredictable reflection that reduces the signal quality for high-speed circuit design.

- Interconnects, such as, trace, via, connector, package, etc., are under our radar already.

- Field Solver helps

- Interconnect impedance also needs to match buffer Output/Input impedance in order to keep good signal quality How to obtain I/O buffer impedance?

**Impedance Concept**

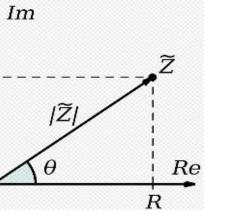

- The impedance of a two-terminal circuit element is represented as a complex quantity Z. The polar form conveniently captures both magnitude and phase characteristics as  $Z = |Z|e^{j arg}$

- where the magnitude |Z| represents the ratio of the voltage difference amplitude to the current amplitude, while the argument arg(Z) (commonly given the symbol  $\theta$  gives the phase difference between voltage and current). *j* is the imaginary unit and is used instead of *i* in this context to avoid confusion with the symbol for electric current

- In Cartesian form, impedance is defined as

- where the real part of impedance is the resistance R and the imaginary part is the reactance X.

For a high-speed I/O buffer, the buffer inductance and capacitance are specially designed. It is close to minimum for the reactance X. So, in this case, the resistance R is the main factor for impedance matching.

X

$$Z = R + jX$$

ZUKEN

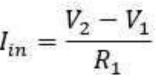

#### Measuring Impedance – Input Impedance

- From the AC impedance triangle, the input or output impedance of a two terminal network can be determined by measuring the small signal AC currents and voltages.

- The voltage is measured across the input terminals and the current measured by inserting the meter in series with the signal generator.

- An easy way to measure small input currents, is to use a fixed resistor, as in the diagram above. Measure the AC voltage at points V1 and V2, then the input current, I<sub>in</sub> becomes:

- The input impedance  $Z_{in}$  of the circuit under test is then found by:

- $Z_{in}=\frac{V_1}{I_{in}}$

Circuit Under Tes

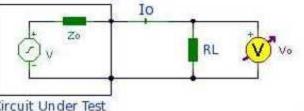

#### Measuring Impedance – Output Impedance

Output impedance may also be determined using a similar technique. A fixed load resistor is used, and the output voltage is measured first with full load, then without the load.

- Z<sub>0</sub> is the internal output impedance of the network to be measured. Circuit Under Test.

- To find the output impedance the output voltage is measured first with no load resistor, then with a fixed load (purely resistive).

- First, the load resistor R<sub>L</sub> is removed and output voltage (V) measured and recorded. Then R<sub>L</sub> is placed back in circuit and the output voltage under load (V<sub>L</sub>). The output impedance, Z<sub>0</sub> is now found by Ohm's Law for AC circuits. As the load is purely resistive Z=V/I, where "V" is voltage drop across the output impedance: (V V<sub>L</sub>), and "I" the output current, V<sub>L</sub>/R<sub>L</sub>. Thus:

$$Z_{0} = \frac{(V - V_{L})}{V_{L}/R_{L}} = \frac{R_{L}(V - V_{L})}{V_{L}}$$

### **IBIS model contents**

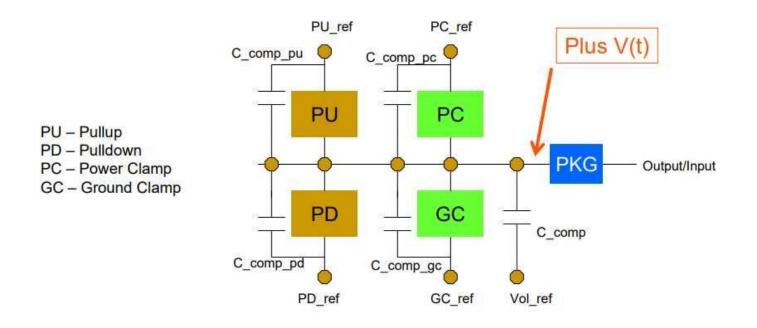

### **IBIS Buffer Structure**

#### All curve data are independent with own voltage references

- I/O type

- 4 static curve data sets

- Pullup

- Pulldown

- Power Clamp

- Ground Clamp

- Output type

- 2 static curve data sets

- Pullup

- Pulldown

- Input type

- 2 static curve data sets

- Power Clamp

- Ground Clamp

### **IBIS model contents**

#### **IBIS model contents**

### ZUKEN®

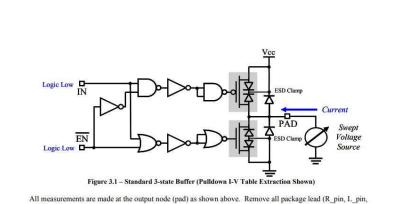

#### 3.1 Extracting I-V Data from Simulations

The first step to extracting the required I-V tables is understanding the buffer's operation. Analyze the buffer schematic and determine how to put the buffer's output into a logic low, logic high and (if applicable) high impedance (3-state) state. As mentioned above, the schematic should include any ESD or protection diodes. Also, understand the buffer's power supply voltage reference ("Vcc") requirements and connections. The schematic should also indicate if the power clamp and/or ground clamp diode structures are tied to voltage rails (voltage references) different from those used by the pullup and/or pulldown transistors.

#### 3.1.1 Simulation Setup

Page 12

A typical I-V table simulation setup for an output or I/O buffer is shown in Figure 3.1 below. For this example, the buffer being analyzed is a standard 3-state buffer with a single push-pull output stage. The buffer uses electrostatic discharge protection devices in addition to its parasitic driver diodes. The buffer's clamp supplies are assumed identical to its driver supply (Vcc hereinafter).

**IBIS Modeling Co**

An measurements are made at the output node (pao) as snown above. Kentove an package read (K\_Din, L\_Din and C\_Din) parasitics. However, any series resistances present between the pad and the pullup/pulldown transistors should be included (these are not shown in Figure 3.1).

The output buffer is connected to an independent voltage source. Set the buffer's input(s) so that the desired output state (low, high, off) is obtained, then using a DC or "transfer function" analysis sweep the voltage source over the sweep range -Vec to 2<sup>9</sup>Vec while recording the current into the buffer. An alternative method is to perform a "transient analysis". The voltage source in this case should be linear ramp function driving the output node, slow enough that the current measurement at each time point is effectively DC, without reactive aspects of the design affecting the result. The current flow into the pad is measured (by IBIS convention, current flow into the die pad is positive), as is the voltage at the node with respect to a reference, then the resulting I-T and V-T data is combined into a single I-V table. Note that a transient function analysis may require post-simulation data manipulation.

#### **Obtain impedance from IBIS curves**

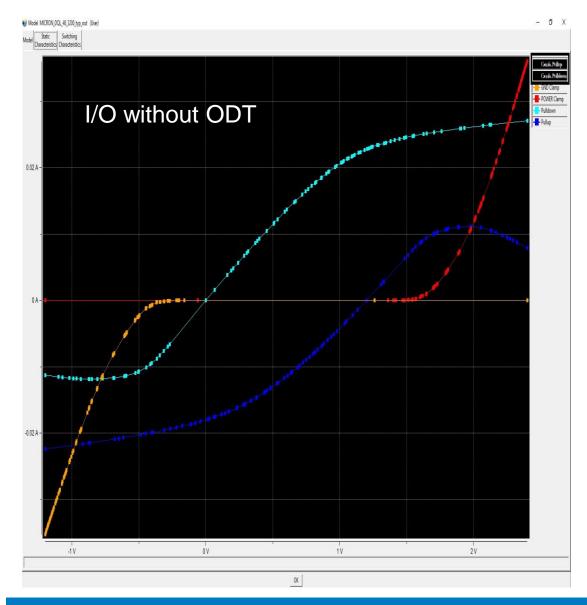

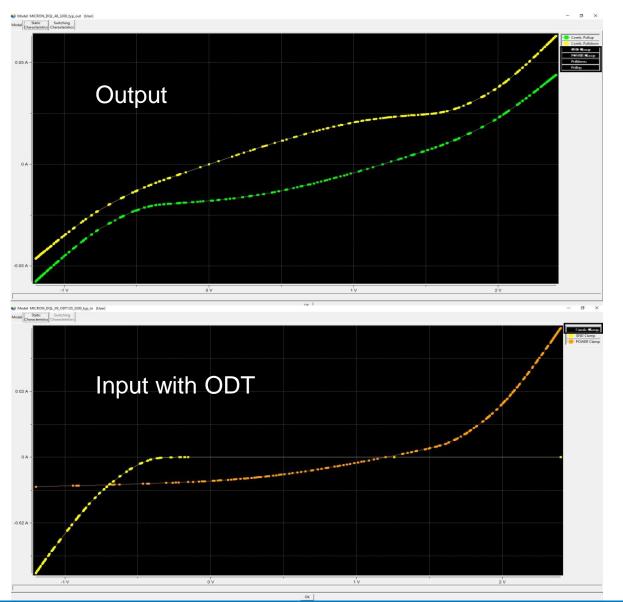

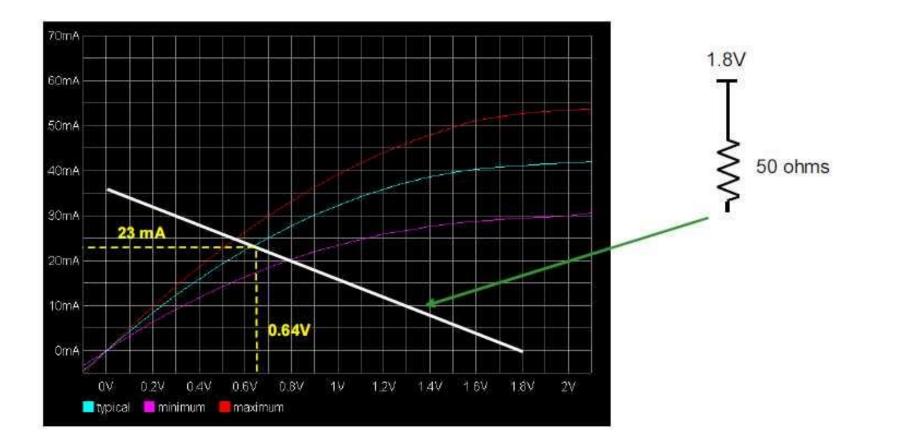

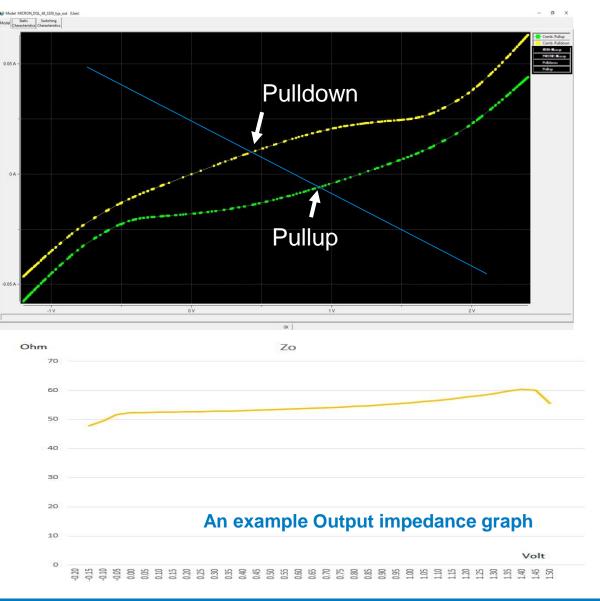

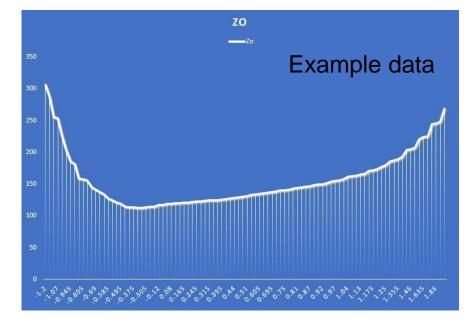

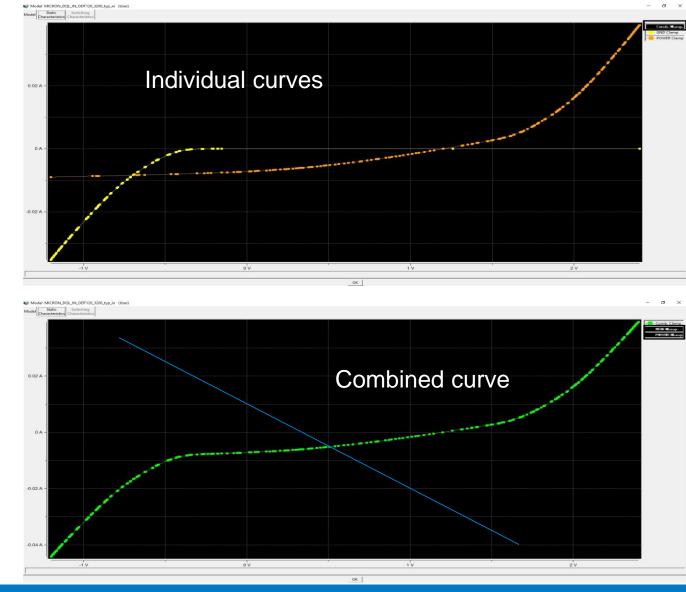

### **Obtain Output type buffer impedance from IBIS**

- Need to use Combined Pullup/Pulldown curves

- Pullup + Clamps

- Pulldown + Clamps

- Load line / Crossing Point

- To avoid numerical errors

$$Z_0 = \frac{dV}{dI} @ R_L$$

### **Obtain Input type buffer impedance from IBIS**

- Use the Combined Clamp data

- To avoid numerical errors

$Z_0 = \frac{dV}{dI} @ R_L$

#### **Conclusion**

- Impedance matching is important for highspeed design

- Not only for interconnect impedance, but also

I/O buffer impedance should be counted in the big picture

- The I/O buffer impedance can be obtained from IBIS curve data

- Obtain buffer driving impedance from IBIS combined Pullup/Pulldown curve data

- Obtain buffer Input impedance from IBIS combined Power /Ground Clamps curve data

- I/O impedance maybe vary for different loads