# Improving Power Supply Induced Jitter Simulation Accuracy for IBIS Model

Yin Sun, Chulsoon Hwang

*EMC Laboratory Missouri University of Science and Technology*

> Virtual IBIS Summit (China) November 20, 2020 (Previously given on August 28, 2020)

#### Outline

- Introduction of Power Supply Induced Jitter (PSIJ)

- Limitations of Current Power-Aware IBIS Model

- New Behavior Model Proposal

- Model Validation

- Conclusions

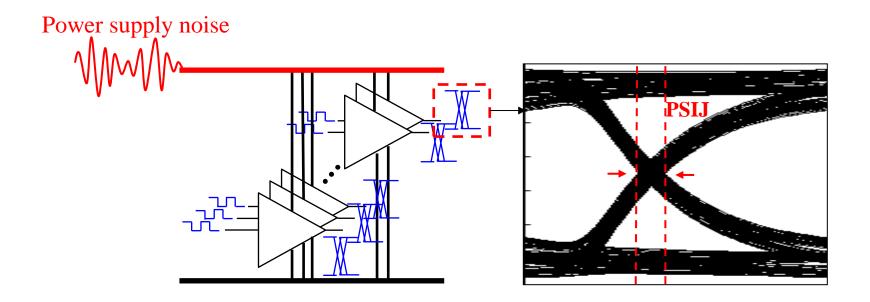

# Power Supply Induced Jitter (PSIJ)

Power supply induced jitter

• The time variation in the output transition edges from ideal positions due to the voltage fluctuations on power rail.

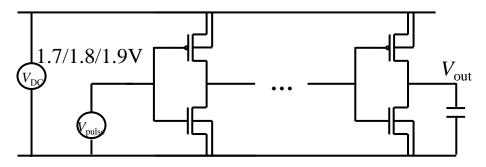

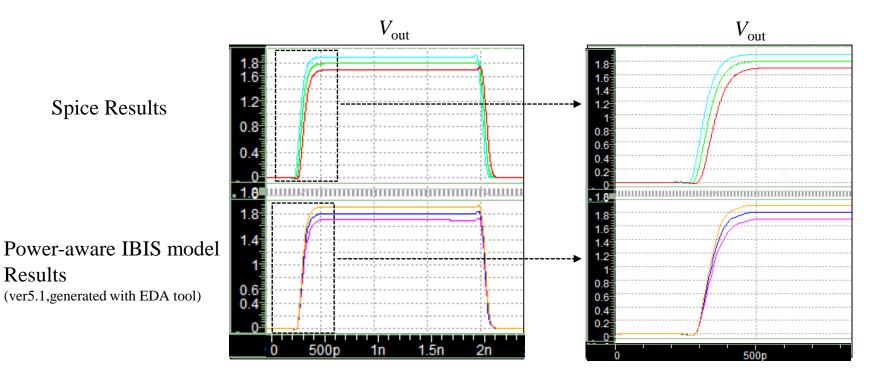

#### Limitations of Current Power-Aware IBIS Model

- <u>**Cannot**</u> account for the delay change caused by power noise correctly.

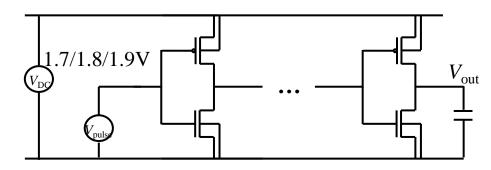

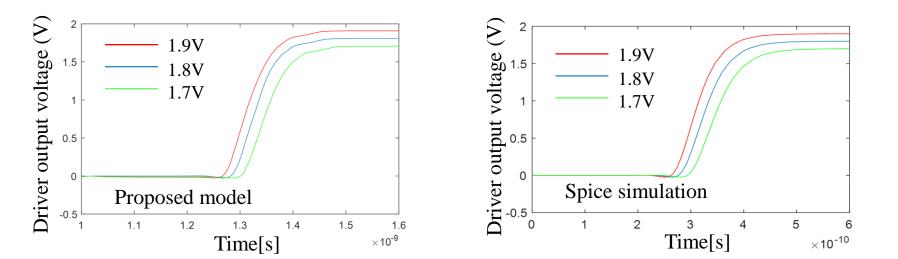

- Example: an inverter chain output, change power voltage to 1.7/1.8/1.9V, respectively

#### Limitations of Current Power-Aware IBIS Model

• Power-aware IBIS model considers gate modulation effect, ratio modification on Ku, Kd based on power rail voltage value

#### Gate Modulation Coefficients

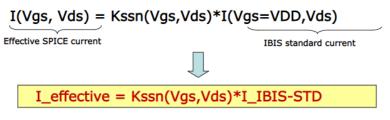

The ST "Gate Modulation" solution is based on the introduction of two coefficients, one for the Pullup and one for the Pulldown stage, which modulate properly the IBIS standard current (I\_IBIS-STD) when a bouncing noise occurs on the power and ground nodes

$$K_{d}(t)I_{pd} \rightarrow K_{sspd}(V_{pd})K_{d}(t)I_{pd}$$

$$K_{u}(t)I_{pu} \rightarrow K_{sspu}(V_{pu})K_{u}(t)I_{pu}$$

$$K_{sspd} \left( V_{pd} \right) = \frac{V_{pd}}{I_{sspd} \left( 0 \right)}$$

$$K_{sspu} \left( V_{pu} \right) = \frac{V_{pu}}{I_{sspu} \left( 0 \right)}$$

Source: "BIRD 98 and ST 'Gate Modulation' Convergence", IBIS Open Forum Teleconference, Jan. 27<sup>th</sup>, 2007

The ratio modification Ksspd, Ksspu on Ku, Kd is only a function of  $V_{pd}$  or  $V_{pu}$ , it cannot reflect the effect of power rail voltage noise on switching edge timing change

## New Behavior Model Proposal

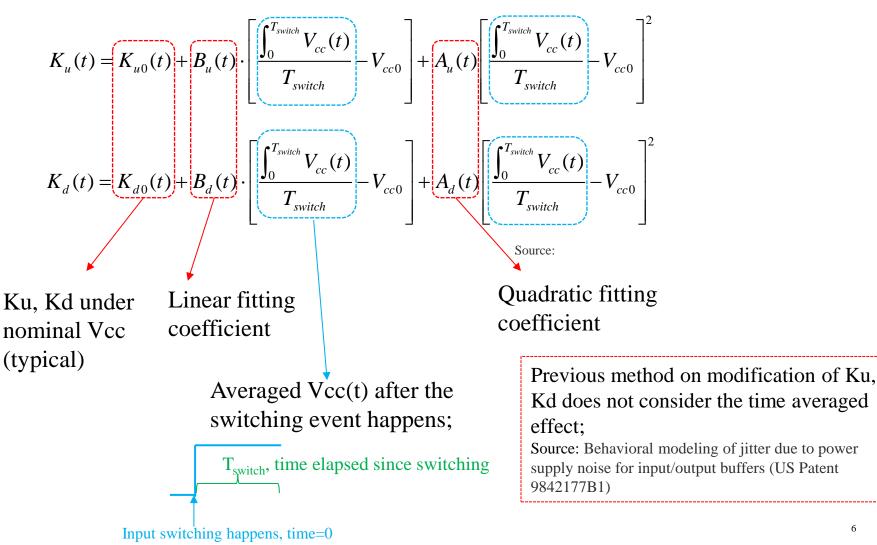

Modify Ku(t), Kd(t) as a function of <u>time averaged</u> power rail voltage Vcc(t); introduce correction coefficient B and A as a function of <u>time</u>

#### New Behavior Model Proposal

• How the modified Ku(t), Kd(t) account for Vcc(t) caused delay change

1. At each time point, use Ku, Kd under three cases => B(t), A(t);

2. B(t), A(t) can account for the delay change due to Vcc(t) noise;

3. The total effect of Vcc(t) during the time range of propagation delay is considered by the time-averaged Vcc(t)

#### New Behavior Model Proposal

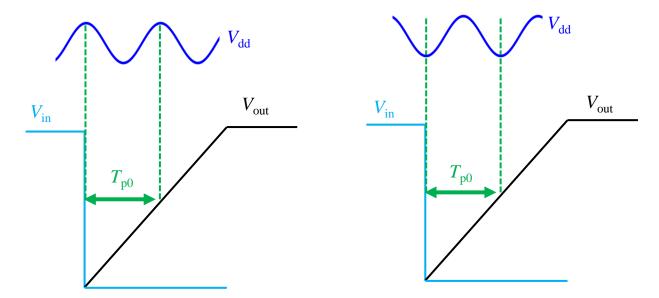

• Why consider **<u>time averaged</u>** power rail voltage effect

Propagation delay will be the same for the two cases

1. The Vcc noise can take effect during the propagation delay time range;

2. The influence is accumulated, just consider instantaneous voltage value is not accurate.

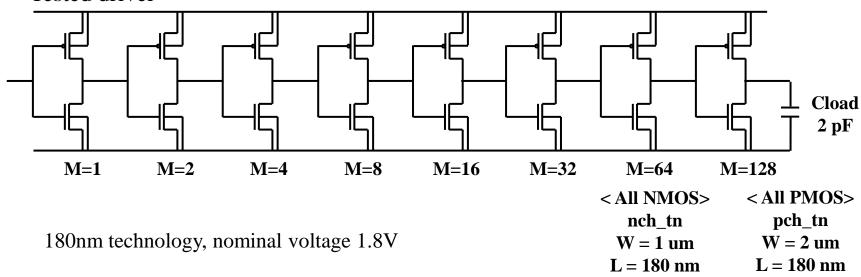

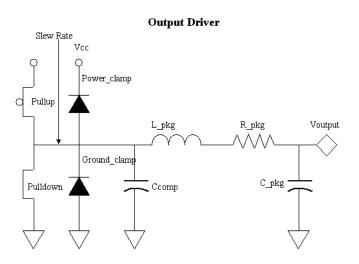

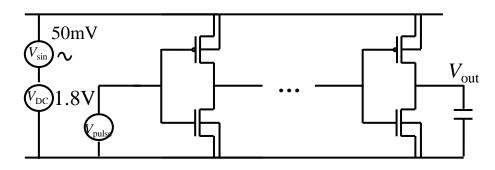

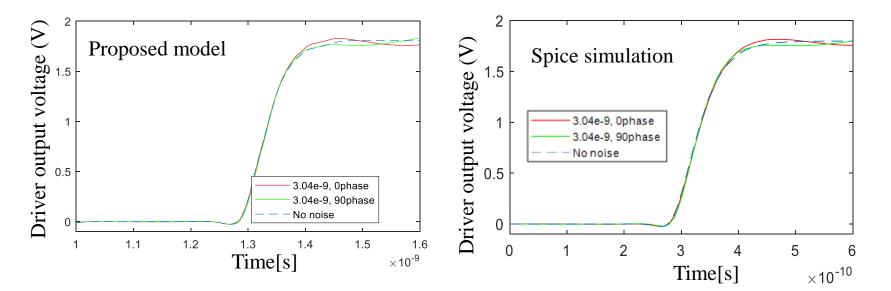

• Tested driver

• Corresponding IBIS model (output)

In this case, there is no power\_clamp and ground\_clamp; C\_comp is extracted as 0.46pF;

The Ku, Kd is implemented with the new method.

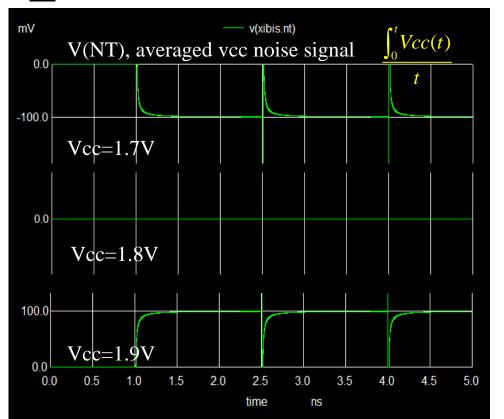

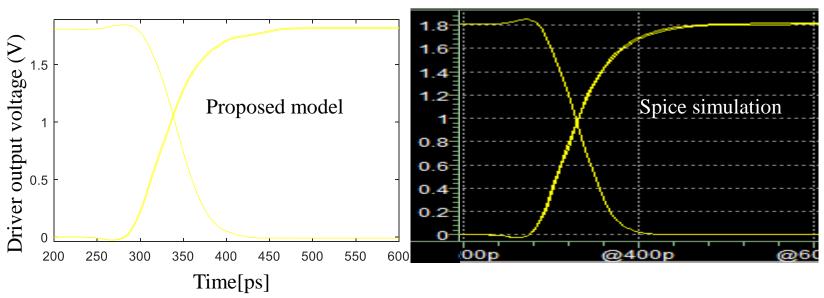

#### 1. Vcc 1.7/1.8/1.9V respectively

2. Vcc have very low frequency noise

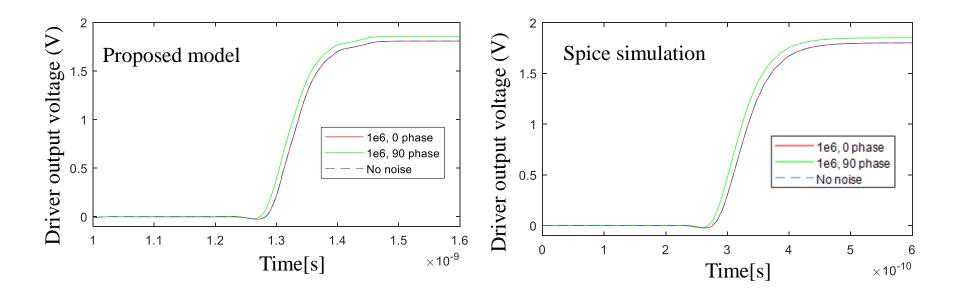

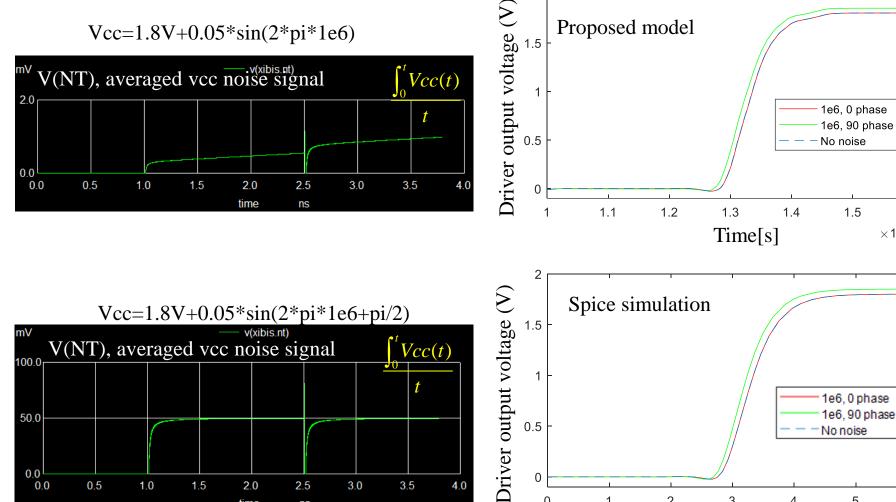

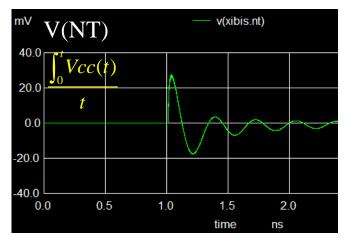

Vcc=1.8V+0.05\*sin(2\*pi\*1e6) Vcc=1.8V+0.05\*sin(2\*pi\*1e6+pi/2)

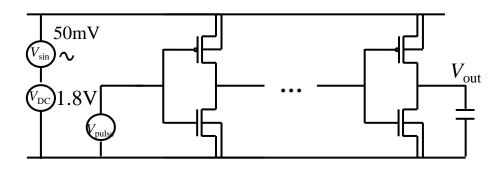

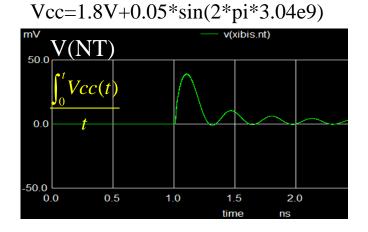

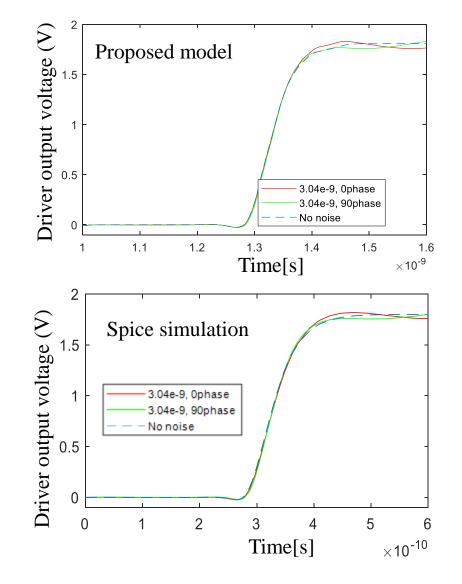

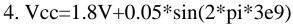

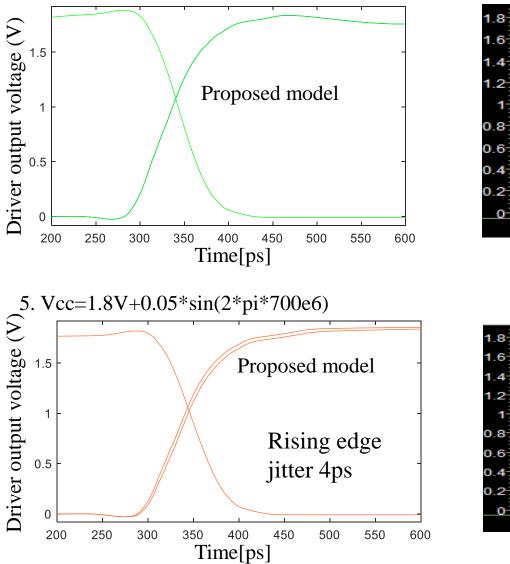

3. Vcc have noise with frequency corresponds to propagation delay (329ps)

Vcc=1.8V+0.05\*sin(2\*pi\*3.04e9)

Vcc=1.8V+0.05\*sin(2\*pi\*3.04e9+pi/2)

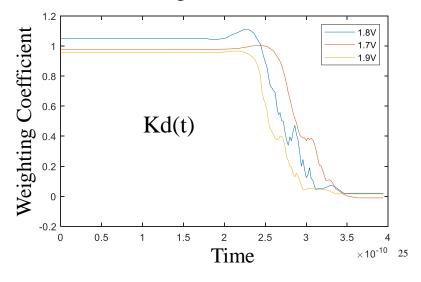

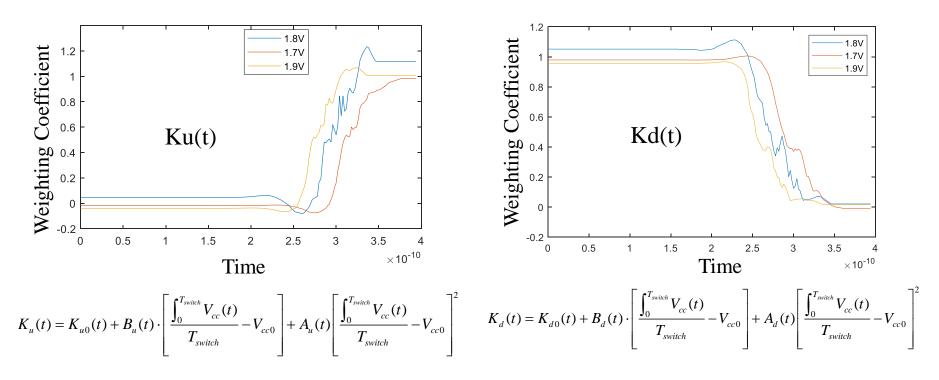

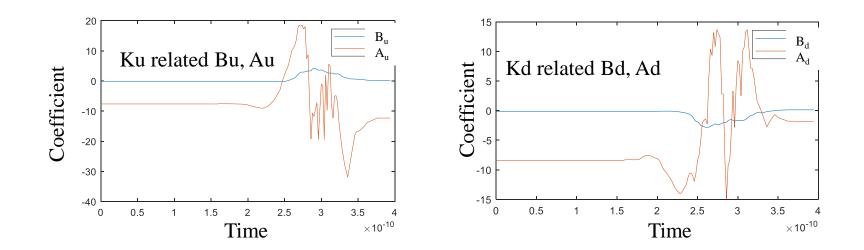

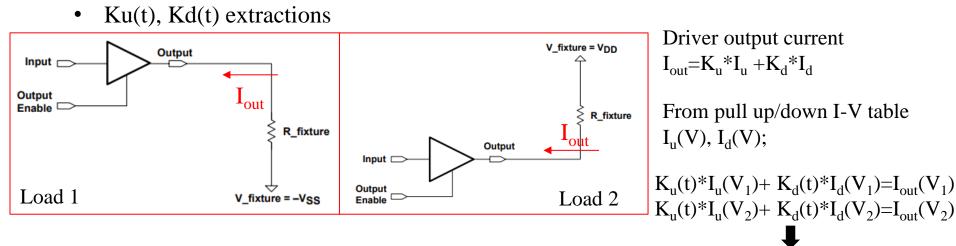

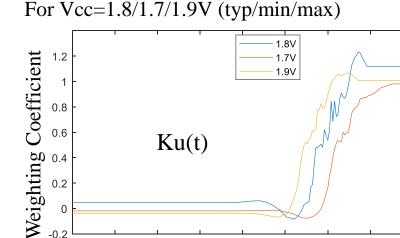

- Extraction of Bu(t), Au(t), Bd(t) and Ad(t) from Ku(t), Kd(t) under different Vcc

- 1.Extraction of Ku (t) and Kd (t) for three voltage cases

- 2. Bu(t), Au(t), Bd(t), Ad(t) extractions

$$K_{u}(V_{cc\_max},t) = K_{u}(V_{cc0},t) + B_{u}(t)*(V_{cc\_max}-V_{cc0}) + A_{u}(t)*(V_{cc\_max}-V_{cc0})^{2}$$

$$K_{u}(V_{cc\_min},t) = K_{u}(V_{cc0},t) + B_{u}(t)*(V_{cc\_min}-V_{cc0}) + A_{u}(t)*(V_{cc\_min}-V_{cc0})^{2}$$

$$2 \text{ equations, } 2 \text{ unknowns}$$

$$algorithm => Bu(t), Au(t)$$

$$V_{cc_max}$$

1.9V; $V_{cc_min}$ 1.7V; $V_{cc0}$ 1.8VBd(t), Ad(t) can be obtained similarly

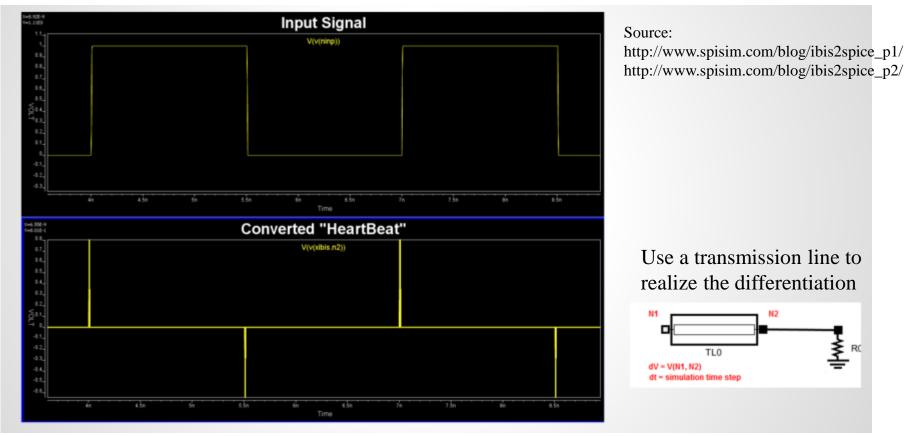

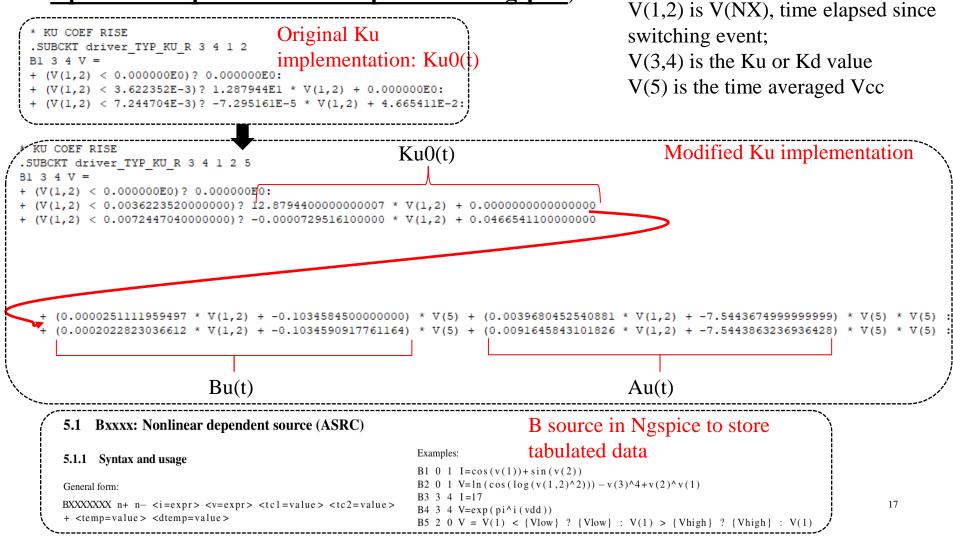

- Implementation in Ngspice (Modify based on current ibis2spice algorithm)

- 1. Ku, Kd, Bu, Au, Bd, Ad calculated offline from rising/falling waveforms

- 2. From input switching edge dv/dt, judging rising or falling

- Implementation in Ngspice (Modify based on current ibis2spice algorithm)

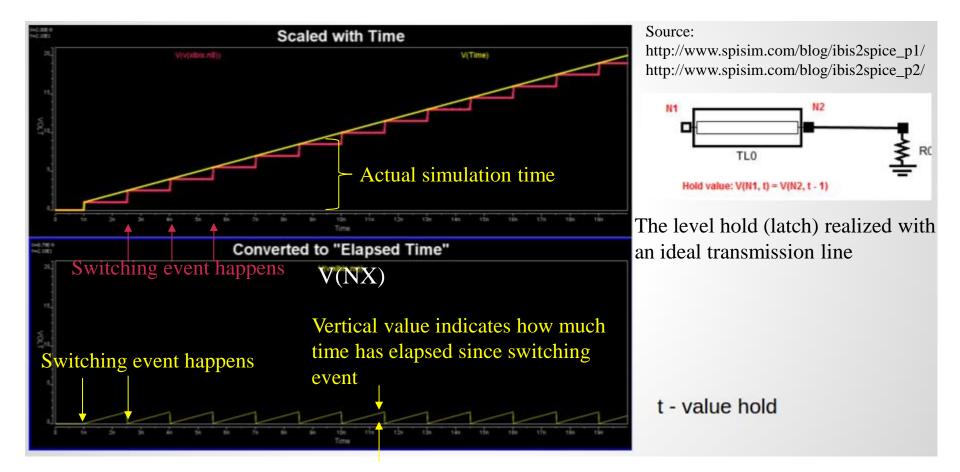

- 3. Record elapsed time since every switching event

- Implementation in Ngspice (Modify based on current ibis2spice algorithm)

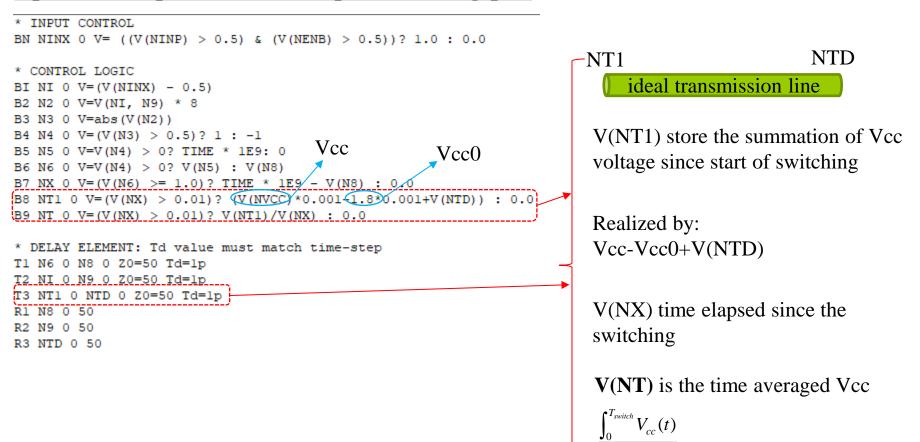

- 4. Implement the time averaged Vcc (<u>Improved algorithm in this work,</u> <u>a practical implementation in open-source Ngspice</u>)

Implementation in Ngspice (Modify based on current ibis2spice algorithm)

5. Implement the modified Ku, Kd as B source (Improved algorithm in this work, a practical implementation in open-source Ngspice)

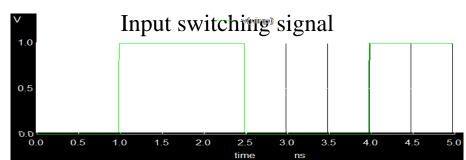

#### Simulation Results of Implemented Time-Averaged Vcc[V(NT)]

#### 1. Vcc 1.7/1.8/1.9V respectively

## Simulation Results of Implemented Time-Averaged Vcc[V(NT)]

2

0

0

1

2

3

Time[s]

Proposed model

2. Vcc have very low frequency noise

0.0

0.0

0.5

1.0

1.5

2.0

time

2.5

ns

Vcc=1.8V+0.05\*sin(2\*pi\*1e6)

3.5

3.0

$imes 10^{-10}$

6

5

4

1.6

$imes 10^{-9}$

#### Simulation Results of Implemented Time-Averaged Vcc[V(NT)]

3. Vcc have noise with frequency corresponds to propagation delay (329ps)

20

#### Conclusions

- The ability to correctly account for the power supply induced jitter has been improved

- This work has extended the current IBIS model to include the delay change effect caused by the power rail noise

- The Ku, Kd are modified as a function of Vcc

- The time averaged effect of Vcc has been considered

- A plausible algorithm has been provided and implemented in Ngspice

- This method is suitable for small power noise situation

## Back-Up, Partial Eye Diagram

For the current implementation, the Ngspice can only run for a short period of time (possibly due to the not perfect implementation of the algorithm as spice sub-circuit);

Usually, 2 rising edges and 1 falling edge can be obtained with the improved IBIS model

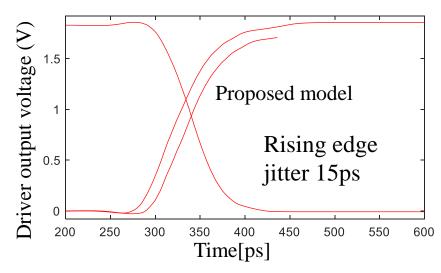

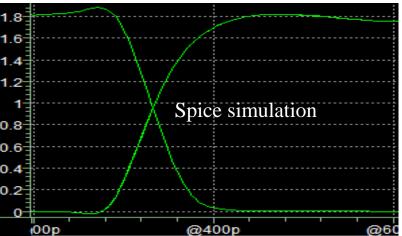

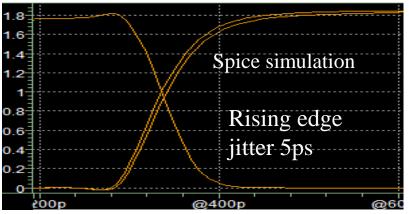

1. Vcc=1.8V+0.05\*sin(2\*pi\*10e6)

## Back-Up, Partial Eye Diagram

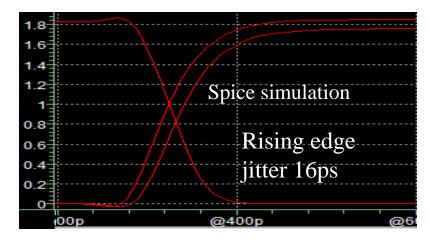

#### 2. Vcc=1.8V+0.05\*sin(2\*pi\*150e6)

23

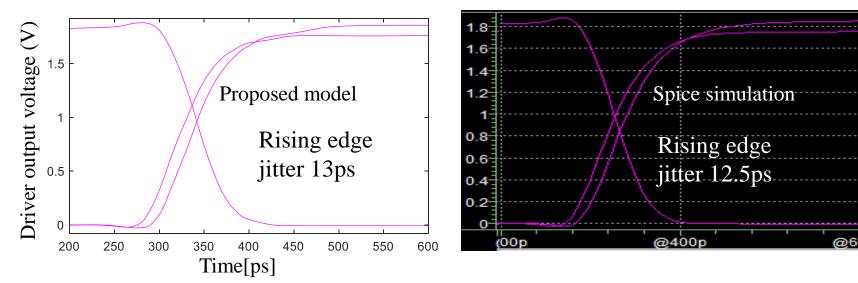

3. Vcc=1.8V+0.05\*sin(2\*pi\*1150e6)

## Back-Up, Partial Eye Diagram

# Back-Up, Ku, Kd Extraction

Extraction of Bu(t), Au(t), Bd(t) and Ad(t) from Ku(t), Kd(t) under different Vcc

2 equations, 2 unknowns algorithm = Ku(t), Kd(t)

1.5

2

Time

2.5

3

3.5

$imes 10^{-10}$

0

0

0.5

1

-0.2