# A further study on the application of IBIS to CISPR25 based EMI analysis of DCDC converter ~Resolving unexpected ringing in the waveform ~

Kazuyuki Sakata, Renesas Electronics Corp. Koji Ichikawa, DENSO CORP. Miyoko Goto, Ricoh Corp. Toshiki Kanamoto, Hirosaki University

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

# Motivation and objective

Most power device models are provided as Spice models dedicated to specific circuit simulators

- $\rightarrow$  Can not freely choose a circuit simulator

- Potential limitation by expression of each circuit simulator

- If the power device model can be represented with IBIS

- $\rightarrow$  Can freely choose a circuit simulator

- Can improve usability by gaining regularity

- Furthermore, if the IBIS model can be derived from measurement

- $\rightarrow$  Modeling made easier

JEITA IBIS-TG studies IBIS modeling of a power device DCDC converter, targeting to EMI simulation (CISPR25 conducted noise simulation)

In this presentation, we discuss error caused in the IBIS based DCDC noise simulation compared to the measurement, reported at 2019 Asian IBIS Summit (TOKYO, JAPAN)

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

# DCDC converter impedance measurement

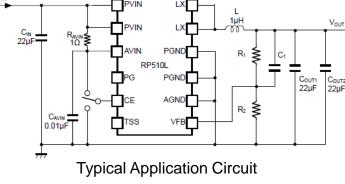

#### DCDC converter: RICOH RP510L004N-TR-A

IO Pins for impedance measurement

| С <sub>оит2</sub><br>22µF | Pin(S-G)  | No.(S-G)    | Pitch(mm)    | Bias voltage(V)                                          | Freq.(Hz)※ |

|---------------------------|-----------|-------------|--------------|----------------------------------------------------------|------------|

|                           | PVIN-PGND | PIN2-PIN10  | 2.65mm±0.3mm | 0,0.3,0.6,1,2,3, <mark>3.6</mark> ,4, <mark>5,5.5</mark> | 1k-3G      |

|                           | PVIN-LX   | PIN2-PIN11  | 2.6mm±0.3mm  | 0,0.3,0.6,1,2,3, <mark>3.6</mark> ,4,5,5.5               | 1k-3G      |

|                           | LX-PGND   | PIN11-PIN10 | 0.5mm±0.1mm  | 0,0.3,0.6,1,2,3, <mark>3.6</mark> ,4,5,5.5               | 1k-3G      |

%Frequency depends on equipment

cf.) https://www.e-devices.ricoh.co.jp/en/products/power/dcdc/rp510/rp510-ea.pdf

Equipment used in this report: HP4291A

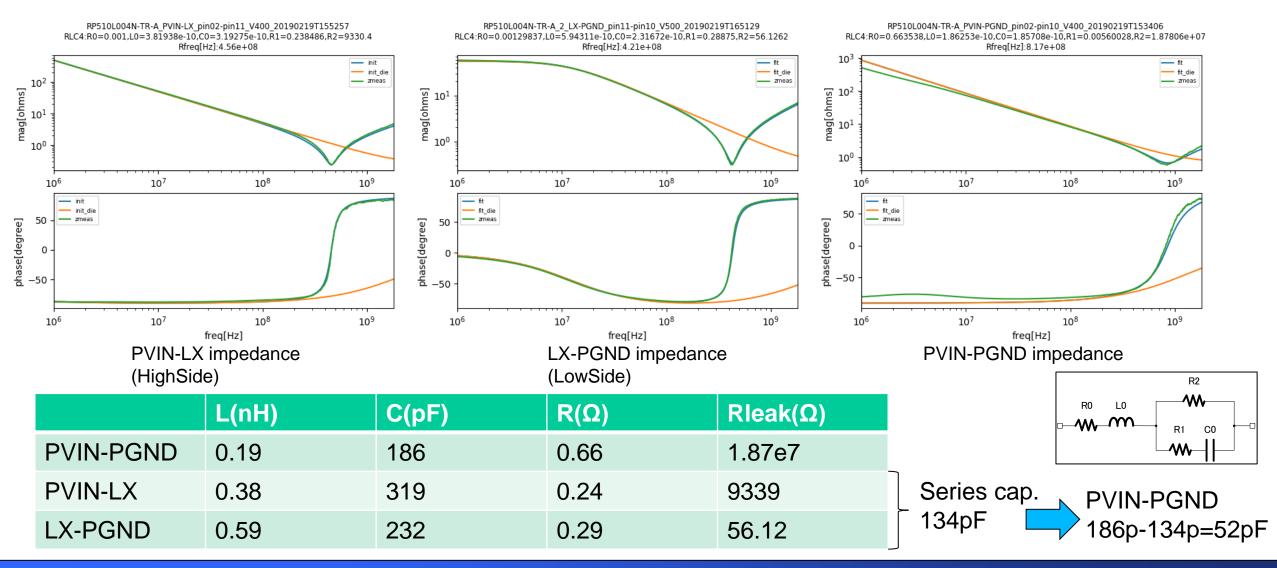

#### Impedance measurement and equivalent circuit

# Capacitance description in IBIS format

Specify the measured caps as C\_comp\_pullup, C\_comp\_pulldown in the IBIS format.

| [Model] bbb                                      |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|

| Model_type I/O                                   |  |  |  |  |  |

| Polarity Non-Inverting                           |  |  |  |  |  |

| Vinl = .72000000                                 |  |  |  |  |  |

| Vinh = 2.88000000                                |  |  |  |  |  |

| Vmeas = 1.8000000                                |  |  |  |  |  |

| C_comp 5.53197e-10 4.65065e-10 7.07186e-10   CDL |  |  |  |  |  |

| C_comp_pullup 319e-12 NA NA   Measurement        |  |  |  |  |  |

| C_comp_pulldown 232e-12 NA NA   Measurement      |  |  |  |  |  |

|                                                  |  |  |  |  |  |

In case that large discrepancy appear in the total capacitance, need to regenerate IBIS model adding supplemental capacitance to the Spice netlist.

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

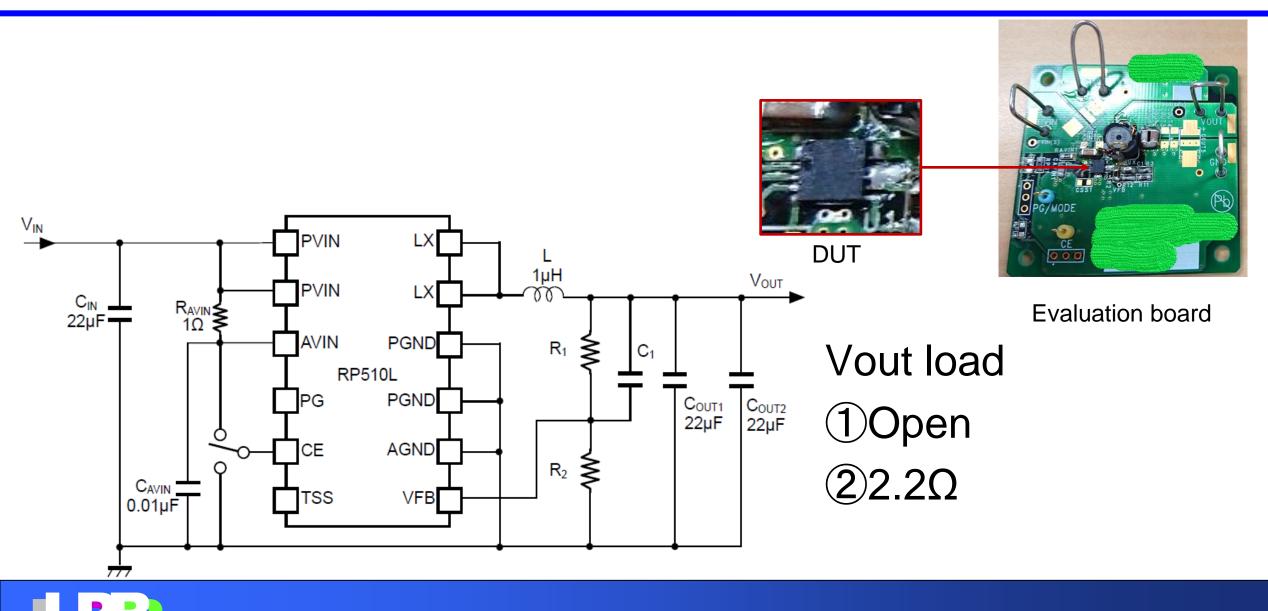

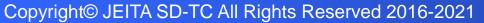

#### Measurement circuit construction

#### Measurement environment and results

Copyright© JEITA SD-TC All Rights Reserved 2016-2021

LPB

Page11

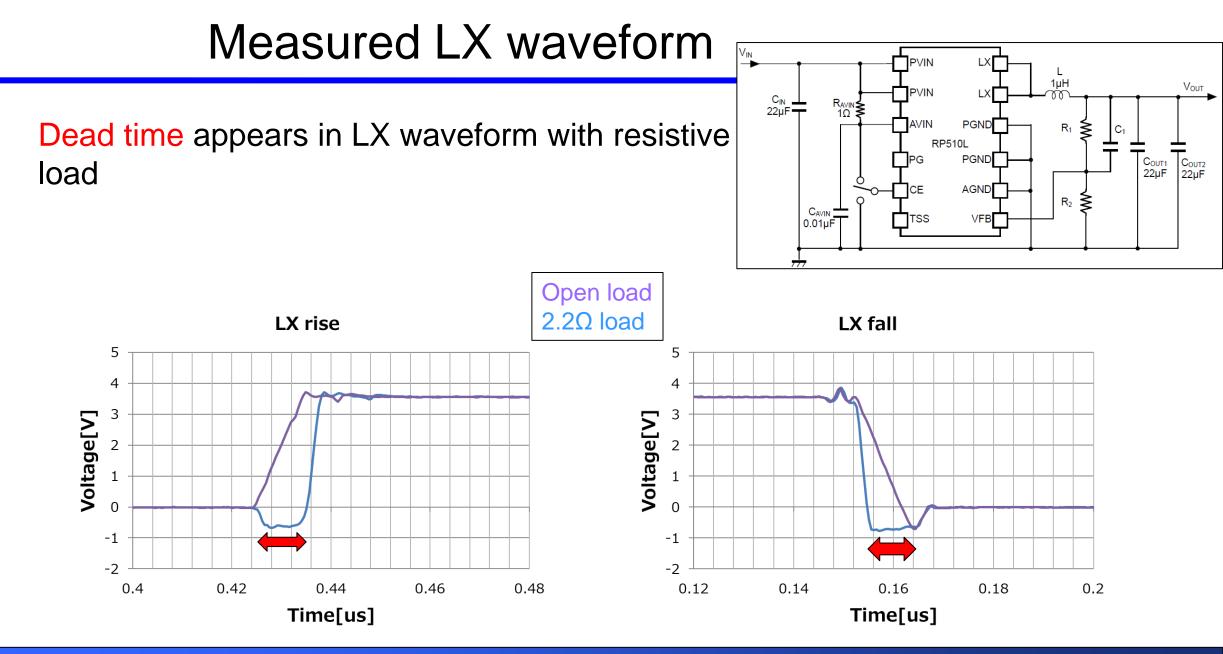

#### Printed circuit board model

Modeling printed circuit board by electromagnetic analysis

Copyright© JEITA SD-TC All Rights Reserved 2016-2021

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

Copyright© JEITA SD-TC All Rights Reserved 2016-2021

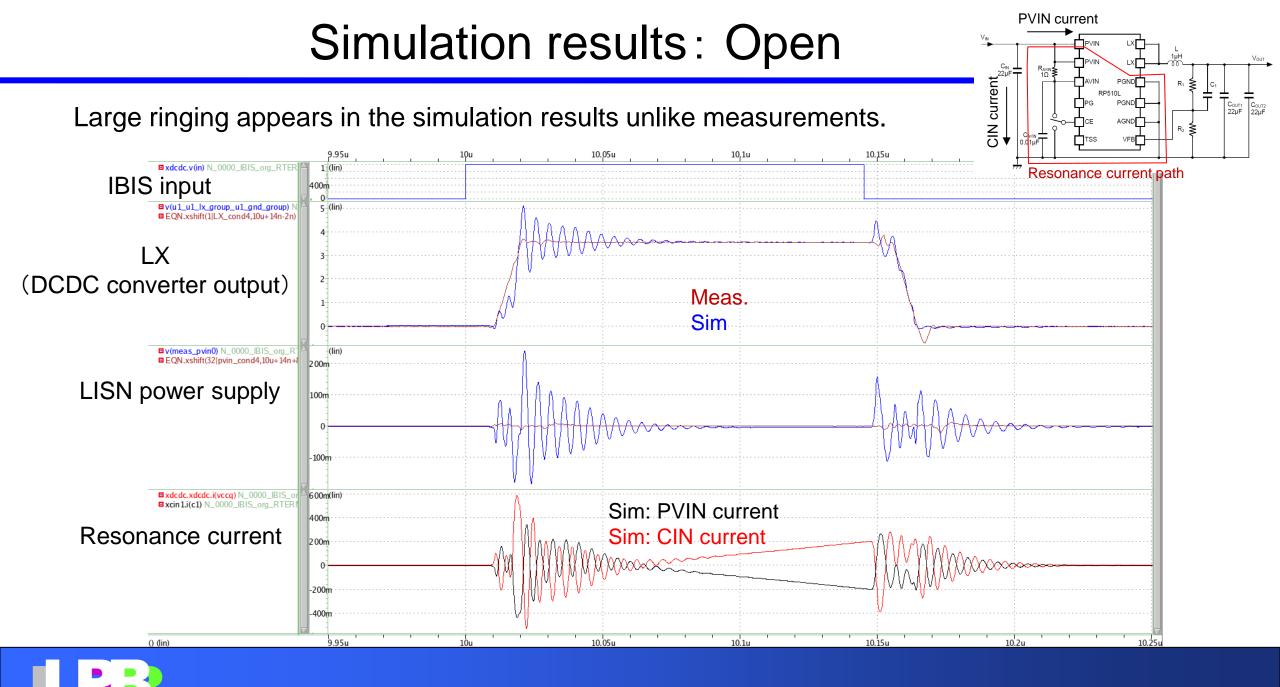

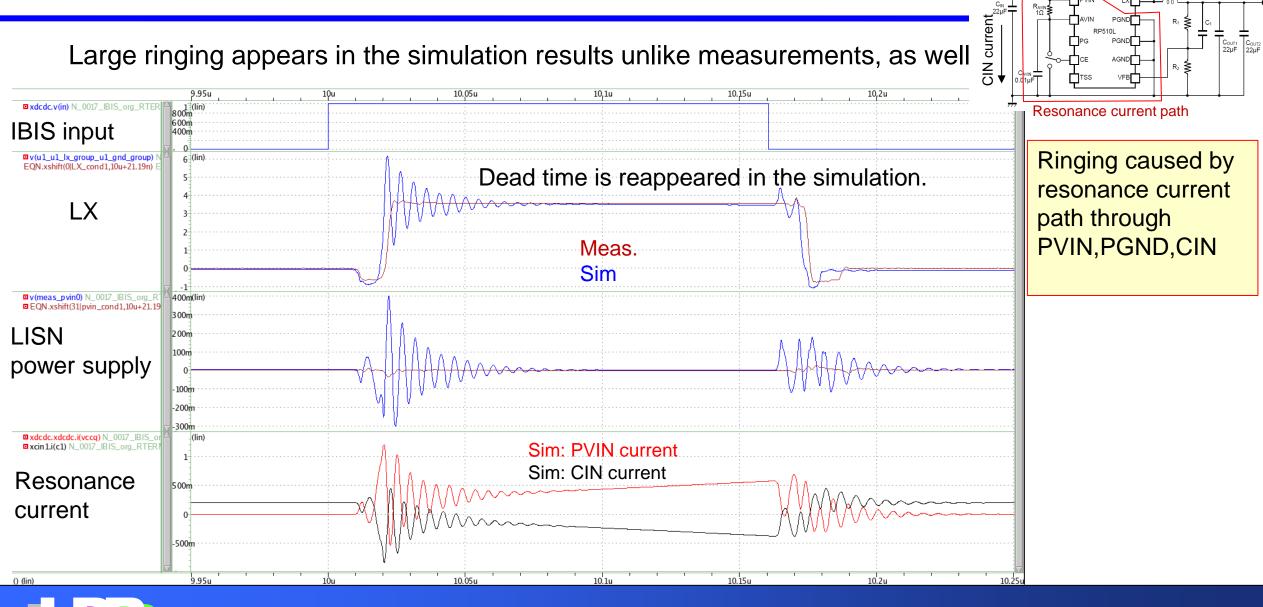

# Simulation results: Resistive load

**PVIN** current

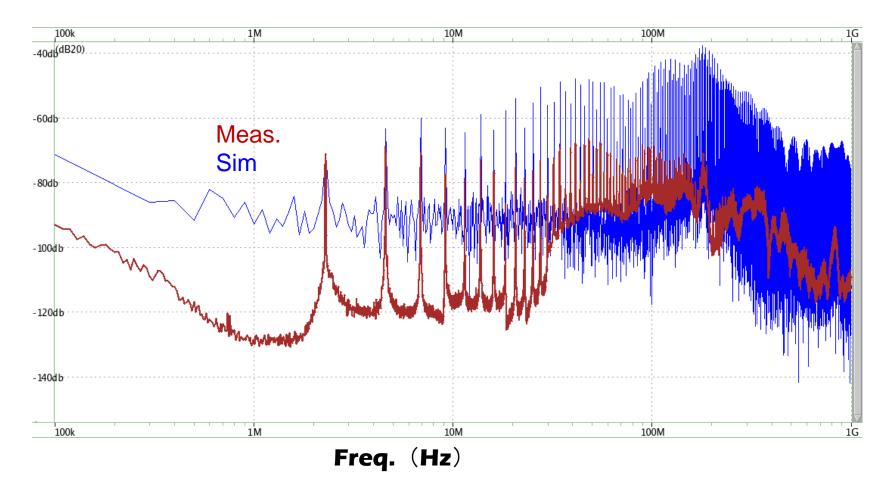

#### CISPR25 (Voltage) PVIN Noise: Open load

The simulation is up to 30db larger than the measured

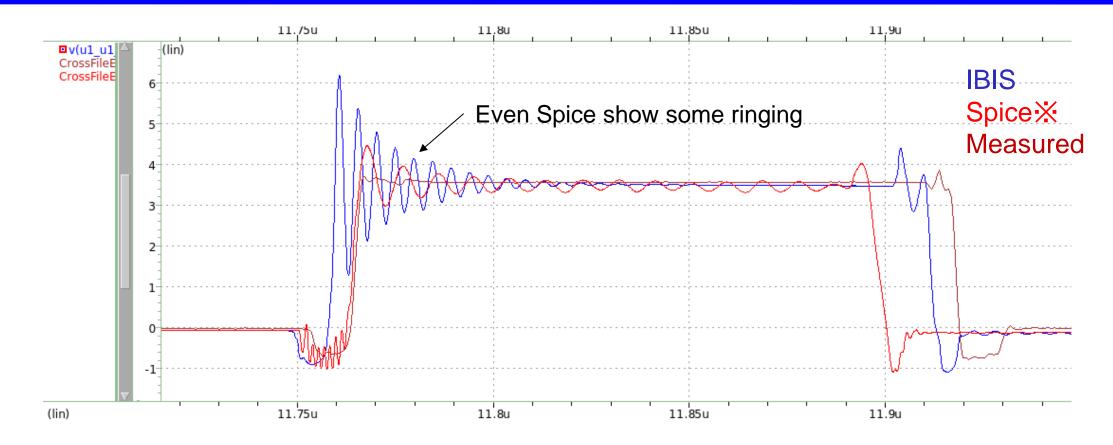

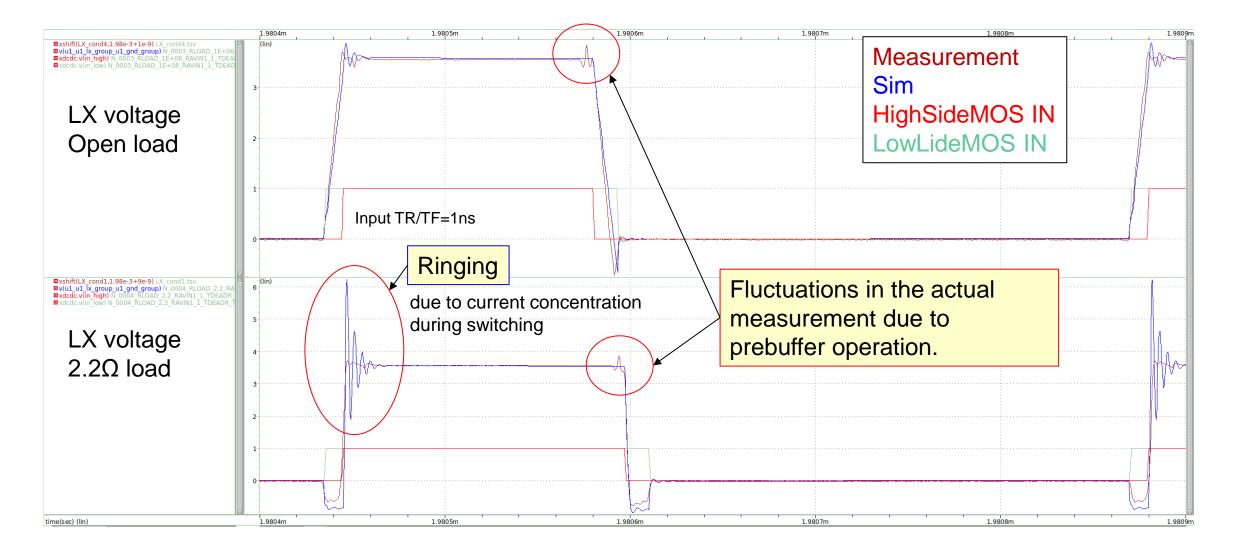

# LX (Output) Voltage: Spice, IBIS vs. Measurement

Even Spice simulation show some ringing waveform After trying to eliminate the ringing, consider the JISSO modeling.

**%**With pre-layout Spice netlist

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

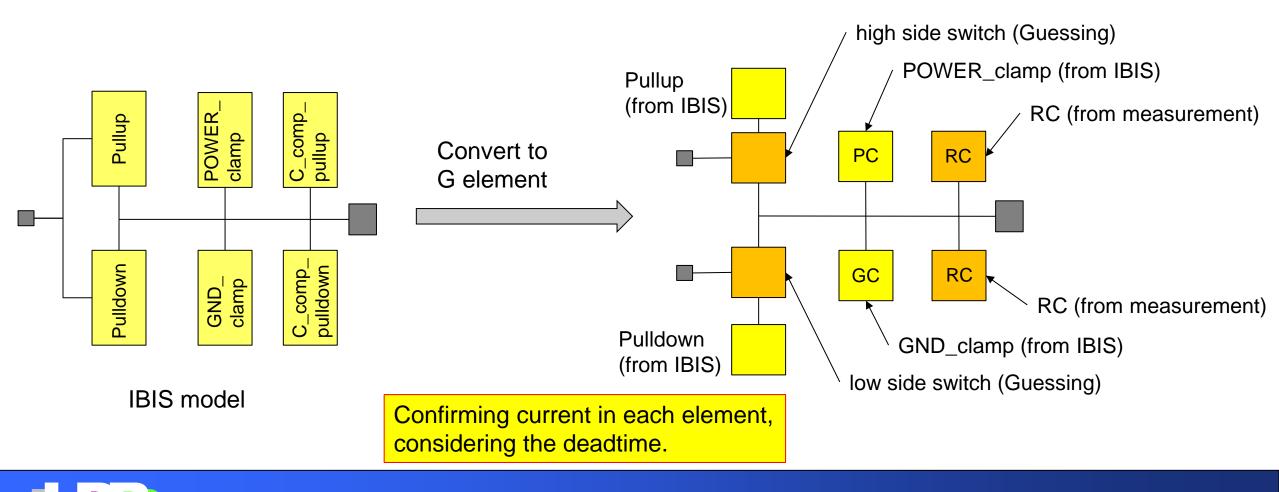

# From IBIS model to Spice macro-model

IBIS analysis by a circuit simulator is a black box approach. Not suitable for cause analysis. Macro modeling replacing IV tables in IBIS with G element in Spice. Then, white box analysis.

### A simple implementation

To simplify, only PVIN inductance is converted from S-parameter

Only inductance (0.9nH) is included in the circuit to analyze.  $V_{IN}$ **PVIN** LX 1µH Vout **PVIN** C<sub>IN</sub> \_ 22µF ─ R<sub>AVIN</sub> 1Ω AVIN PGND R<sub>1</sub> ≶  $C_1$ RP510L С<sub>оит2</sub> 22µF PGND PG С<sub>оит1</sub> 22µF AGND CE ≩  $R_2$ ÇAVIN TSS VFB 0.01µF 777

From EM field solver CIN loop inductance: 0.88nH CAVIN loop inductance: 2.17nH

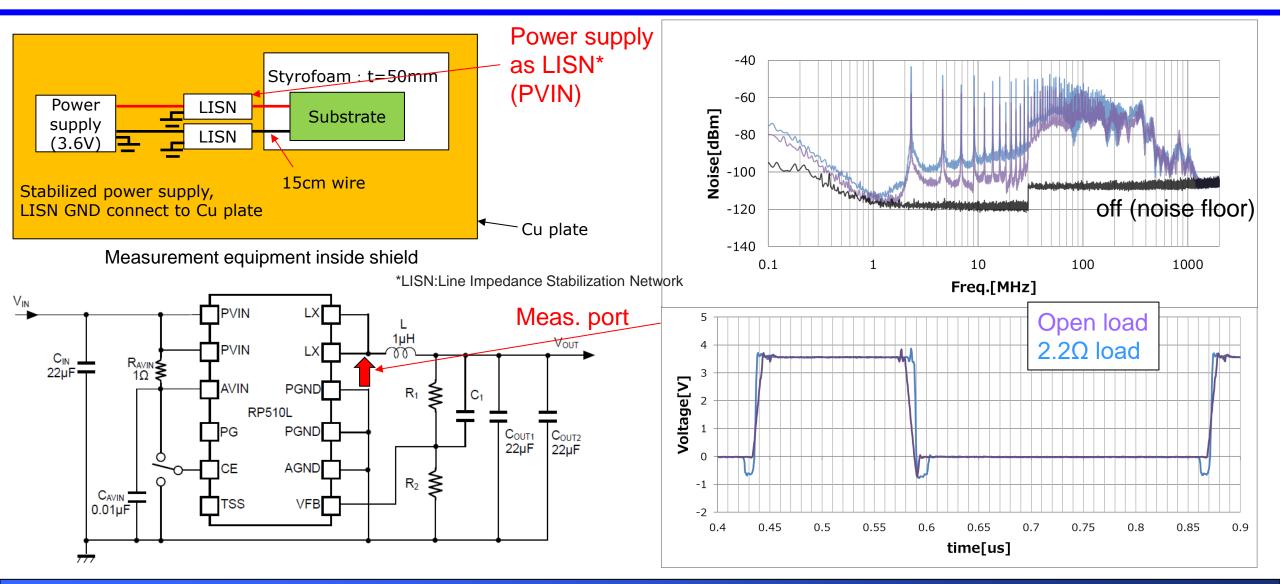

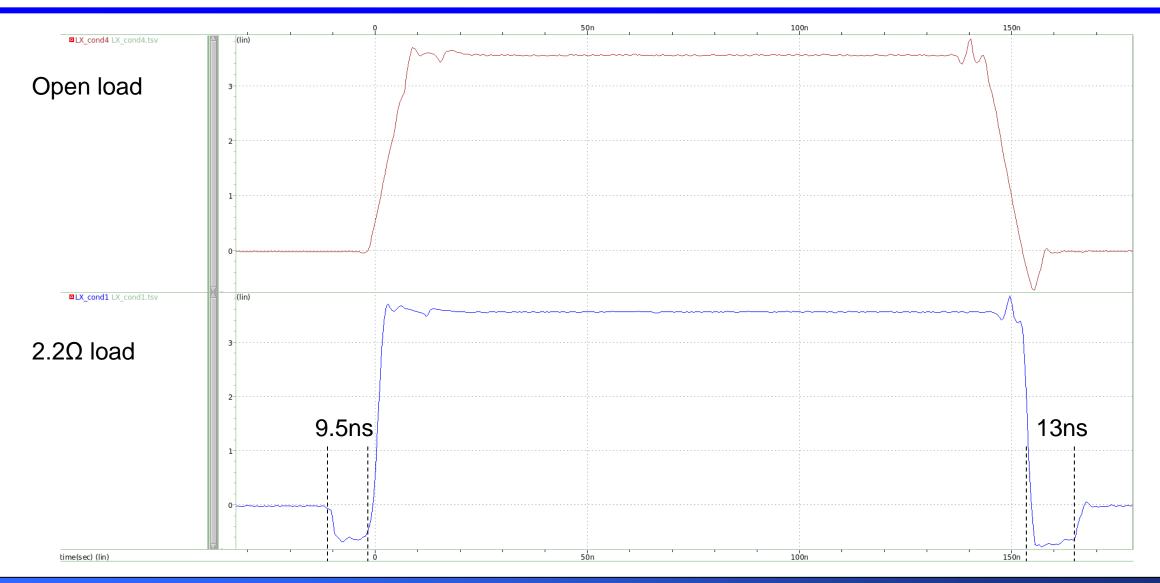

# Estimating deadtime from measurement (LX voltage)

Copyright© JEITA SD-TC All Rights Reserved 2016-2021

Page21

# Simulation result of Spice macro model (Simplified)

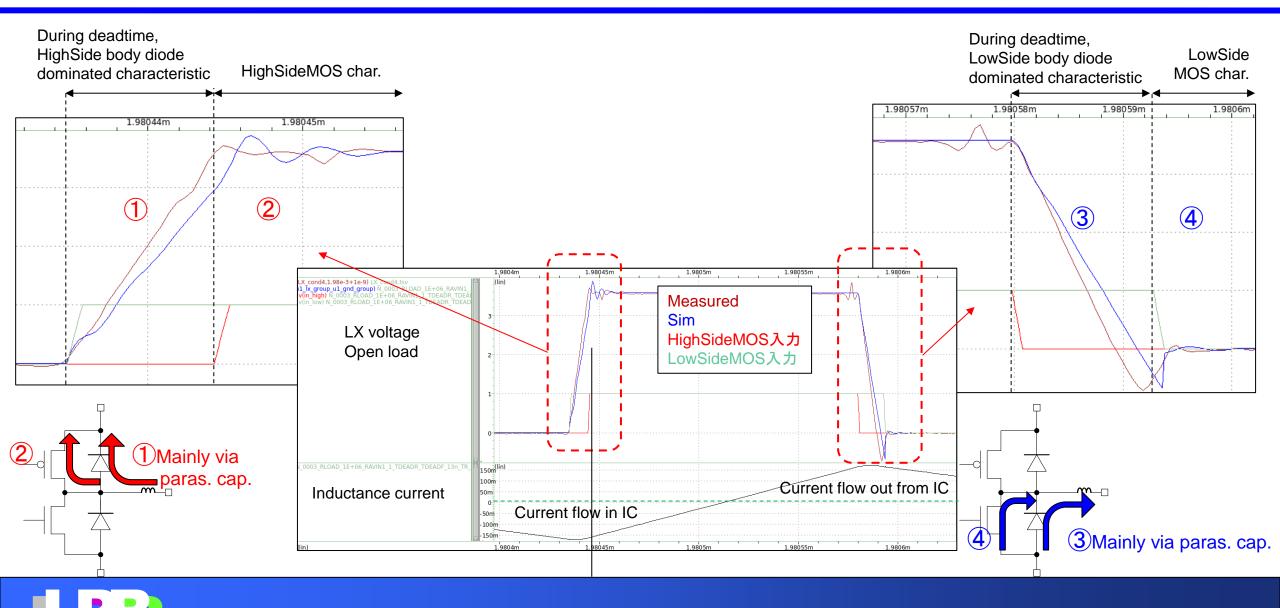

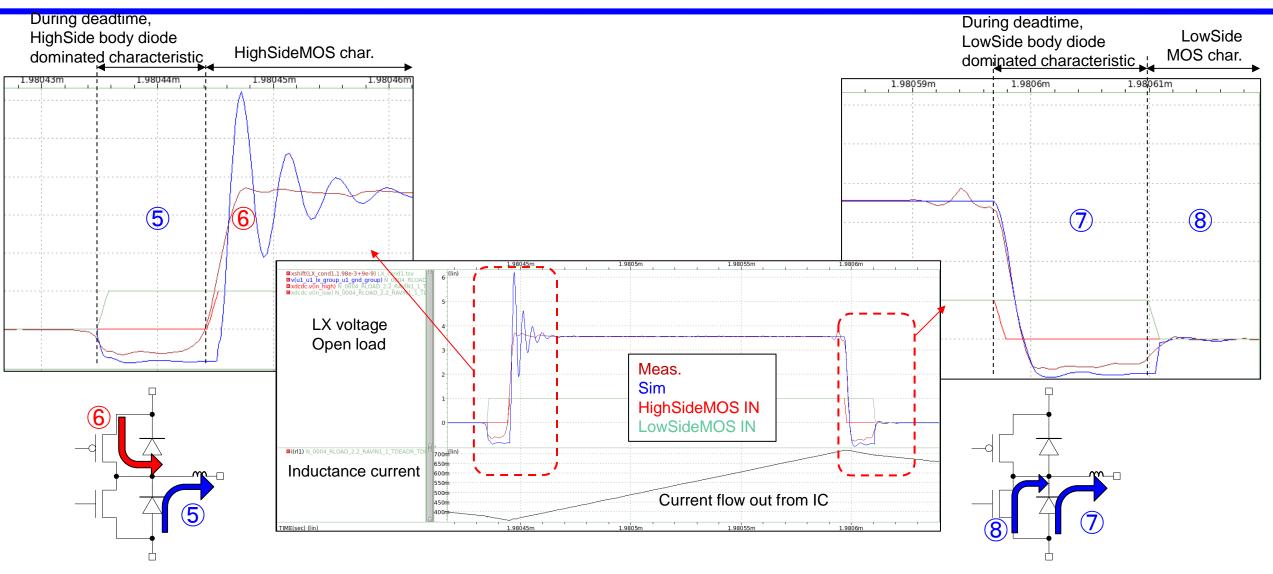

# Discussion according to macro model (Open load)

Copyright© JEITA SD-TC All Rights Reserved 2016-2021

# Discussion according to macro model (2.2 $\Omega$ load)

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

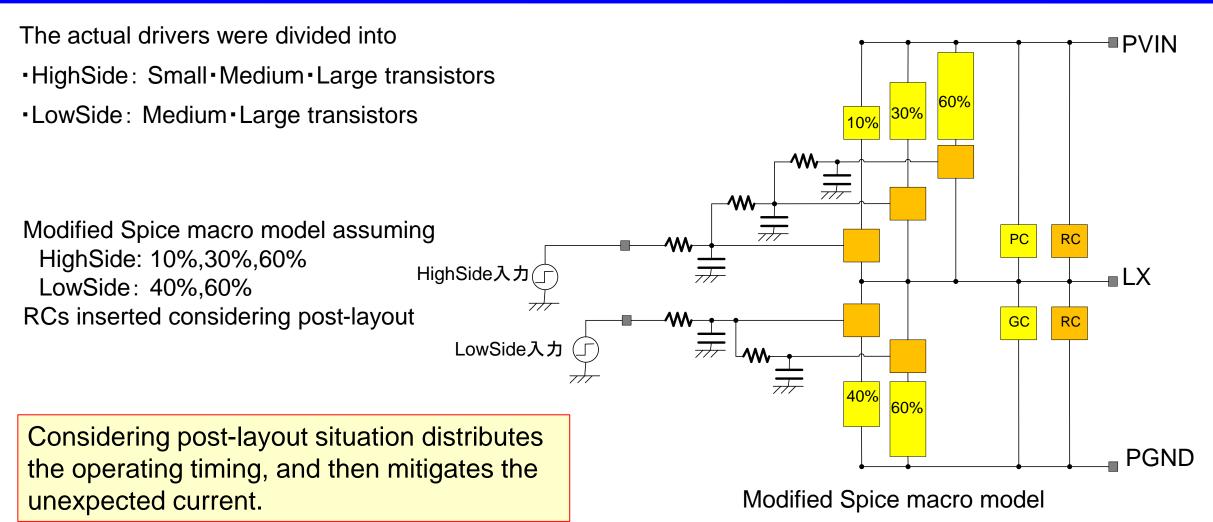

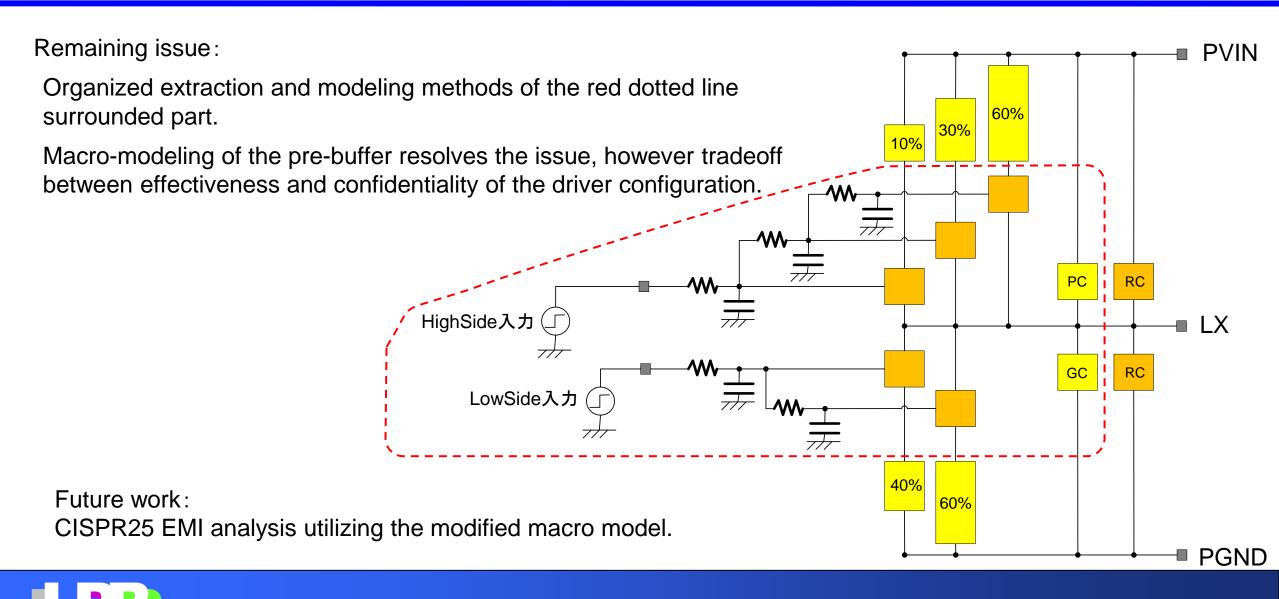

# Modified Spice macro model

Divided G-element by drivability, Inserted parasitic RCs

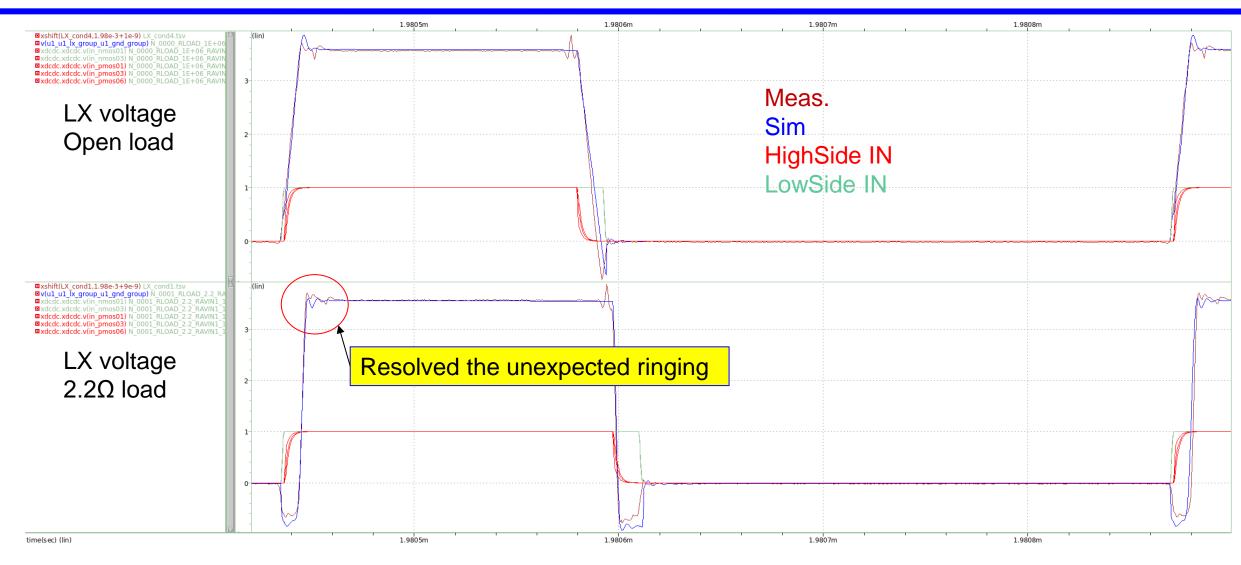

# Modified Spice macro model results (Simplified)

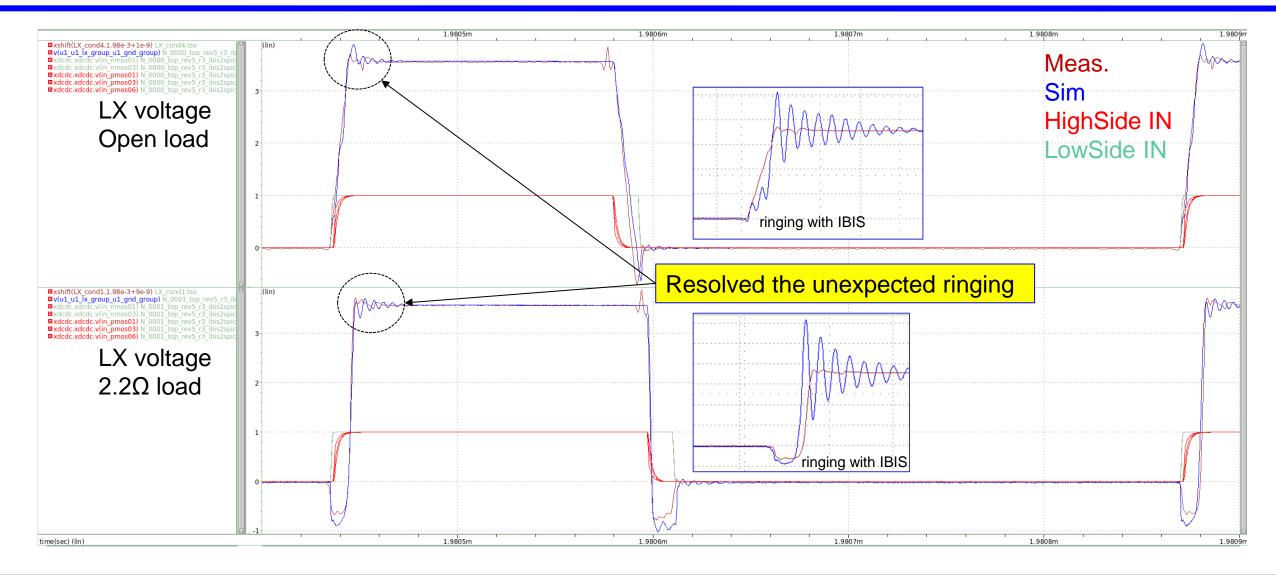

# Modified Spice macro model results (S-parameter)

Copyright© JEITA SD-TC All Rights Reserved 2016-2021

Page28

- Motivation and objective

- Impedance modeling of DCDC converters

- Measurement settings and results

- Simulation results and comparison with measurement

- Study on the discrepancy from the measurement

- From IBIS model to Spice macro model

- Improving the Spice macro model

- Summary

- Remaining issues and plans

# Summary

- Considering driver subdivisions as well as post-layout timing and slew rate is indispensable to re-create the actual waveform.

- In our experiment, adopting the actual driver subdivisions with the parasitic RC network has mitigated the previously reported unexpected current concentration and ringing in the waveform.

# Remaining issue and future work

Copyright© JEITA SD-TC All Rights Reserved 2016-2021