# IBIS4.2 and VHDL-AMS for SERDES and DDR2 Analysis

#### 31st October 2006

© Mentor Graphics Corp., 2006,

Reuse by written permission only. All rights reserved.

#### lan Dodd

Architect, High Speed Tools Ian\_dodd@mentor.com

#### Gary Pratt

Manager, High Speed Partnerships gary\_pratt@mentor.com

S ( ) ) (G

## **IBIS 4.2 Multi-lingual Extensions**

- Traditional IBIS lacks the ability to adequately model the behavior of devices used in state of the art communication channels:

- Drivers with pre-compensation

- Receivers with input slew rate sensitivity.

- Phase locked loop clock and data recovery

- Simple and adaptive equalization

- Multi-level signaling

- Traditional IBIS also lacks the ability to adequately specify new measurements:

- Differential overshoot

- Eye masks

#### IBIS 4.2 Multi-lingual Extensions can address both of these limitations

IBIS Open Forum, Japan, 31<sup>st</sup> October 2006

## **SPICE** as an IBIS 4.2 Multi-lingual option

- Good supply of transistor level models for older devices

- **May be encrypted and therefore not portable between tools**

- Poor standardization

- Lots of proprietary primitives

- Extremely slow simulation

- Particularly when using transistor level models

- Missing a high level view

- Needed to effectively model complex digital logic

- Needed to make complex measurements.

IBIS Open Forum, Japan, 31st October 2006

## AMS as an IBIS 4.2 Multi-lingual option

#### VHDL-AMS and Verilog-AMS International standards

- IEEE and Accellera

- **Fast.**

- Models are compiled to machine code just like built in primitives.

- **—** Digital content is handled in event driven kernel

- Flexible

- Can provide both behavior and measurement.

#### Accurate

**—** Uses the same analog non-linear solver as SPICE

## **IBIS 4.2 Multi-lingual Case Studies**

- The model maker and user can best decide whether it is best to create models using the IBIS 4.2 multi-lingual extensions utilizing SPICE or AMS

- The best solution for the SI Engineer may well be a tool that supports the mixing of both

- AMS provides some unique features so this presentation is going to provide two case studies that highlight these features.

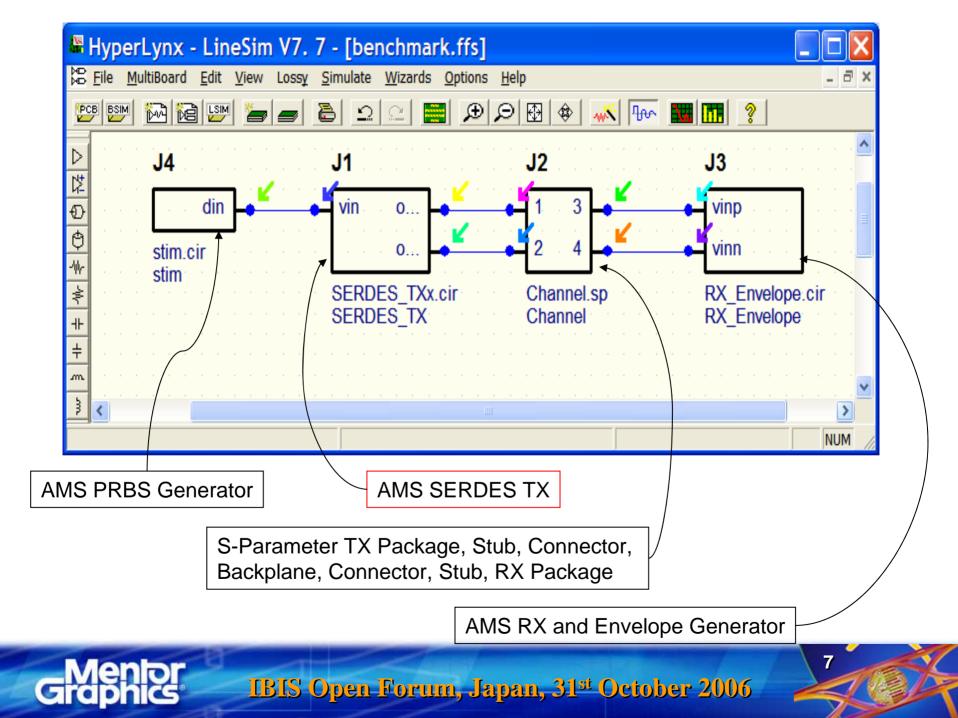

### **AMS Case Study One**

#### **Full non-linear analysis of a SERDES channel**

- Simulate to 10 million data bits

- Custom data pattern

- VHDL-AMS Driver with non-linear drive characteristics and pre-compensation

- Realistic S-Parameter model for packages, two connectors and backplane\*

- VHDL-AMS receiver model with built in envelope recorder

- Simulations to be done on an average single processor notebook computer running Microsoft Windows

- Appropriate simulation time-step for accurate results

\* As with previous examples used in presentations, this S-parameter model was provided by an independent third party and not optimized for simulation speed

6

IBIS Open Forum, Japan, 31st October 2006

#### **The VHDL-AMS SERDES Transmitter Model**

begin

-- output the proper current based on the state of signal din, -- and values of constants Ipe and Imain if domain = quiescent\_domain use - if DC then itxp == Ipe/2.0; itxn == Ipe/2.0; -- set both outputs to half elsif din='1' and din'delayed(bit) = '0' use itxp == Ipe; itxn == 0.0; -- first pulse (txp positive) elsif din='1' and din'delayed(bit) = '1' use itxp == Imain; itxn == Ipe-Imain; -- normal pulse (txp positive) elsif din='0' and din'delayed(bit) = '1' use itxp == 0.0; itxn == Ipe; -- first pulse (txn positive) elsif din='0' and din'delayed(bit) = '0' use itxp == Ipe-Imain; itxn == Imain; -- normal pulse (txn positive) end use; break on din, din'delayed(bit) ; -- deal with the discontinuities

-- P and N-side C\_comp, R\_term, Vdd i\_r\_term\_p == (vtxp - Vdd)/R\_term; i\_c\_comp\_p == c\_comp \* vtxp'dot; i\_r\_term\_n == (vtxn - Vdd)/R\_term; i\_c\_comp\_n == c\_comp \* vtxn'dot;

end architecture;

IBIS Open Forum, Japan, 31st October 2006

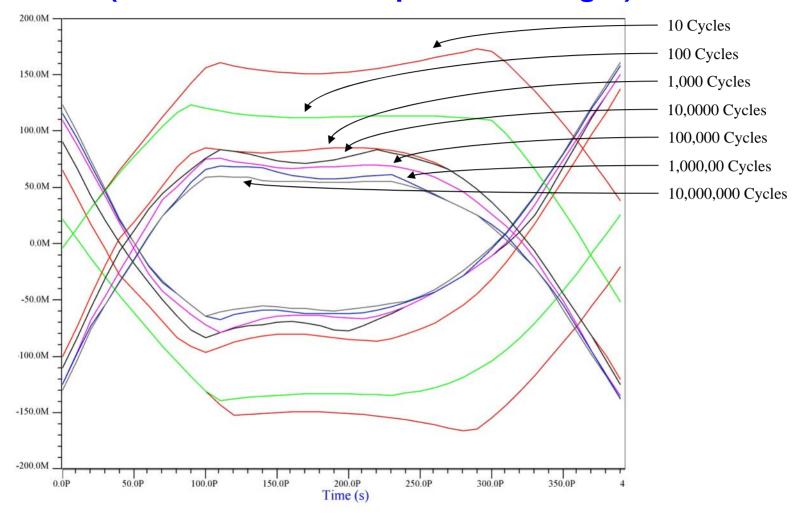

#### **Results: Simulation to 10 Million Data Cycles**

(All simulations completed overnight)

IBIS Open Forum, Japan, 31<sup>st</sup> October 2006

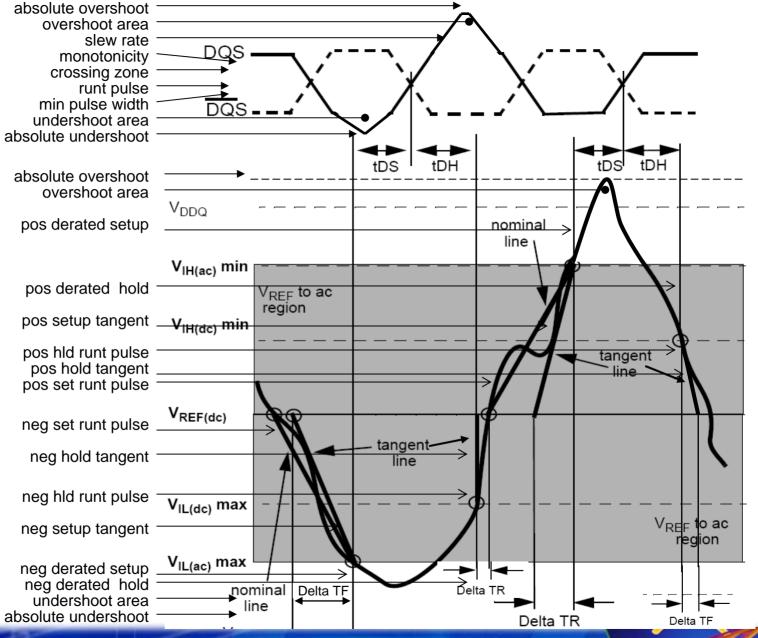

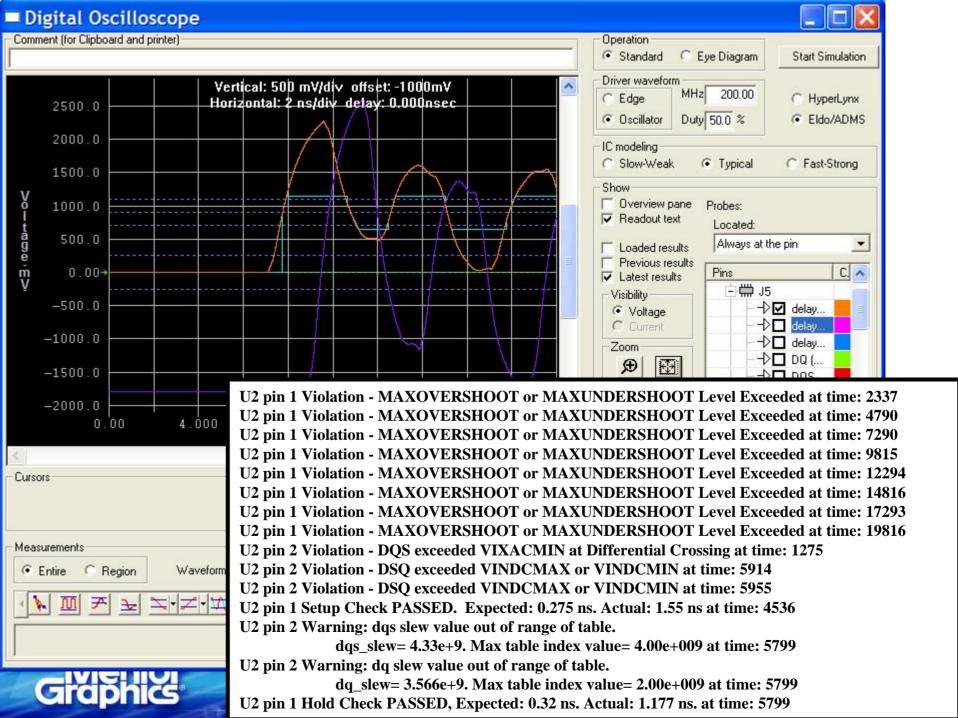

## AMS Case Study Two Automated DDR2 Measurements

- Implement all measurements specified in the DDR2 datasheet in a VHDL-AMS model

- Utilize standard IBIS 3.2 driver and receiver models

Constraints **DR2** Electrical and nng

IBIS Open Forum, Japan, 31<sup>st</sup> October 2006

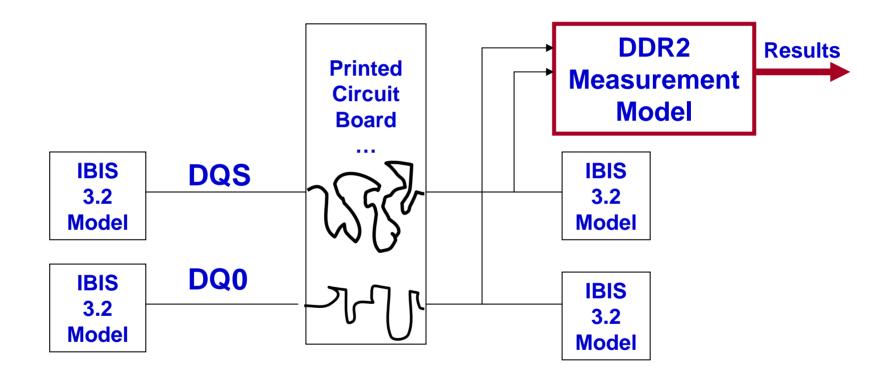

#### **IBIS 4.2 Measurement Model**

**IBIS Open Forum, Japan, 31st October 2006**

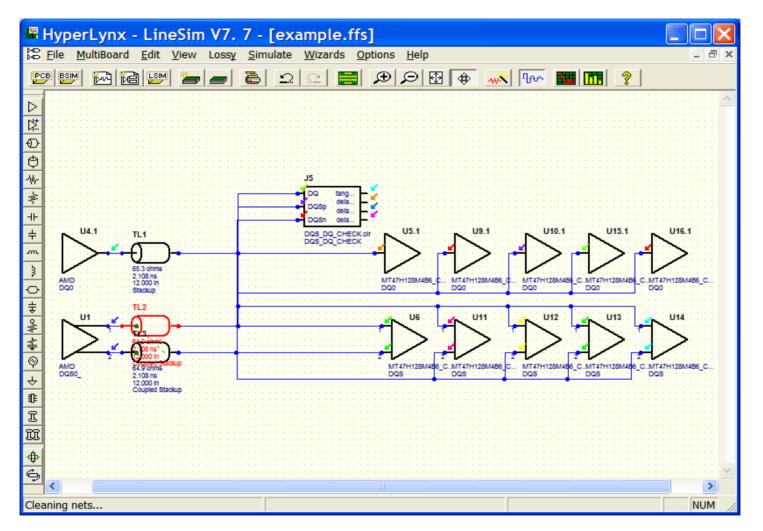

#### Pre-layout analysis using the IBIS 4.2 Measurement Model

IBIS Open Forum, Japan, 31<sup>st</sup> October 2006

#### TANGENT MEASUREMENT

Wait for vref crossing

Store data points

Wait for vix\_ac cross

Calculate the slope from each point to the vix\_ac crossing point

Return the maximum slope

Wait for vix\_dc crossing

Calculate the slope from each subsequent point back to the vix\_dc crossing

Wait for vref crossing Return the max slope

#### begin

-- measure the setup time tangent

```

wait until VREFDC: -- wait for a crossing of correct direction

max slope:=0.0; data point cntr:=0; setup crossing <= 0.0*sec;</pre>

while not vix ac'event loop -- store all the data points until vix ac crossing

data point v(data point cntr) := Vin'reference;

data point t(data point cntr) := now;

wait on vix ac, ASP; -- wait for next event

data point cntr := data point cntr + 1;

end loop; -- go on to find the maximum slope

setup crossing <= now;

for i in min slope to data point cntr-1 loop

slope := (crossing point v - data point v(i)) /

(crossing point t - data point t(i));

if slope > max slope then max slope:=slope; end if;

end loop;

setup slope <= max slope;</pre>

-- measure the hold tangent

wait until not vix dc; -- wait for opposite crossing of vix dc

max slope := 0.0;

crossing point v := Vin'reference; crossing point t:=now;

-- calculate slope of each point until vix dc, or max points

while not VREFDC'event loop

wait on VREFDC, ASP ;

slope := -(Vin'reference - crossing point v) /

(now - crossing point t);

if slope > max slope then max slope := slope; end if;

end loop;

hold slope <= max slope; -- in v/s

end process;

```

#### (error and exception handling removed for clarity)

14

IBIS Open Forum, Japan, 31st October 2006

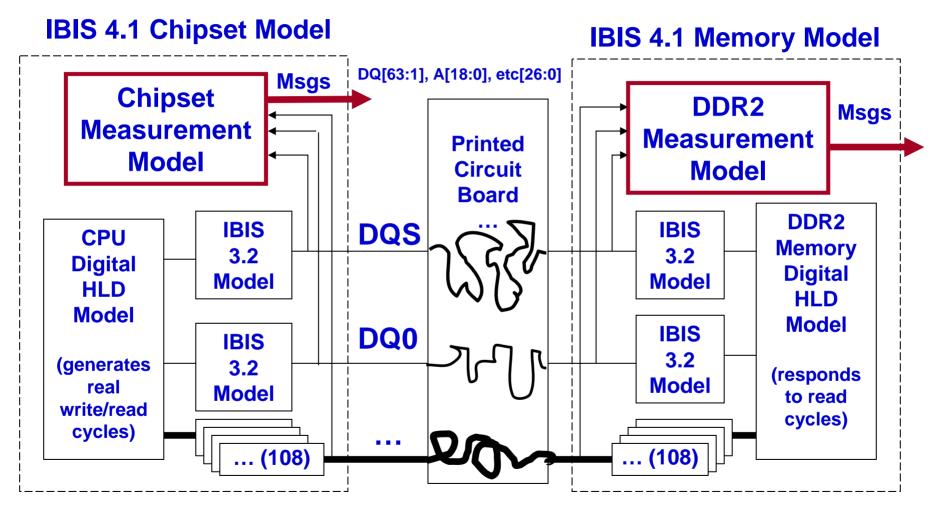

## Model for the Full DDR2 Channel Integrating both Behavior and Measurement \*

\* Note: This model is not in strictly IBIS 4.2 compliant because it uses an external circuit that references an IBIS 3.1 model

16

IBIS Open Forum, Japan, 31st October 2006

## **Special thanks to**

Randy Wolff and his associates at Micron for assistance in developing DDR2 simulation and measurement models.