# System-Level Timing Closure Using IBIS Models

Barry Katz President/CTO, SiSoft Asian IBIS Summit

Asian IBIS Summit – Tokyo, Japan - October 31, 2006

0 Õ

0

Signal Integrity Software, Inc.

# Agenda

- High Speed System Design

- Establishing timing model

- Derivation of timing equations

- Idealized timing analysis

- The role of signal integrity

- Reconciling signal integrity with timing

- Pre-route exploration

- Driving physical design

- Post-route validation

- Design analysis reuse

- Case study: DDR2 memory

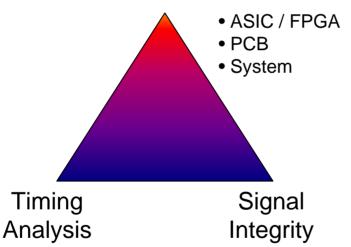

## High Speed System Design .... Not Just "Signal Integrity"

#### **Constraint-Driven Design**

- High Speed Design involves

multiple disciplines

- Changes in any area drive changes in others

- Mastery of modeling details & process flow is <u>essential</u> for success

# **System Level Timing Closure**

Successful high speed design requires a rigorous methodology for ensuring positive design margin across all combinations of:

**SiSofi**

- Component timing (process)

- Voltage & temperature

- Package & PCB routing lengths

- PCB manufacturing variations ( $Z_0$ , loss)

# **Establishing Timing Budgets**

õ

- High speed interfaces have one or more "transactions" that require timing closure

- Memory example:

- Address/control

- Data read

- Data write

- Strobe to Clock

- Timing relationships must be identified and closed for each different transaction

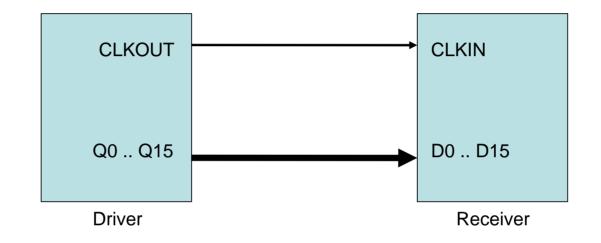

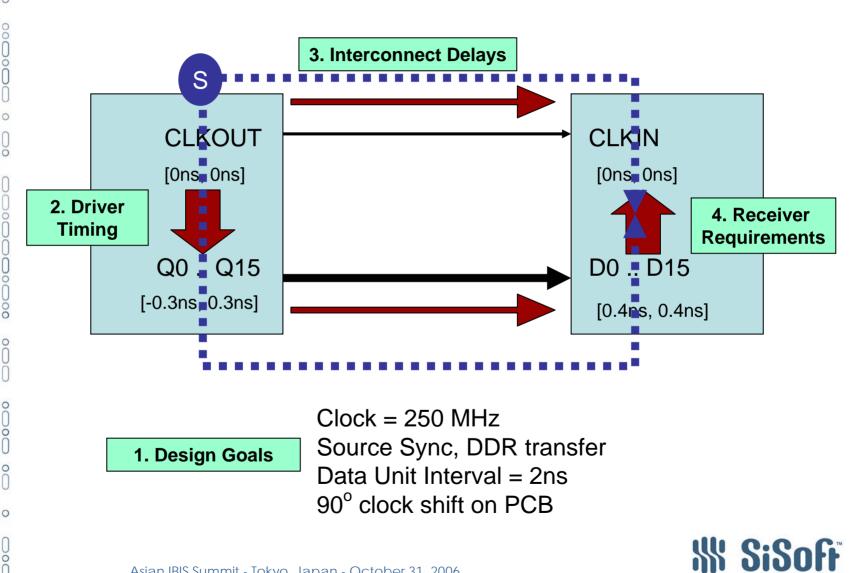

# **Source-Sync Transaction Example**

- Establish component timing & transfer protocol

- Derive timing equations

- Idealized timing analysis

- Signal integrity analysis and Timing Closure

**% SiSoff**

# **Component Timing, Transfer Protocol**

Asian IBIS Summit - Tokyo, Japan - October 31, 2006

õ

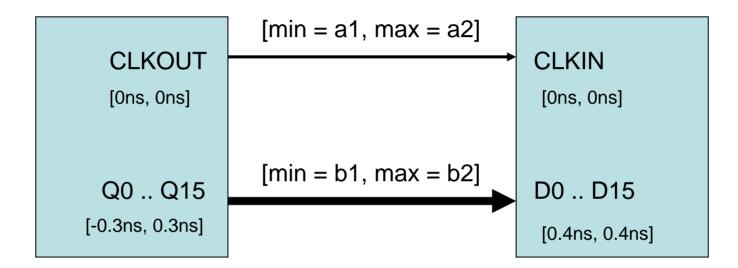

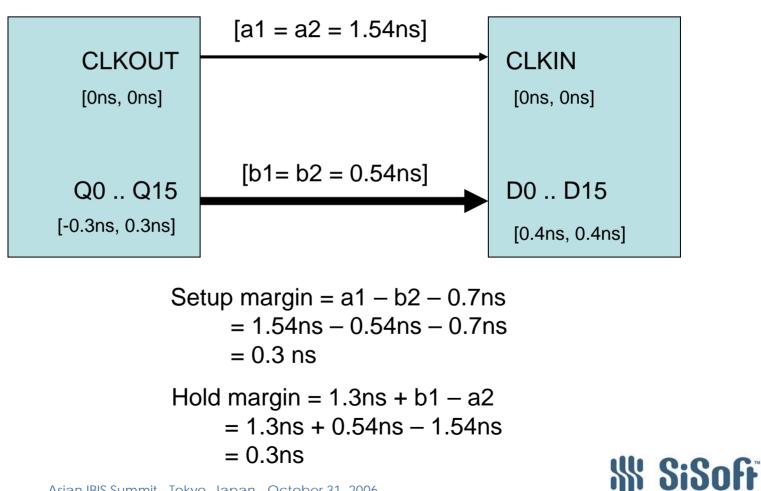

# **Derive Timing Equations**

Setup margin = [early clock] – [late data] – [setup requirement] = [0ns + a1] - [0.3ns + b2] - [0.4ns]= a1 - b2 - 0.7ns

Hold margin = [Data UI] + [early data] – [late clock] - [hold requirement] = [2ns] + [-0.3ns + b1] - [0ns + a2] - [0.4ns]= 1.3ns + b1 - a2

SiSofi

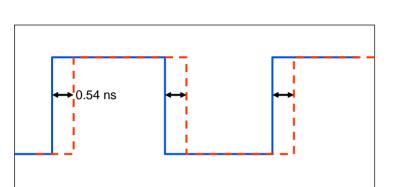

# **Idealized Timing Analysis**

Minimum data length =  $3^{\circ}$ , at 180 ps/in = 0.54 ns

# The Role of Signal Integrity

#### Idealized Delays

#### **Real-World Delays**

- Detailed analysis of digital switching behavior

- IBIS or HSpice models define I/O buffer behavior

- Accounts for

- Actual circuit loading

- Reflections / ringing

- Circuit topology

- Inter-symbol interference

- Switching thresholds

- Process, Voltage, and Temperature Variation

### **% SiSoff**

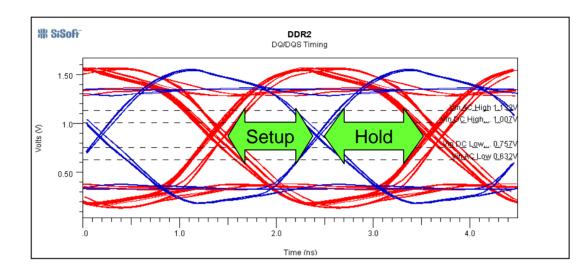

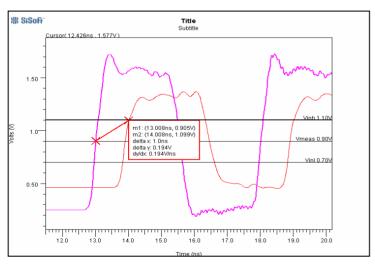

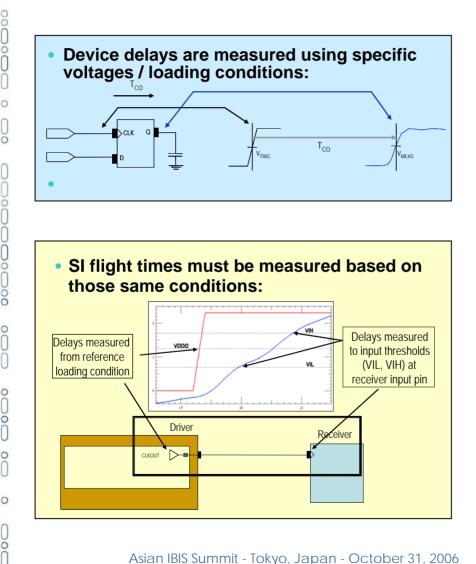

# **Reconciling SI with Timing**

õ

- Static timing and signal integrity measurements <u>must</u> be compatible

- SI measurements are "normalized" to conditions under which loading is specified

- IBIS Vref, Cref, Rref, Vmeas

- Timing Closure occurs when integrated timing/SI results show acceptable setup/hold margins

**SiSoff**

## **Building an Executable Timing Model**

| Microsoft Exce                   |                                                              |                          | ·                                            | w Help           |                                  |                            | Type a que:              | tion for h              | * • •                      | 2 × 9  |                                    |                  |                                |                                |   |                   |              |

|----------------------------------|--------------------------------------------------------------|--------------------------|----------------------------------------------|------------------|----------------------------------|----------------------------|--------------------------|-------------------------|----------------------------|--------|------------------------------------|------------------|--------------------------------|--------------------------------|---|-------------------|--------------|

|                                  |                                                              | _                        |                                              |                  |                                  |                            |                          |                         |                            |        |                                    |                  |                                |                                |   | _                 |              |

| 2 2 2 a a                        | s 🖄 12 S I                                                   | 2 🗄 🔒                    | Pol Reply wi                                 | th Changes       | Epd Review                       | -                          |                          |                         |                            |        |                                    |                  |                                |                                |   | F                 | O            |

| H30 -                            | 6                                                            |                          |                                              |                  |                                  |                            |                          |                         |                            |        |                                    |                  |                                |                                |   |                   |              |

| A                                | B                                                            | С                        | D                                            | E                | F                                |                            | G                        |                         | Н                          | -      |                                    |                  |                                |                                |   | tr                | a            |

| Setup<br>1 Margin (ns)           | Hold Margin<br>(ns)                                          |                          | Max Etch<br>Delay (ns)                       | Transfer<br>Net  | Drive                            |                            | Recei                    |                         | Column                     |        |                                    |                  |                                |                                |   |                   |              |

| 2 0.153<br>3 0.16                | 3 1.455                                                      | 1.727<br>1.73            | 2.233                                        | addcmd_8         | L ddr2_control<br>L ddr2_control | ler o                      | ddr2_sdram               | _1                      | mbl<1>                     | ÷.     |                                    |                  |                                |                                |   | Vá                | اد           |

| 4 0.160<br>5 0.160               | B 1.475                                                      | 1.747                    | 2.218                                        | addcmd_8         | L ddr2_control                   | ler (                      | ddr2_sdram<br>ddr2_sdram | _3                      | mbl<1><br>mbl<1>           | 1      |                                    |                  |                                |                                |   | VC                |              |

| 6 0.160<br>7 0.160               | B 1.475                                                      | 1.747                    | 2.218                                        | addomd_8         | L ddr2_control<br>L ddr2_control | ler d                      | ddr2_sdram<br>ddr2_sdram | 5                       | mpi<1><br>mbl<1><br>mbl<1> | ÷.     |                                    |                  |                                |                                |   |                   |              |

| 8 0.145                          | 9 1.446                                                      | 1.718                    | 2.237                                        | addcmd_8         | L ddr2_control<br>L ddr2_control | ler e                      | ddr2_sdram<br>ddr2_sdram | 7                       | mbl<1>                     | ÷.     |                                    |                  |                                |                                |   | _                 | _            |

| 9 0.158<br>10 No AC specs        | No AC specs                                                  | 1.727                    | 1.267                                        | ck_4L            | L ddr2_control<br>ddr2_control   | ler o                      | ddr2_sdram<br>ddr2_sdram | 1_c                     | mbl<1><br>NoDef            | 1      |                                    |                  |                                |                                |   |                   |              |

| 11 No AC specs<br>12 No AC specs | No AC specs                                                  | 1.263                    | 1.267                                        | ck_4L<br>ck_4L   | ddr2_control<br>ddr2_control     | ler o                      | ddr2_sdram<br>ddr2_sdram | 3_c                     | NoDef<br>NoDef             | ±      |                                    |                  |                                |                                |   |                   |              |

| 13 No AC specs<br>14 0.421       |                                                              | 1.263                    |                                              | ck_4L<br>ctrl_4L | ddr2_control<br>ddr2_control     |                            | ddr2_sdram<br>ddr2_sdram |                         | NoDef<br>mbl<1>            |        |                                    |                  |                                |                                |   | -                 | -            |

|                                  | Microsoft Excel - 1                                          |                          |                                              |                  | add control                      |                            | aar7 edean               | -                       | mblels                     |        |                                    |                  |                                |                                |   |                   |              |

| 18 0.                            | Ele Edt Yew                                                  |                          |                                              |                  |                                  | rial                       | • 10                     | • B .                   | / U 🔳 🔳                    |        | 15%,                               |                  | uestion for help               |                                |   | _                 | _            |

| 20 0                             | 🖢 🖄 🖄 🖂 🌭 🤅                                                  |                          |                                              |                  |                                  | ·                          |                          | _                       |                            |        |                                    |                  |                                |                                |   |                   |              |

| 22 0.                            | A1 -                                                         | ∱ Transf                 | fer Net                                      |                  | 5                                | 5                          |                          |                         |                            |        | L K                                |                  |                                |                                |   |                   |              |

| 23 0.<br>24 1.                   |                                                              | D                        | Ų                                            | 0                | c                                | r                          | DC-Vref                  | AC-Vref                 |                            | 2      | n.                                 | L                | м                              | ^                              |   | C                 | re           |

| 25 No AC spe                     |                                                              |                          |                                              |                  | Min                              | Max                        | Derate                   | Derate<br>Slew          |                            |        | Vref                               | Min<br>Vintleas  | Max<br>VinMeas                 | Min                            |   | Ŭ                 |              |

| 27 No AC spe                     | Transfer<br>Net<br>2 addcmd 8Lddr2                           | Driver                   | Receiver                                     | R/F              | Derating<br>(ns)<br>0.039        | Derating<br>(ns)<br>-0.035 | Rate<br>(V/ns)<br>0.763  | Rate<br>(V/ns)<br>0.735 | Corner                     | Edge # | Crossing<br>Time (ns<br>2 33.36    |                  | VinMeas<br>Time (ns)<br>33.708 | Derated<br>Time (ns)<br>33.244 |   | tii               | m            |

| 29<br>30<br>H 4 F H / V          | 3 addcmd_8Lddr2_<br>4 addcmd_8Lddr2_                         | controller<br>controller | ddr2_sdram_1<br>ddr2_sdram_1                 | R<br>F           | 0.028                            | -0.042                     | 2 0.815                  | 0.722                   | 2 TTTE<br>TTTE             |        | 3 38.41<br>4 48.35                 | 38.257<br>48.185 | 48.716                         | 38.285<br>48.221               |   | - CH              |              |

| Ready E                          | 5 addcmd_8Lddr2_<br>6 addcmd_8Lddr2_<br>7 addcmd_8Lddr2_     | controller               | ddr2_sdram_1<br>ddr2_sdram_1<br>ddr2_sdram_1 | F                | 0.041<br>0.007<br>0.03           | -0.046<br>-0.016<br>-0.052 | 5 0.947                  | 0.878                   | 3 TTTE<br>5 TTTE<br>3 TTTE |        | 5 58.41<br>6 63.35<br>7 78.41      | 63.202           | 68.779<br>63.693<br>78.784     | 58.279<br>63.209<br>78.272     |   | a                 | сıf          |

| 5                                | B addcmd 8L ddr2 addcmd 8L ddr2                              | controller<br>controller | ddr2_sdram_1<br>ddr2_sdram_1                 | F                | 0.023                            | -0.033                     | 0.845<br>0.735           | 0.768                   | 3 TTTE                     |        | 8 103.34<br>9 108.40               | 103.191          | 103.717<br>108.749             | 103.214 108.277                |   | a                 |              |

| 1                                | D addcmd 8L ddr2<br>1 addcmd 8L ddr2<br>2 addcmd 8L ddr2     | controller               | ddr2_sdram_1<br>ddr2_sdram_1<br>ddr2_sdram_1 | F<br>R           | 0.005<br>0.059<br>0.016          | -0.03<br>-0.052<br>-0.036  | 0.679                    | 0.679                   | 5 TTTE<br>9 TTTE<br>1 TTTE | 1      | 0 113.33<br>11 123.42<br>12 133.34 | 123.222          |                                | 113 212<br>123 282<br>133 221  |   |                   |              |

| 1                                | 3 addcmd_8Lddr2_<br>4 addcmd_8Lddr2_                         | controller<br>controller | ddr2_sdram_1<br>ddr2_sdram_2                 | R                | 0.026                            | -0.023                     | 3 0.826<br>9 0.763       | 0.826                   | TTTE                       | 1      | 3 138.41<br>2 33.36                | 138.211          | 138.72<br>33.708               | 138.238<br>33.244              |   | P                 | $\mathbf{O}$ |

| 1                                | 5 addcmd_8Lddr2_<br>6 addcmd_8Lddr2_                         | controller               | ddr2_sdram_2<br>ddr2_sdram_2                 | R<br>F           | 0.034                            | -0.042                     | 0.805                    | 0.672                   | 2 TTTE                     |        | 3 38.41<br>4 48.35                 | 48.193           |                                | 38.289<br>48.224               | - |                   | U            |

| 1                                | 7 addcmd_8Lddr2_<br>8 addcmd_8Lddr2_<br>9 addcmd_8Lddr2_     | controller               | ddr2_sdram_2<br>ddr2_sdram_2<br>ddr2_sdram_2 | F                | 0.043 0.034 0.047                | -0.048<br>-0.043<br>-0.047 | 3 0.785                  | 0.721                   | TTTE<br>TTTE<br>TTTE       |        | 5 58.40<br>6 63.36<br>7 78.41      | 63.2             | 63.709                         | 58.273<br>63.234<br>78.279     |   |                   |              |

| 2                                | 0 addcmd_8Lddr2_<br>1 addcmd_8Lddr2_                         | controller<br>controller | ddr2_sdram_2<br>ddr2_sdram_2                 | F                | 0.047                            | -0.048                     | 8 0.729<br>5 0.887       | 0.690                   | TTTE                       |        | 8 103.36<br>9 108.37               | 103.185          | 103.728<br>108.738             | 103.232<br>108.249             |   |                   | _            |

| 2                                | 2 addcmd_8Lddr2<br>3 addcmd_8Lddr2<br>4 addcmd_8Lddr2        | controller               | ddr2_sdram_2<br>ddr2_sdram_2<br>ddr2_sdram_2 | F<br>R<br>F      | 0.03                             | -0.027<br>-0.026<br>-0.036 | 5 1.002                  | 0.811                   |                            | 1      | 0 113.36<br>11 123.39<br>12 133.38 | 123.243          | 123.763                        | 113 213<br>123 243<br>133 212  |   |                   |              |

| 222                              | 5 addcmd 8L ddr2<br>6 addcmd 8L ddr2                         | controller<br>controller | ddr2_sdram_2<br>ddr2_sdram_3                 | R                | -0.005                           | -0.016                     | 5 1.056<br>9 0.763       | 0.874                   | TTTE                       |        | 3 138.37<br>2 33.36                | 138.246          | 138.745<br>33.708              | 138.241<br>33.244              |   |                   |              |

| 22                               | 7 addcmd_8Lddr2_<br>8 addcmd_8Lddr2_<br>9 addcmd_8Lddr2      | controller               | ddr2_sdram_3<br>ddr2_sdram_3<br>ddr2_sdram_3 | R<br>F           | 0.032                            | -0.042<br>-0.051<br>-0.05  | 0.787                    | 0.681                   | TTTE                       |        | 3 38.41<br>4 48.35<br>5 58.40      | 48.189           | 48.723                         | 38 288<br>48 223<br>58 282     |   |                   | -            |

| 33                               | 0 addcmd_8L ddr2 1<br>11 addcmd_8L ddr2                      | controller<br>controller | ddr2_sdram_3<br>ddr2_sdram_3                 | F                | 0.032                            | -0.04                      | 0.795                    | 0.736                   | S TTTE                     |        | 6 63.39<br>7 78.41                 | 63.201<br>78.237 | 63.699<br>78.778               | 63 233<br>78 277               |   |                   |              |

| 3                                | <ul> <li>addcmd_8L ddr2_i</li> <li>M / Eye Detail</li> </ul> |                          | ddr2_sdram_3<br>Details / Wav                |                  | 0.035<br>by Triet 🖌 War          | -0.051<br>reform Marg      |                          |                         | ? TTTE                     | 11     | 8 103.35                           | 103.189          | 103.722                        | 103.224                        |   | _                 | _            |

| Re                               | oady                                                         |                          |                                              |                  |                                  |                            |                          |                         |                            |        |                                    |                  | NUM                            |                                |   |                   |              |

|                                  |                                                              |                          |                                              |                  |                                  |                            |                          |                         |                            |        |                                    |                  |                                |                                |   |                   |              |

|                                  |                                                              |                          |                                              |                  |                                  |                            |                          | _                       |                            | _      |                                    |                  |                                |                                |   |                   |              |

| 4                                |                                                              | 4                        | _                                            | 4                |                                  |                            |                          |                         |                            |        | _                                  | 4                |                                | <b>4</b>                       |   | +t <sub>ssc</sub> |              |

- For each interface, all transactions must be validated for all cases:

- Component timing (process)

- Voltage, temperature

- PCB variations

- Creating an executable timing model to perform automatic regression is ideal

SiSofi

- **Possibilities**

- Excel

- **Custom scripting**

- **EDA** tools

Asian IBIS Summit - Tokyo, Japan - October 31, 2006

# **Pre-Route SI Exploration**

õ

- Pre-route simulations model planned

- Drivers

- Receivers

- Routing topology & lengths

- Termination

- Simulated interconnect delays are extracted and plugged back into the Executable Timing Model

- Setup and hold margins are calculated for temperature, process and voltage corners

#### **% SiSoff**

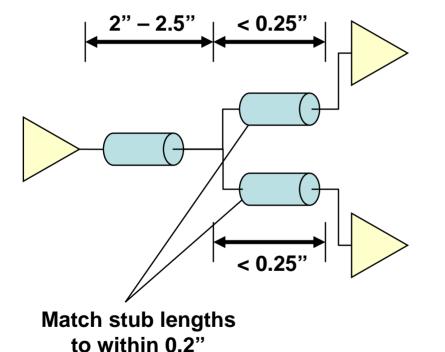

# **Driving Physical Design**

Asian IBIS Summit - Tokyo, Japan - October 31, 2006

- Pre-route SI/Timing analysis defines PCB routing rules

- Rules usually include pin ordering, length limits and stub matching

- Driving automated rules into PCB CAD is essential

**SiSoff**

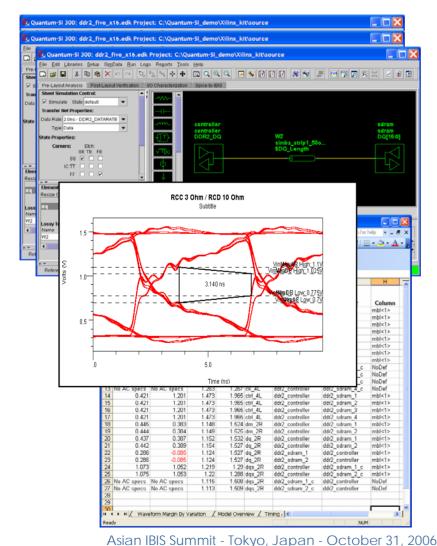

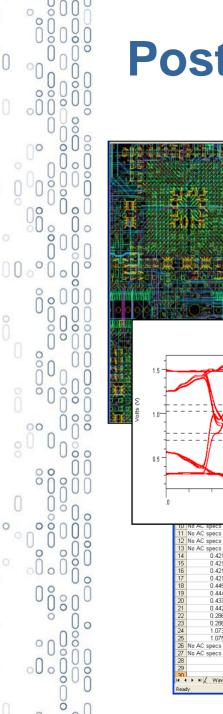

# **Post-Route Validation**

- Routed topologies are extracted from PCB database and simulated

- Simulated interconnect delays are extracted and plugged back into system timing model

- Setup and hold margins are calculated for temperature, process and voltage corners

2006

**SiSofi**

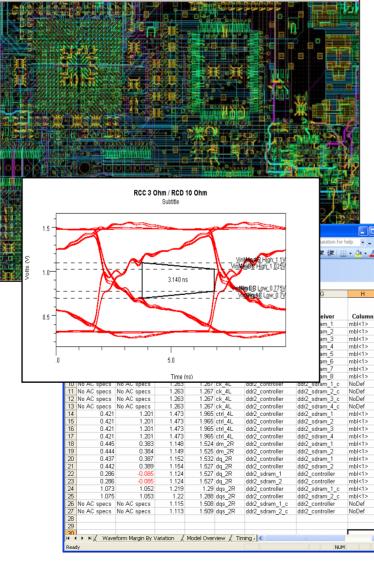

# **Design Analysis Reuse**

000

000

Π

Õ

Once all the SI/timing data for an interface has been captured, it should be possible to directly reuse that information for multiple instances in a project or other projects

Each interface kit contains net class schematics, timing data & SI models

#### **% SiSoff**

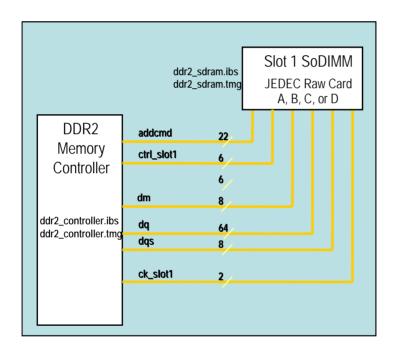

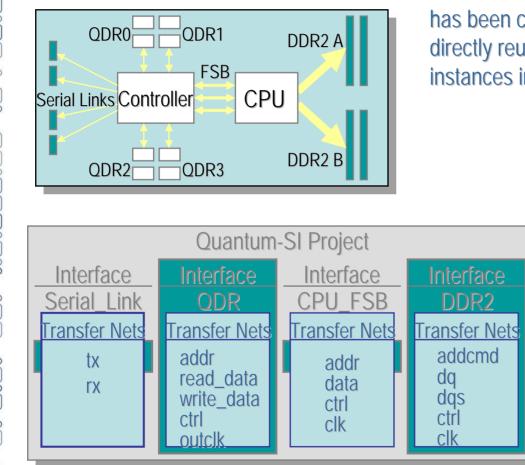

## **Case Study: DDR2 System Memory**

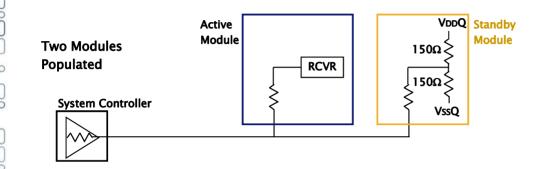

- DDR2 supports one or two DIMM modules

- DIMM Modules

- Registered and Unbuffered

- 4 to 18 memory devices

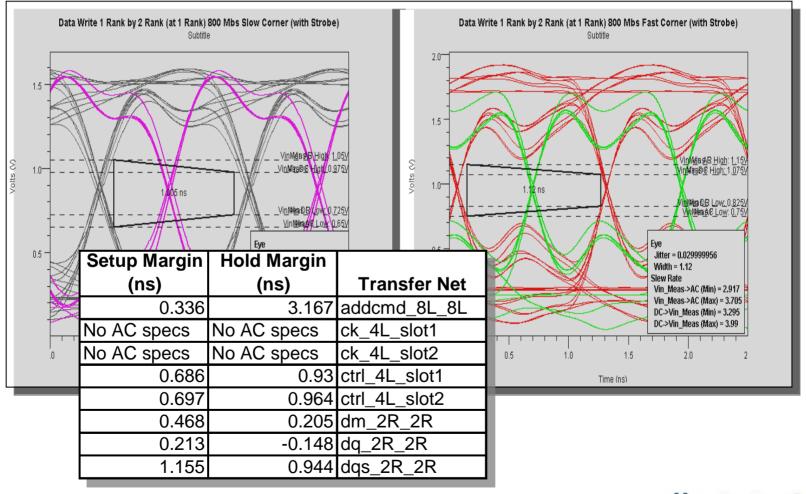

- Two module, data write transaction is presented here

- Complete case study:

"Features and Implementation of High-Performance 667Mbs and 800Mbs DDRII Memory Systems"

- Presented by Micron & SiSoft

- DesignCon West, 2005

- http://www.sisoft.com/papers.asp

# **DDR2 Data Write Configuration**

õ

| Write Configurations |          |                           |              |           |                |           |  |  |  |

|----------------------|----------|---------------------------|--------------|-----------|----------------|-----------|--|--|--|

|                      |          | DQ Active-Term Resistance |              |           |                |           |  |  |  |

| Configuration        | Write to | Controller                | Dram a       | at Slot 1 | Dram at Slot 2 |           |  |  |  |

|                      |          | Controller                | Front Side   | Back Side | Front Side     | Back Side |  |  |  |

| 2R / 2R              | Slot 1   | No Term                   | No Term      | No Term   | 50 or 75 ohm   | No Term   |  |  |  |

| 217/217              | Slot 2   | No Term                   | 50 or 75 ohm | No Term   | No Term        | No Term   |  |  |  |

| 2R / 1R              | Slot 1   | No Term                   | No Term      | No Term   | 50 or 75 ohm   | Empty     |  |  |  |

| 20/10                | Slot 2   | No Term                   | 50 or 75 ohm | No Term   | No Term        | Empty     |  |  |  |

| 1R / 2R              | Slot 1   | No Term                   | No Term      | Empty     | 50 or 75 ohm   | No Term   |  |  |  |

| IR / ZR              | Slot 2   | No Term                   | 50 or 75 ohm | Empty     | No Term        | No Term   |  |  |  |

| 1R / 1R              | Slot 1   | No Term                   | No Term      | Empty     | 50 or 75 ohm   | Empty     |  |  |  |

|                      | Slot 2   | No Term                   | 50 or 75 ohm | Empty     | No Term        | Empty     |  |  |  |

| 2R / Empty           | Slot 1   | No Term                   | 150 ohm      | No Term   | Empty          | Empty     |  |  |  |

| Empty / 2R           | Slot 2   | No Term                   | Empty        | Empty     | 150 ohm        | No Term   |  |  |  |

| 1R / Empty           | Slot 1   | No Term                   | 150 ohm      | Empty     | Empty          | Empty     |  |  |  |

| Empty / 1R           | Slot 2   | No Term                   | Empty        | Empty     | 150 ohm        | Empty     |  |  |  |

- Termination strategy is dynamic; depends on how many DIMMs are present and which device is receiving

- Simulation environment must switch receiver models based on which case is being analyzed

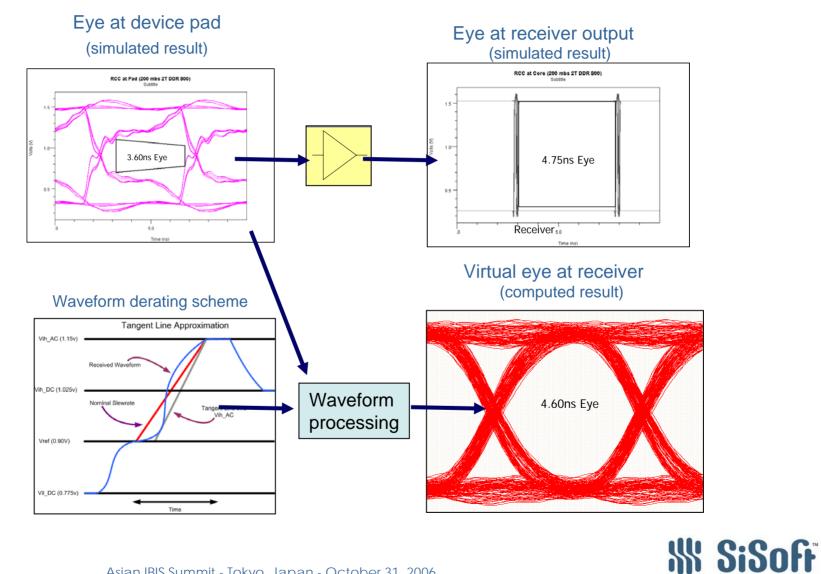

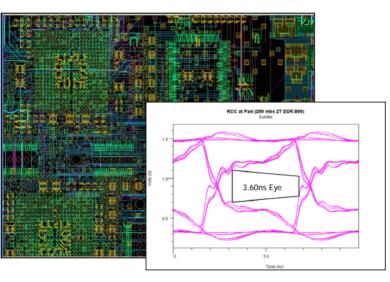

# **Slew Rate Derating – "Virtual Eye"**

00

00/

00

00

000

õ

0

)80

Õ

**SiSofi**

#### Summary

| Setup Margin | Hold Margin |               |  |  |  |

|--------------|-------------|---------------|--|--|--|

| (ns)         | (ns)        | Transfer Net  |  |  |  |

| 0.336        | 3.167       | addcmd_8L_8L  |  |  |  |

| No AC specs  | No AC specs | ck_4L_slot1   |  |  |  |

| No AC specs  | No AC specs | ck_4L_slot2   |  |  |  |

| 0.686        | 0.93        | ctrl_4L_slot1 |  |  |  |

| 0.697        | 0.964       | ctrl_4L_slot2 |  |  |  |

| 0.468        | 0.205       | dm_2R_2R      |  |  |  |

| 0.213        |             | dq_2R_2R      |  |  |  |

| 1.155        | 0.944       | dqs_2R_2R     |  |  |  |

- High-speed system design requires a rigorous, repeatable methodology for achieving Timing Closure

- Static Timing, Signal Integrity, and physical design rules are all interrelated

- An Executable Timing Model allows for a user to validate all transactions across all cases

- Signal Integrity analysis must be performed in accordance with the system timing model

#### **% SiSoff**