### The Direction of IBIS as a Standard

Michael Mirmak Chair, EIA IBIS Open Forum

**IBIS Summit** Tokyo, Japan October 31, 2006

#### Legal Disclaimers

THIS DOCUMENT AND RELATED MATERIALS AND INFORMATION ARE PROVIDED "AS IS" WITH NO WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. INTEL ASSUMES NO RESPONSIBILITY FOR ANY ERRORS CONTAINED IN THIS DOCUMENT AND HAS NO LIABILITIES OR OBLIGATIONS FOR ANY DAMAGES ARISING FROM OR IN CONNECTION WITH THE USE OF THIS DOCUMENT.

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance.

Intel may make changes to specifications, product descriptions, dates and plans at any time, without notice.

Copyright © 2006, Intel Corporation. All rights reserved.

# **IBIS** Development

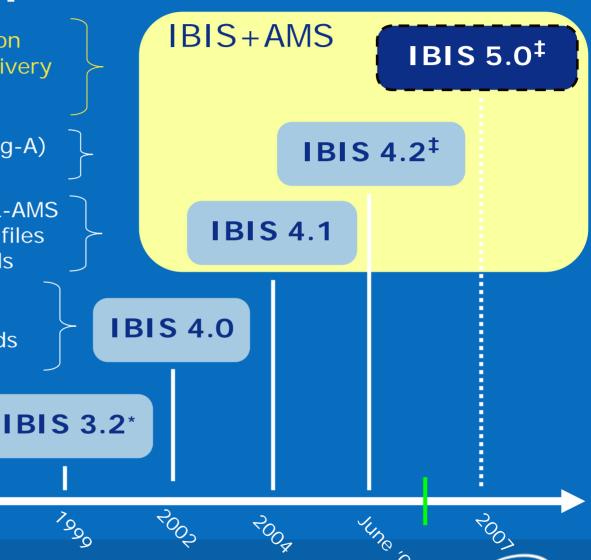

\* ANSI standard ‡ will be submitted for ANSI std.

- Restructuring of specification

- Gate modulation power delivery

- Links to ICM for packages

- Analog-only support (Verilog-A)

- Fixes for standardization

- Links to Verilog-AMS, VHDL-AMS

and Berkeley SPICE files

- · Differential thresholds, loads

- New meas. & delay loads

- Golden Waveforms and loads

- All IBIS 2.1 features

- Package modeling

- Series devices

- Scheduled drivers

To support new circuit design technologies, IBIS has grown and will continue to grow

## Industry Needs Are Changing Again

- Today's IBIS Technology Enables Today's Analysis Methods

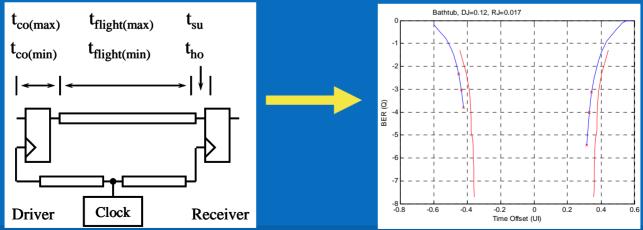

- Single-ended, source-synchronous interfaces slower than 1 GHz

- Setup and hold timing equations using pin measurements

- Worst-case corners analyzed using a few hundred or thousand bits

- Tools process analog waveform data taken at pins, pads

- Newer Technologies Suggest New Techniques

- Differential, low-swing interfaces at 1 GHz and above

- Eye diagram and statistical, BER analyses using 1e5, 1e6+ bits

- Response of entire channel is often analyzed as a unit

- Models are usually linear and may even support digital logic

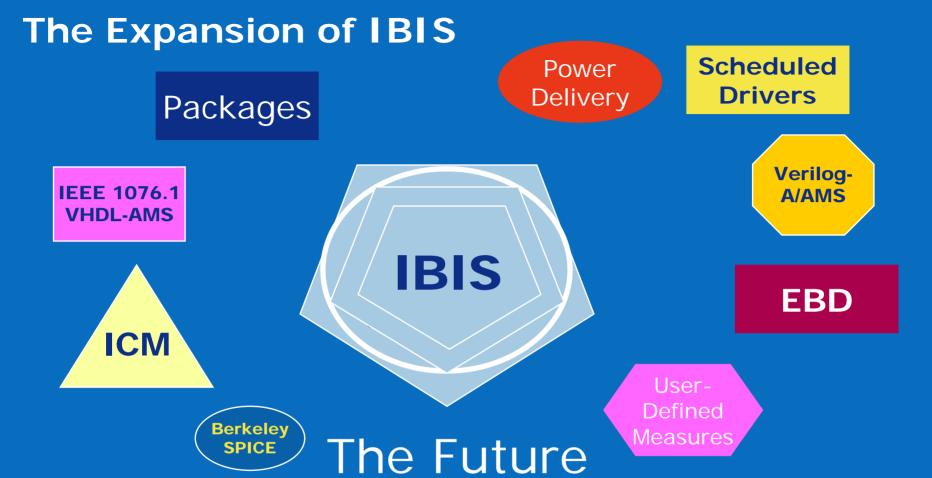

### **How Do We Support the New Methods?**

- A new discussion in the IBIS Advanced Technology Modeling group

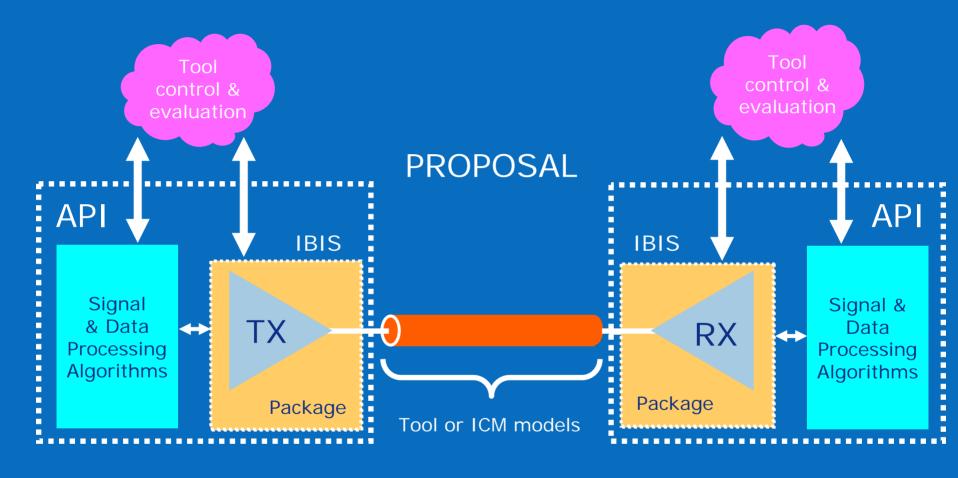

- Expand IBIS to include an API (application programming interface)

- The API would link to external C code for signal processing analysis

- Example: clock data recovery and bit-error rate (BER) estimation

- Similar effort underway in VHDL (IEEE 1076c)

- This would expand IBIS beyond <u>circuits</u> into <u>systems</u>

### **How Do We Support the New Methods?**

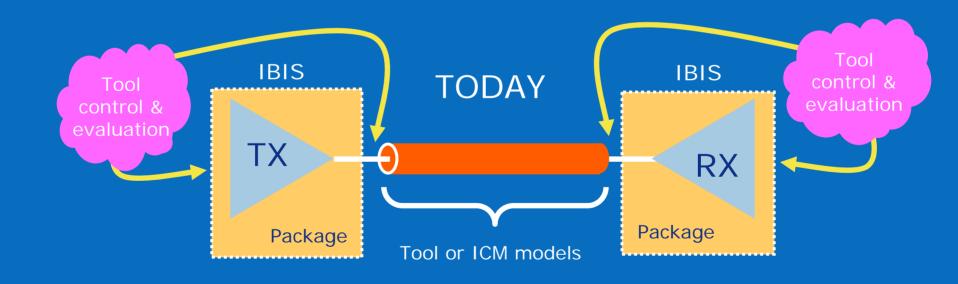

#### **Critical Choices**

- Should IBIS remain a circuit analysis standard or expand to systems?

- Would creating a new specification be more appropriate?

- Is an API needed?

- AMS languages under IBIS can support complex equations

- Can the AMS languages handle these new analysis needs?

- Where should the "model" end and the "tool" begin?

- Both AMS and an API would allow analysis procedures inside a model

- Should models include both circuit functions and tool functions?

- Example: tool or model API/AMS code could handle BER estimation

This issue will be discussed at this Summit and arises frequently in the IBIS community.

Your opinion matters!

#### References

- Official IBIS Website, including tools, articles, IBIS & ICM specs

- http://www.eigroup.org/ibis/

- The IBIS 4.0 Cookbook recommended for model creation!

- http://www.eda-stds.org/ibis/cookbook/

- IBIS Summit presentations

- http://www.eda-stds.org/ibis/summits/index-bydate.htm

- Accelera\* Verilog-AMS Working Group

- http://www.eda-stds.org/verilog-ams/

- IEEE\* 1076.1 (VHDL-AMS) Working Group

- http://www.eda-stds.org/vhdl-ams/

- Behavioral Modeling and Simulation Conference 2006

- http://www.bmas-conf.org/2006/

- On-line signal integrity classes & references

- http://www.intel.com/education/highered/signal/elct762.htm

- http://www.intel.com/education/highered/signal/elct865.htm

- Join the IBIS and IBIS-Users e-mail reflectors!