#### **JEITA EDA -WG Activity**

Oct 31, 2006

IBIS Summit in Japan

JEITA EDA-WG

Takeshi Watanabe (NEC Electronics)

#### **Outlines**

- 1. JEITA EDA-WG Activities

- 2. Short Term Direction of JEITA EDA WG

- 3. Study of Interconnect Model

- 4. JEITA IBIS Model Portal site Plan

#### 1. JEITA EDA-WG Activities

#### **Objectives of JEITA EDA**

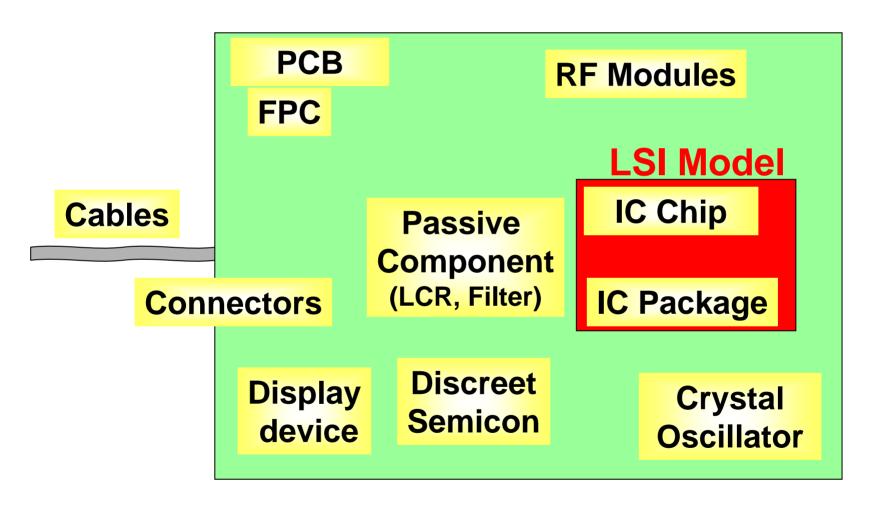

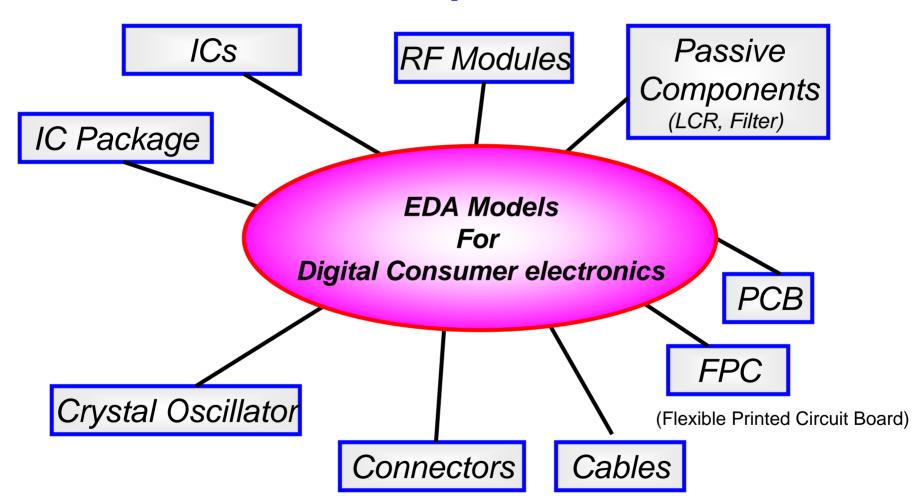

#### **EDA Model for**

#### **Digital Consumer Electronics**

Cellular Phone, LCD /PDP TV, Digital Camera/Video, DVD Recorder

(Digital, RF, and Analog circuits)

Auto Mobile Electronics ?

(Motor Drive, EMC)

< Applicability of IBIS V4.1 >

## EMI, SI and PI for Digital Consumer Electronics

#### <Background>

**EMI** High-speed Clock Frequency

SI DDR, PCI, PCI-Express

PI High density and Large scale IC

SiP and Module, PCB level

EMI, SI and PI Simulation Technology

#### **EDA Model for EMI, SI and PI Simulation**

#### Focus of EDA Model for Simulation

#### 9 components

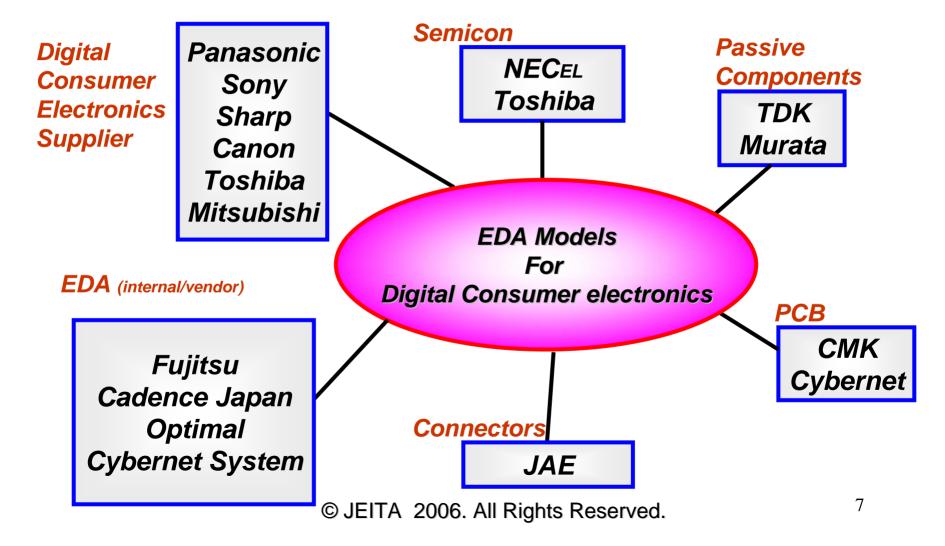

#### **JEITA EDA-WG Member**

#### 16 Major Companies

#### 2. Short Term Direction of JEITA EDA WG

- Study of Interconnect Model

- •EDA Models of Passive Components and Connector and other Components

- JEITA IBIS Model WEB

- Discussion about Case study of Simulation for Digital Consumer Electronics

- and JEITA-IBIS Joint meeting periodically

#### **Study of Interconnect Model**

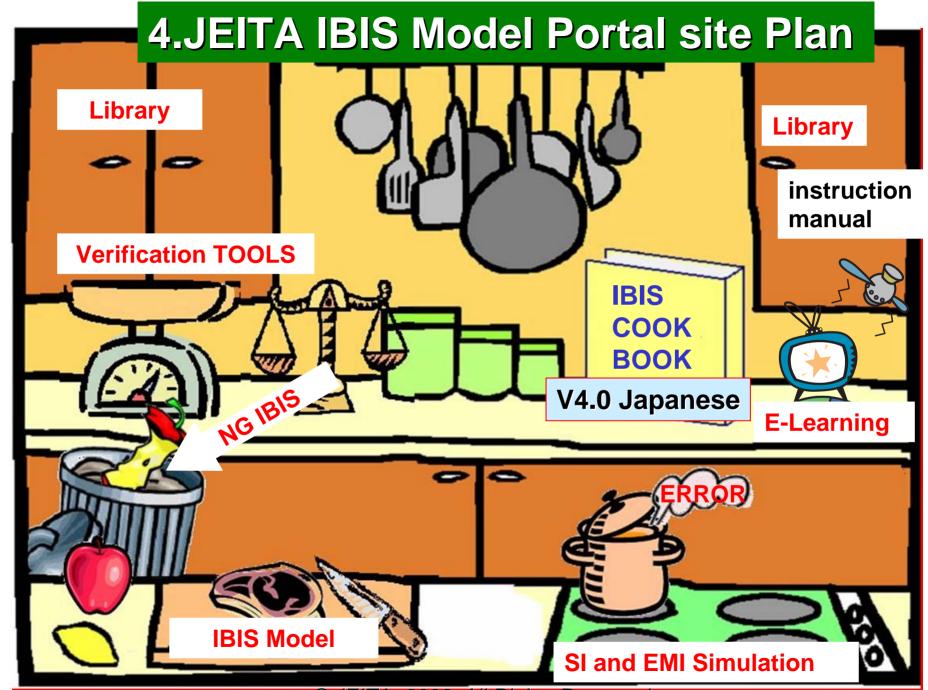

#### **JEITA IBIS Model Portal site Plan**

|     |        |     |                      | EDA Model    |              |       | EDA Tool    | Environment                   |

|-----|--------|-----|----------------------|--------------|--------------|-------|-------------|-------------------------------|

|     |        | ICs | Passive<br>Componets | C onnec tors | PCB<br>board | Cable | (recommned) | for the usage<br>of EDA Model |

| SI  | <1Gbps | 0   | 0                    | 0            | 0            | 0     | 0           | 0                             |

|     | >1Gbps | 0   | 0                    | 0            | 0            | 0     | 0           | 0                             |

| ЕМІ | <3GHz  | 0   | 0                    | 0            | 0            | 0     | 0           | 0                             |

| PI  | <3GHz  | 0   | 0                    |              | 0            |       | 0           | 0                             |

0 foremost task

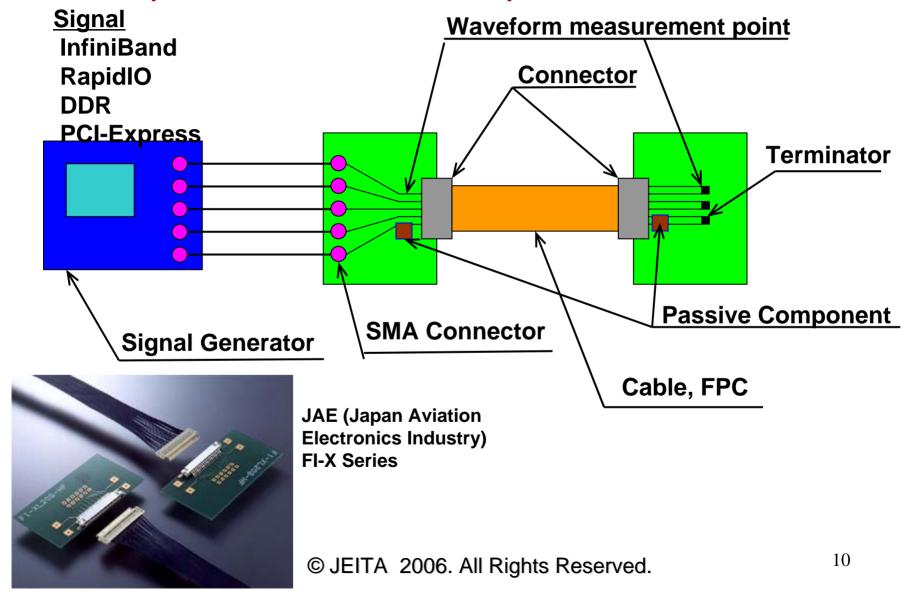

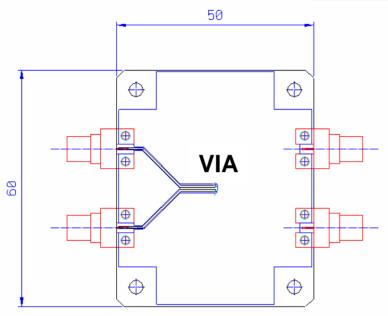

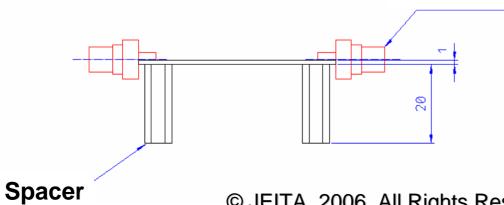

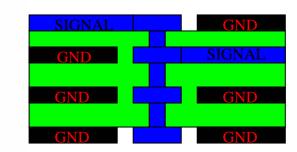

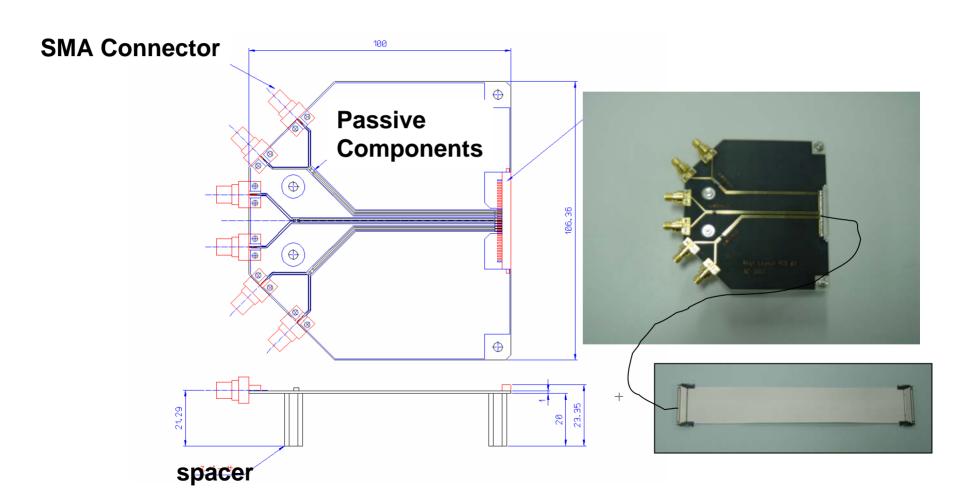

#### 3. Study of Interconnect Model

#### SI Model (Connector, PCB, Cable)

# Study of Interconnect Model for Signal Integrity

- **◆**Target Application; DDR, PCI-Express etc.

- **◆EDA Model; Connectors,**

**Passive Components,**

PCB (Via, Pattern),

LSI

**♦**Simulation Tool; Cadence, etc.

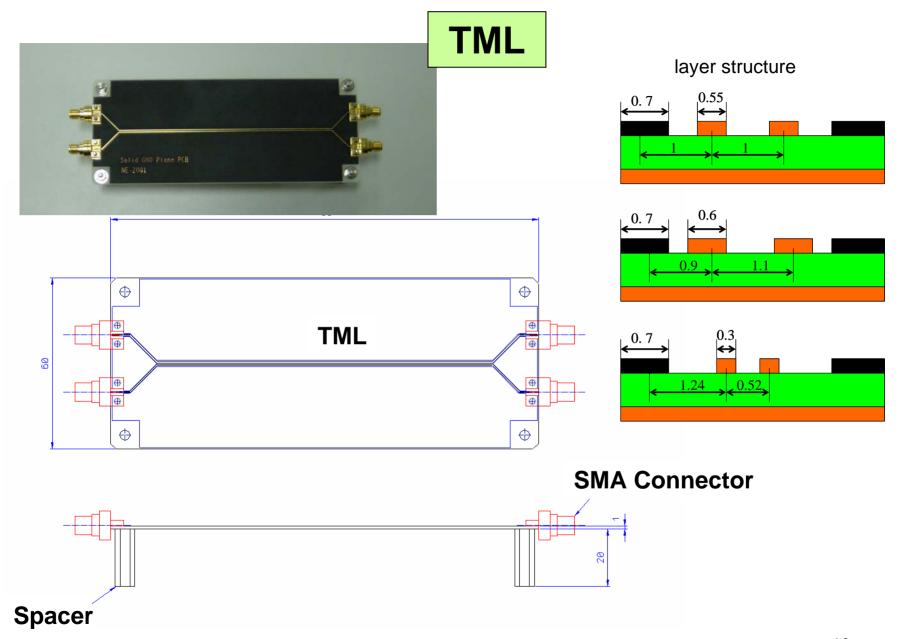

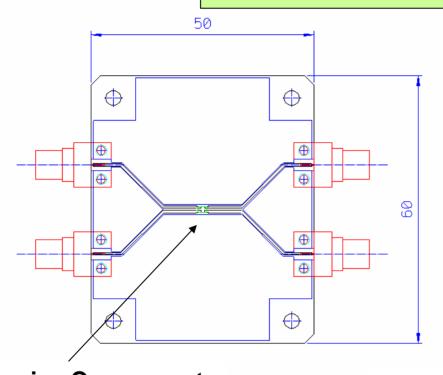

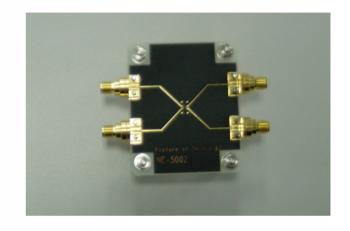

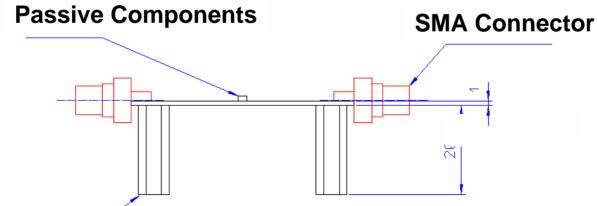

#### **Passive Components**

**Spacer**

#### **SMA Connector**

© JEITA 2006. All Rights Reserved.

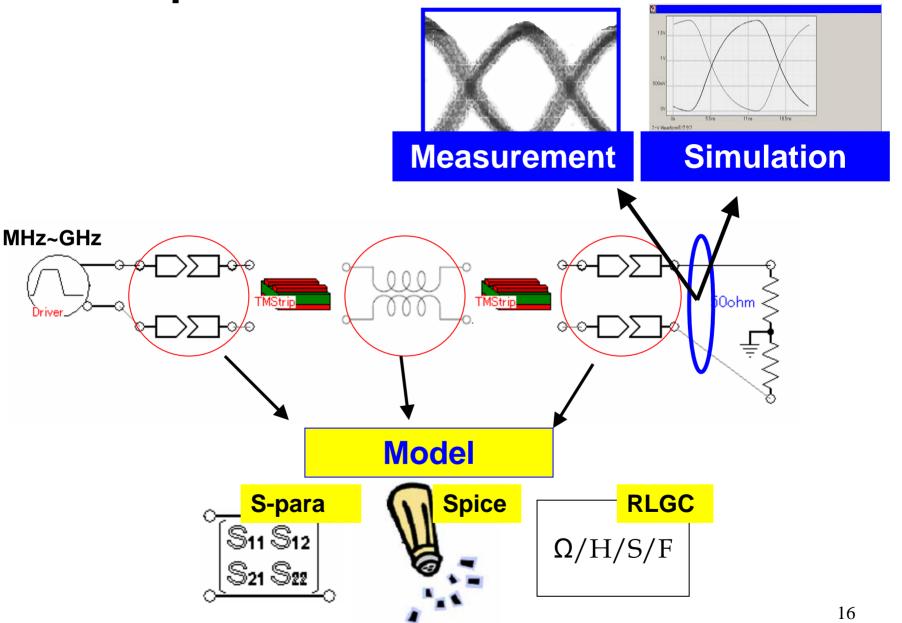

### All Component (TML, Passive Components, VIA, Connector)

#### **Compare Measurement with Simulation**

© JEITA 2006, All Rights Reserved.

# We hope to discuss case study of IBIS with you periodically

## Thank you for all the help EIA/IBIS Committee!