# Hybrid Asian IBIS Summit – Japan, 2024 Discussion Room with IBIS Open Forum

October 22, 2024

**IBIS Open Forum**

**JEITA EDA Model Specialty Committee**

Facilitator: Hayato Ogawa Keysight Technologies Japan K.K. **IBIS Open Forum**

JEITA EDAモデル専門委員会

ファシリテータ: 小川 隼人 キーサイト・テクノロジー株式会社

Theme #1 / テーマ1

About IC package modeling ICパッケージのモデリングについて

#### ■ 要望①

#### Interconnect モデル をマルチポート対応にして欲しい

● 背黒

LPDDR5などパッケージ内で複数のダイに接続するICが存在しているが、Interconnectモデルでは1:1接続のみが想定されており実情に即していない。

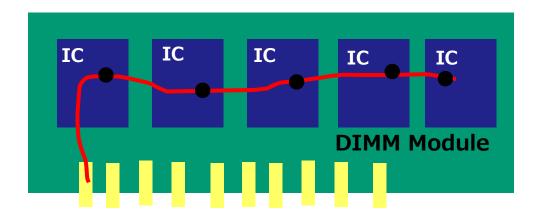

また、EMDモデルは複数接続は可能であるがこのモデルはモジュール基板向けの表現であるためIC内部の記述には適さないと考える。

● 起案者半導体ベンダー、IBISモデルユーザー

#### ■ 要望②

# EMDモデル, Interconnectモデルの用途・使い分けに関する補足が欲しい

● 背黒

2024年現在、日本においては、EMDモデル、Inerconnectモデルの普及が進んでいない。 モデルを提供するデバイスベンダーは、 EMDモデル、Inerconnectモデルの使い分けが分かりにくいことが、要因の一つである。 モデル作成の仕様は、Specificationで定義されているが、その使い方について、補足情報が欲しい。 例えば、次ページのような絵と表。

※当日は、モデル普及に関して、会場からのご意見も募ることを考えています。

起案者 半導体ベンダー

■ Request #1

**Multi-port support for Interconnect Model**

Background

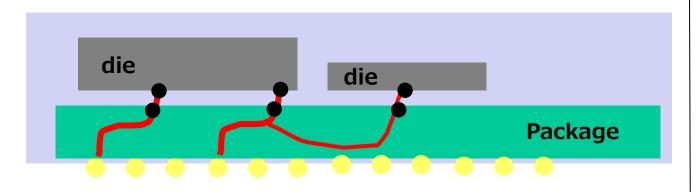

There are ICs such as LPDDR5 that connect to multiple dies within a package, but the Interconnect model only assumes 1:1 connection, which does not suit the actual situation. Also, although multiple connections are possible with EMD model, this model is not suitable for describing the inside of an IC because it is a representation for module boards.

Drafter

Semiconductor device vendor, IBIS Model user

■ Request #2

Providing supplementary information regarding the use of EMD model and Interconnect model

Background

As of 2024, EMD model and Interconnect model haven't become widespread in Japan.

One of the reasons is that it's difficult for device vendors who provide models to differentiate between EMD model and Interconnect model. The specifications for model creation are defined in the Specification, but is it possible for IBIS Open Forum to provide supplementary information on how to use them?

(For example, the illustration and table on the next page.)

\*On the day of the summit, we are considering soliciting opinions from the audience regarding the dissemination of the model.

Drafter

Semiconductor device vendor

# **Interconnect Model for IC package Only?**

# **EMD Model for Module Board Only?**

|            | IC (topology1:1) | IC(topology1:x) | Multi Chip IC | Module Board (DIMM etc.) |

|------------|------------------|-----------------|---------------|--------------------------|

| Inerconnet | 0                | ×               | ×             | ×                        |

| EMD        | 0                | 0               | 0             | 0                        |

#### **■** Comment From IBIS Open Forum

#### From Arpad:

The terminology in IBIS for <u>package</u>, <u>module</u> and <u>board</u> needs to be taken a more flexibly. For example, the term "module" (in EMD) is not strictly limited to a DIMM "memory module". It could also mean a multi-chip module (MCM), sometimes called multi-die memory chip. With EMD models you can also describe a daughter card that is plugged into a motherboard. EMD models can also be nested, e.g., it could be a model of a daughter card that contains a memory module, that contains a multi-die memory chip.

With that in mind, an EMD model could describe the "package" (substrate) of a multi-die chip. This would include the connections found between the EMD pins and die pads (which in this case would be the IBIS [Pin]-s of the IBIS file). In this case, the traditional IBIS package keywords would need to be "zeroed out" inside the .ibs file to effectively turn the IBIS [Pin]-s into pads. If there is a need to model the metal interconnects found between the actual die pads and buffer terminals, the [Interconnect Model] can be used.

We consciously did not add support for forks and joins in the [Interconnect Model] "package" syntax for signal pins because that would have complicated the syntax too much and the same can be achieved by the EMD keywords.

In summary (for slide 2): for multi-chip devices, use the EMD keywords for the non-1:1 "package" modeling (between pins and the die pads), zero out the traditional package keywords in the .ibs file of the buffer models on the die, and use the [Interconnect Model] keyword only if there is a need to describe on-die interconnects between the die pads and buffer terminals.

#### ■ IBISオープンフォーラムからのコメント

#### Arpad氏より

IBISにおけるパッケージ、モジュール、ボードの用語は、もっと柔軟にとらえる必要があります。 例えば、(EMDの)「モジュール」という用語は、厳密にはDIMM「メモリ」に限定されません。厳密にはDIMM「メモリ・モジュール」に限定されません。 マルチチップモジュール(MCM)を意味することもあり、マルチダイメモリチップと呼ばれることもあります。 チップと呼ばれることもあります。

EMDモデルでは、マザーボードに差し込むドーターカードも記述できます。 EMDモデルは入れ子にすることもできます、例えば、マルチダイ・メモリ・チップを搭載したメモリ・モジュールを含むドーター・カードのモデルにすることもできます。 それを念頭に置いて、EMDモデルはマルチダイ・チップの「パッケージ」(基板)を記述することができる。 これにはEMD ピンとダイパッド(この場合、IBISファイルのIBIS [Pin]-sとなる)間の接続も含まれる。 この場合、従来のIBISパッケージのキーワードを.ibsファイル内で「ゼロアウト」し、IBIS [Pin]-sを効果的にパッドに変換する必要があります。 もし実際のダイ・パッドとバッファ端子の間にある金属相互接続をモデル化する必要がある場合は、[Interconnect Model]を使用することができます。

信号ピンの[Interconnect Model]「パッケージ」構文では、フォークと結合のサポートを意識的に追加しませんでした。EMDキーワードでも同じことができるからです。

要約すると:マルチチップデバイスの場合、1:1 以外の「パッケージ」モデリング(ピンとダイパッド間)には EMD キーワードを使用し、ダイ上のバッファモデルの .ibs ファイルでは従来のパッケージキーワードをゼロにし、[Interconnect Model] キーワードを使用します。ダイ上のバッファモデルの.ibsファイルで従来のパッケージキーワードをゼロにし、オンダイ相互接続を記述する必要がある場合にのみ[Interconnect Model]キーワードを使用します。インターコネクトモデル]キーワードは、ダイ・パッドとバッファ端子間のオンダイ・インターコネクトを記述する必要がある場合にのみ使用してください。

#### **■** Additional Questions from Japan

We have one confirmation.

The first request is about "Multi-port support for Interconnect Model".

If possible, we'd like to know the direct answer to this.

Is it correct to understand that there are no plans to support multi-port in [Interconnect Model]?

(There is no need to revise the answer slide. The facilitator will do it well.)

Because there was a participant who said that he heard that there were plans at last year's summit, so we would like to understand the truth once again.

It may be a misunderstanding on that person's part.

#### **■** Comment From IBIS Open Forum

From Randy:

There are no plans to support multi-port in [Interconnect Model].

#### ■ 日本からの追加質問

ひとつ確認があります。最初の要望は「インターコネクトモデルのマルチポート対応」についてです。可能であれば、これに対する直接的な回答を教えていただきたい。インターコネクトモデル]でマルチポートをサポートする予定はないという理解でよろしいでしょうか?。

昨年のサミットで予定があると聞いたという参加者がいたので、今一度真意を把握したい。その方の誤解かもしれない。IBIS オープンフォーラムからのコメント

#### ■ IBISオープンフォーラムからのコメント

#### ランディ氏より

Interconnect Model]でマルチポートをサポートする予定はありません。

Theme #2 / テーマ2

# Definition of quality for IBIS-AMI IBIS-AMIの品質定義

#### ■ 質問

IBIS Quality SpecificationはIBISモデルには定義されているが、IBIS-AMIについてはどのように品質を担保すべきかご意見を伺いたい。

- 背景 お客様にQuality Specification準拠した品質求められているが、AMIに対応していないので困っている。

- 起案者 半導体ベンダー

#### Question

IBIS Quality Specification defines only IBIS models. What is IBIS Open Forum's opinion on how to ensure quality regarding IBIS-AMI?

- Background

Model creators are faced with difficulties because model users are demanding quality that complies with Quality

Specification, but it is not compatible with IBIS-AMI.

- DrafterSemiconductor device vendor

#### **■** Comment From IBIS Open Forum

From Michael:

Some features are being introduced in IBIS 8.0 that can address IBIS Quality requirements.

Note that some basic IBIS AMI checks are enabled by the IBISCHK parser today. These are limited to ensuring that the necessary .ami and algorithmic executable files are present, as well as checking the individual executables (appropriate to the operating system) include the minimum required functions, such as AMI\_Init and AMI\_Close.

BIRD229.1 introduces a new keyword, [AMI Test Configuration], which is intended to enable testing of executable models in AMI format across different EDA simulators. The optional keyword includes defined input and model configuration information, along with expected output, all provided with the model by the model-maker. EDA tools supporting the keyword will therefore be able to automatically check that a given AMI executable generates the expected parameters and waveform output for the input provided with the model.

Note that this does not address generation of channel responses by EDA tools. The new keyword assumes the model-maker provides the channel response directly in a file; the EDA simulation tool does not actually generate it from other model information. Separately, updates are being considered to [Test Load] and [Test Data] to define loads and interconnects using advanced IBIS Interconnect keywords. This will enable checking and correlation of channel characterization by EDA tools.

With the new [AMI Test Configuration] keyword, supporting IQ2 and possibly Designator G IBIS Quality designations for AMI models should be possible. Note that the IBIS Quality specification may need revision to distinguish between IBIS files containing [AMI Test Configuration] and files containing [Test Load]/[Test Data].

#### ■ IBISオープンフォーラムからのコメント

Micael氏より

IBIS 8.0では、IBISの品質要件に対応できるいくつかの機能が導入されます。

現在、IBISCHKパーサーによっていくつかの基本的なIBIS AMIチェックが有効になっています。これらは、必要な.amiファイルとアルゴリズム実行ファイルが存在することを確認することと、(オペレーティングシステムに適した)個々の実行ファイルにAMI\_InitやAMI\_Closeなどの必要最低限の関数が含まれていることを確認することに限られています。

BIRD229.1では、異なるEDAシミュレータ間でAMI形式の実行可能モデルをテストできるようにするための新しいキーワード[AMI Test Configuration]が導入された。このオプションのキーワードには、定義された入力とモデル構成情報、および期待される出力が含まれ、これらはすべてモデル作成者によってモデルと共に提供されます。そのため、このキーワードをサポートするEDAツールは、指定された AMI実行ファイルが、モデルと共に提供された入力に対して期待されるパラメータと波形出力を生成することを自動的にチェックすることができます。

これは、EDA ツールによるチャネル応答の生成には対応しないことに注意。この新しいキーワードは、モデル作成者がチャネル応答を直接ファイルで提供することを想定しており、EDAシミュレーション・ツールは実際には他のモデル情報からチャネル応答を生成しません。これとは別に、高度なIBIS Interconnectキーワードを使用して負荷と相互接続を定義するために、[Test Load]と[Test Data]の更新が検討されている。これにより、EDAツールによるチャネルキャラクタリゼーションのチェックと相関が可能になる。

新しい[AMI Test Configuration]キーワードにより、AMIモデルのIQ2およびDesignator G IBIS Quality指定のサポートが可能になります。AMI Test Configuration]を含むIBISファイルと[Test Load]/[Test Data]を含むファイルを区別するために、IBIS Quality仕様の改訂が必要になる可能性があることに注意してください。

Electronic Commerce ALliance for Global business Activity