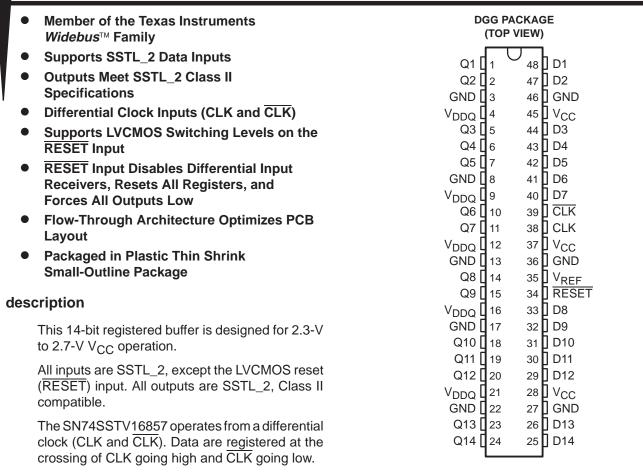

## SN74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL 2 INPUTS AND OUTPUTS

MARCH 16, 2000

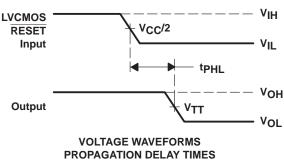

The device supports low-power standby operation. When  $\overline{\text{RESET}}$  is low, the differential input receivers are disabled, and undriven (floating) data, clock, and reference voltage ( $V_{\text{REF}}$ ) inputs are allowed. In addition, when  $\overline{\text{RESET}}$  is low all registers are reset, and all outputs are forced low. The LVCMOS  $\overline{\text{RESET}}$  input must always be held at a valid logic high or low level.

To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the low state during power up.

The SN74SSTV16857 is characterized for operation from 0°C to 70°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus is a trademark of Texas Instruments Incorporated.

# **DESIGN GOAL**

### **INPUTS** OUTPUT **CLK** CLK D Q Н Н

### RESET Н $\uparrow$ Н $\downarrow$ L L Н L or H L or H Χ $Q_0$ X or X or X or L floating floating floating

**FUNCTION TABLE**

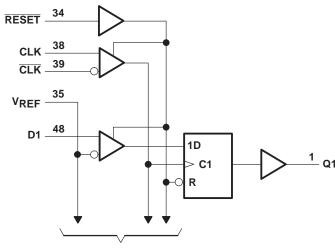

### logic diagram (positive logic)

To 13 Other Channels

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> or V <sub>DDQ</sub>                   | 0.5 V to 3.6 V                               |

|-----------------------------------------------------------------------------|----------------------------------------------|

| Input voltage range, V <sub>I</sub> (see Notes 1 and 2)                     | $-0.5 \text{ V}$ to $V_{CC} + 0.5 \text{ V}$ |

| Output voltage range, V <sub>O</sub> (see Notes 1 and 2)                    | $-0.5 \text{ V to V}_{DDQ} + 0.5 \text{ V}$  |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ )                                 | —50 mA                                       |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{DDO}$ )             | ±50 mA                                       |

| Continuous output current, $I_O$ ( $V_O = 0$ to $V_{DDQ}$ )                 | ±50 mA                                       |

| Continuous current through each V <sub>CC</sub> , V <sub>DDQ</sub> , or GND | ±100 mA                                      |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3)                     | 70°C/W                                       |

| Storage temperature range, T <sub>stq</sub>                                 | –65°C to 150°C                               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. This value is limited to 3.6 V maximum.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

# **DESIGN GOAL**

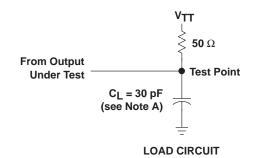

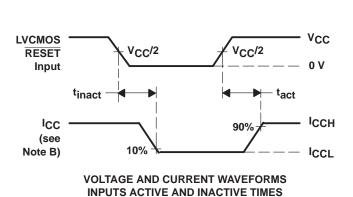

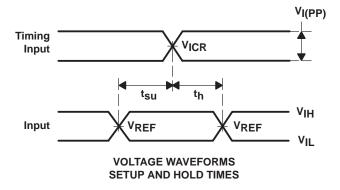

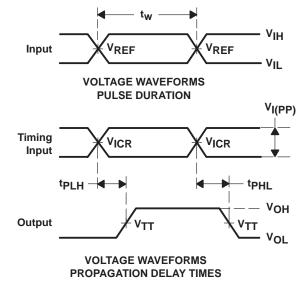

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B.  $I_{CC}$  tested with clock and data inputs held at  $V_{CC}$  or GND, and  $I_{O}$  = 0 mA.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , input slew rate = 1 V/ns  $\pm$ 20% (unless otherwise noted).

- D. The outputs are measured one at a time with one transition per measurement.

- E.  $VTT = V_{REF} = V_{DDQ}/2$

- F.  $V_{IH} = V_{REF} + 310 \text{ mV}$  (ac voltage levels) for differential inputs.  $V_{IH} = V_{CC}$  for LVCMOS input.

- G. VIL = VREF 310 mV (ac voltage levels) for differential inputs. VIL = GND for LVCMOS input.

- H. tpLH and tpHL are the same as tpd.

Figure 1. Load Circuit and Voltage Waveforms